“устройство для исправления ошибок в системах передачи дискретной информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 663120

Авторы: Насыпный, Осмоловский

Текст

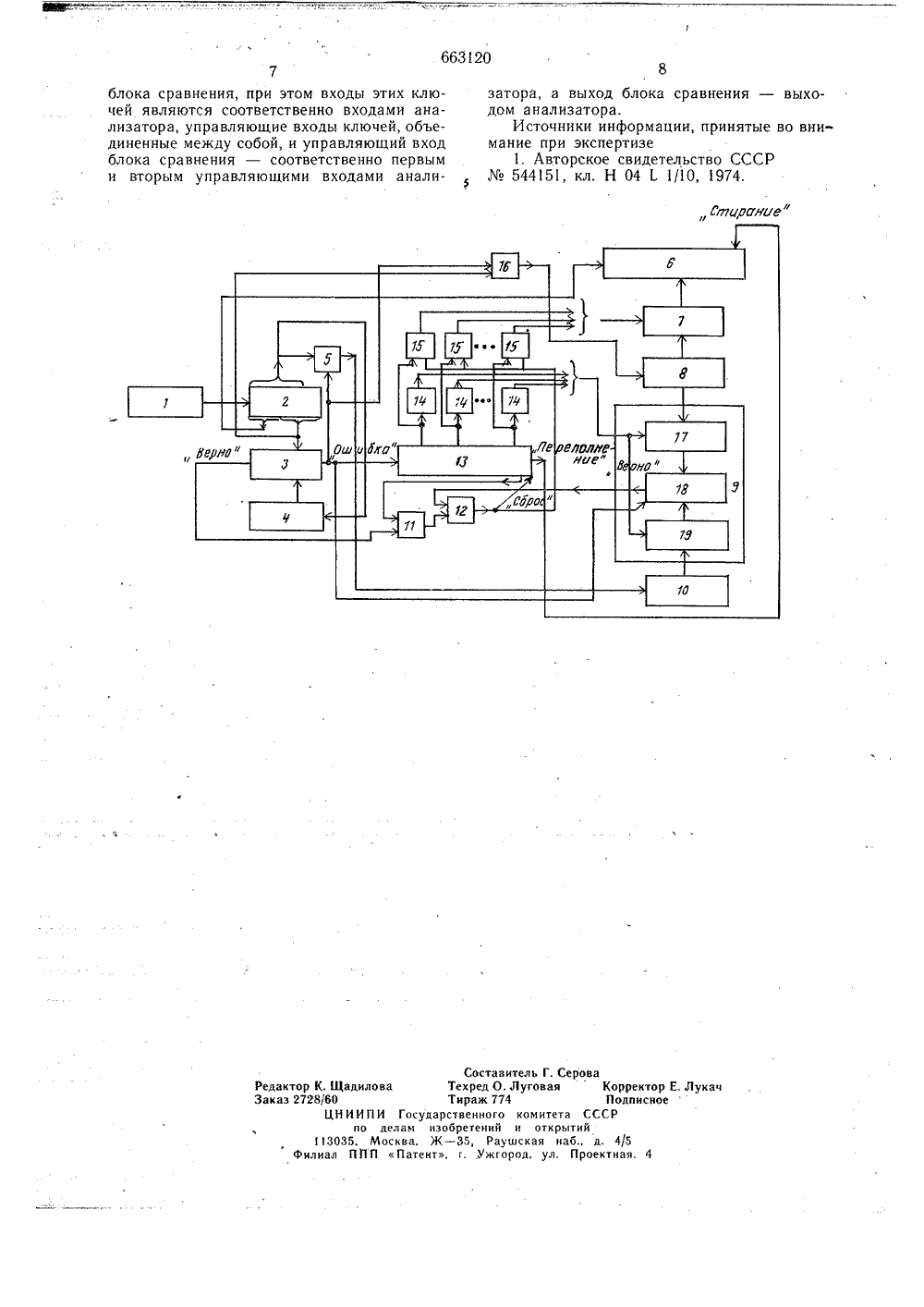

ОП ИСАНИЕ ИЗОБРЕТЕН Ия К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ . Союз СоветскихСоциалмстяческихРеспубпнк цб 63120 61) Дополнительное к авт. свид-ву -22) Заявлено 04.03.77 (21) 2461681/18-0 1) М. Кл.2 Н 04 1. 1/10 явки-с п исоединением Приоритет -Опубликова еударатвеииый комитет СССР по делам изабретеиий и еткрытийкой, и блок элементов И, при этом выход ошибка блока сравнения подключен к входам анализатооа непосредственно, через последовательно соединенные регистр ошибок и блок элементов НЕ, через последовательно соединенные элемент запрета, к другому входу которого подключен эталонный выход первого регистра памяти, и регистр правильно принятого блока и через последовательно соединенные первый элемент И, к другому входу которого подключен проверочный выход первого регистра памяти, и регистр блока, принятого с ошибкой, другой выход которого подключен к входу ключа, к управляющему входу которого подключены через блок элементов И выходы регистра ошибок, соответствующий выход которого через последовательно соединенные второй элемент И, к другому входу которого подключен выход верно блока сравнения, и элемент ИЛИ подключен к другимвходам блока элеметов И и к входу сброс регистра ошибок, 20 выход переполнение которого подключенк входу стирание накопителя, к другому входу которого подключен соответствующий выход первого регистра памяти, эталонный выход которого через второй регистр памяти Для ошибокформац диненнь дн ход ключключен квторой рвведенырегистр отого бло Изобретение относится к радиотехнике.Известно устройство для исправления ошибок в системах передачи дискретной информации, содержащее последовательно соединенные декодер, первый регистр памяти и блок сравнения, а также накопитель, к одному из входов которого подключен выход ключа, анализатор, выход которого подключен к одному из входов элемента ИЛИ, второй регистр памяти и блок элементов НЕ 111,Однако известное устройство характеризуется недостаточной помехоустойчивостью.Цель изобретения - повышение помехоустойчивостии. этого в устроиство для исправления в системах передачи дискретной инин, содержащее последовательно соее декодер, первый регистр памяти сравнения, а также накопитель, к из входов которого подключен выа, анализатор, выход которого пододному из входов элемента ИЛИ, егистр памяти и блок элементов НЕ, элемент запрета, два элемента И, шибок, регистр правильного приняка, оегистр блока, принятого с ошибАВЛЕНИЯ ОШИБОК РЕДАЧИОРМАЦИИЭ 663120подключен к другому входу блока сравнения, М разрядов, записывается 1 и сла анализатор выполнен в вииде двух ключеи,тельно, число единиц, записанных в егистввыходы которых подключены к входам блока ошибок 13 становитсясравнения п и этр этом входыэтих-ключей яв-подряд обнаруженных ошибок в п инятыхляются соответственно входами анализатора кодо б рвых локах; запрещается запись череззапрета декодированного с обнауправляющие входы ключей, объединенные элемент зап ета 5с авнения -между собой, и управляющий вход блока руженнойошибкойблокаврегистр 10р - соответственно первым ивто- него правильно принятого блокбтр последым п аво лока, что обеса выхо блр у р ляющими входами анализатора, печивает сохранение в нем со бо щении последзатора.д лока сравнения - выходом анали- него блока, декодированног б б- о ез о наруженной ошибки; в регистр 8 блока с ошибкойНа чертеже дана структурная электри в записываются символы сообческая сх ема предлагаемого устроиства.дящих в состав проверочной комбинацииоУстройство содержит декодер 1, первый декодированного блока; в блоке сравнениярегистр памяти 2, блок сравнения 3, второй 18 после записи инфо ма ир р ти , элемент запрета 5, како- блока с ошибкой происходит сравегист памяти 4 эпитель 6 кл 7дит сравнение симюч 7, регистр 8 блока, принято- волов одноименных сообщени"нии, записанныхши кой, анализатор 9, регистр О в регистр 10 последнего правильно приняправильно принятого блока, элемент И 11 того блока и Ррегистр лока с ошибкой.8 бэлемент ИЛИ 12, регистр ошибок 13, блокэлементов НЕ 14, блок элементов И 15 и . ВыбоР одноименных сообщений из Укаэлемент И 16. Анализатор 9 содержит ключ занных РегистРов 8 и 10 длЯ подачи на блок17 , блок сравнения 18 и ключ 19.2 О сравнения 18 анализатора 9 осуществляетсяУстройство работает следующим обра посРедством ключей 17 и 19, управляемыхзом, --" -:с помощью регистра ошибок 13 и блока элеПринятый очередной кодовый блок после -ме"тов НЕ 14декодированйя" ггоступает в первый регистрпамяти 2, откуда его информационные сЛопустим, что декодирован кодовый блокволы записываются в накопитель 6 приема+ при условии, что в канале искаженв котором хранятся информационные к . оько -1+1 блок. При сравнении провебинации М ранее принятые кодовых б рочной комбинации принятого кодового блоков, а проверочные подаются на б ка с эталоном, образованным из сообщенийнения 3, на второй вход которого из второго лока+, ошибка в нем обнаружитсяРеистра памяти 4 поступают символы ком- за счет искажения эталона. В этом случаебинаций предыдущего блока, используе е в Регистр 8 блока с ошибкой будут занесев качестве эталона, После сравнения сооб- ны символы проверочной комбинации блощения, входящие в состав принятого б, ка 1-1+2, а в регистре ошибок 13, выходылока,символы которых будут использоваться как- разрядов которого, начиная со второгоэталон для последующего кодового блока параллельно соединены с входами блока элезаписываются во второй регистр памяти 4 з ментов НЕ 14 и блока элементов И 15 буи в случае правильного приема блока (сов- Лет записана комбинация 1100. В регистрепадения сравниваемых символов) через э, . 0 последнего правильно принятого блока10мент запрета 5, на запрещающий вход ко о находятся соответствующие сообщения блоРого с Выхода ошибка блошка срав 3 ка . Колчево разрядов Регистра ошбок 13сигнал не подается, поступает такт также в ре е екок, в которых записаны нули послера виль ор бе ко,ироваиЯочереоо коовооблокаопределяют число одноименных сообщений,находящихся в регистрах 10, 8 правильнопринятого блока и блока с ошибкои, кото ь приема, удет выдана рые необхо имо выпотребителю после приема последующихрд выдать на блок сравнениякодовых блоков, 4игналами, подаваемыми с выходов бло 18, Сигка элементов НЕ 14 через ключи 17 и 19на блок сравнения 18 с регистров 8 и 10 бло ри о наружении ошибки в принятом ка с ошибкой и п авил нюдам блоке если количество под яд б-во подряд - символы одноименных сообщений выдаютсяруженных оши ок в предыдущих кодовых на блок сравнения 18.блоках не превышает числа М сообщений, юевходящих в состав блока п инение о нро зводится срав- При совпадении сравниваемыдХ СИМВОЛОВнд оименных сообщении декодирован- что и произойдеого и последнего правильно принятогобло- кч блок 11+2т в данном случае, посколька. Вк с в канале не искажен, с.вы лока сравнения 18 сигнала. этом случае с выхода ошибка бло- "хода верно бий вка сравнения 3 снимается сигнал, поступаю- через элемент И г 1 И 12т , поступит на вторые5 на то о"щ " регистр ошибок 13, элемент запрета . входы элементов И блв лока элементов И 15,, на второй вход элемента И 16 и на уп- на первые входы которыхавляющий вхоых подаются сигнакото ом вр " х д блока сравнения 18, по лы с выходов разрядов ре б 13,р у в регистр ошибок 13, содержащий Количество разрядов, начиная со второго,эрегистра ошибок 13, в которые записаны 1 определяют количество предыдущих кодовых блоков, информационные сообщения которых необходимо исправить. В рассматриваемом примере 1 со второго разряда регистра ошибок 13 поступит на первый вход первого элемента И блока элементов И 15 сигнал, с выхода которого обеспечится запись через ключ 7 символов информационного блока Б 1, + 1 из регистра 8 блока с ошибкой, в котором хранятся сообщения, в данном случае не искаженного блока Ы + 2, в накопитель 6 приема вместо находящейся там информационной комбинации кодового блока 1.1 + 1, таким образом происходит исправление искаженных информационных комбинаций. Сигналом с выхода верно блока сравнения 18, поступающим на вход сброс регистра ошибок 13, осуществляется стирание записанной в него комбинации,Если число подряд обнаруженных ошибок в кодовых блоках равно М (в этом случае в регистре ошибок 13 записаны од ни 1), а последующий М+1-ый блок декодирован без обнаруженной ошибки, то за счет проверочной комбинации последне. го блока принятого с ошибкой, которыйв этом случае в канале не искажен, произойдет исправление информационных сообщений предыдущих Мкодовых блоков.При этом сигнал ошибка с выхода блока сравнения 3 не поступает и, следовательно, записи принятого блока в регистр 8 с ошибкой, в котором находится предыдущий блок, последний из числа декодированных с обнаруженной ошибкой, не будет, не произойдет также и записи 1 в регистр ошибок 13. Сообщения декодированного блэка будут записаны в регистр 10 правильно принятого блока,Сигнал верно с блока сравнения 3 через элемент И 11, на второй вход которого подано отпирающее напряжение с выхода, М-го разряда" регистра ошибок 13, элемент ИЛИ 12 поступит на вторые входы элементов И блока элементов И 15, на первые входы которых подано отпирающее напряжение с заполненного единицами регистра ошибок 13, в этом случае сигналы с выхода элементов И блока элементов И 15 через ключи 7 произведут запись Мсообщений последнего декодированного с обнаруженной ошибкой блока, находящегося в регистре 8 блока с ошибкой, в накопитель 6 приема, вместо находящихся там комбинаций Мпредыдущих блоков. Сигналом, поступившим на вход сброс регистра ошибок 13, производится стирание записанной в него комбинации. Если же при уСловии, что число подряд обнаруЖенных ошйбок равно М, последующий М+ 1-ый блок декодирован с ошибкой, то в регистр - ошибок 13 сигналом с выхода ошибкаблока сравнения 3 будетзаписана 1. Тогда сигнал с выхода переполнение регист%1 О 6ра ошибок 13 поступит на вход стирание накопителя 6 приема и произойдет стирание первого из числа М блоков, декодированных с обнаруженной ошибкой, после чего прием продолжается. Регистр ошибок 13 в этом случае не сбрасывается и если последующий кодовый блок будет декодирован без ошибки, то за счет проверочной комбинации предыдущего блока, описанным выше образом, произойдет исправление сообщений информационно связанных с ним Мблоков. Если же последующий блок будет также декодирован с ошибкой, то произойдет стирание из накопителя 6 приема информационной комбинации, следующей за стертой ранее. 1Формула изобретения1. Устройство для исправления ошибокв системах передачи дискретной информации, содержащее последовательно соединенные декодер, первый регистр памяти и блок сравнения, а также накопитель, к одному из входов которого подключен выход ключа, анализатор, выход которого подключен к одному из входов элемента ИЛИ, второй ре 2 ю гистр памяти и блок элементов НЕ, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены элемент запрета, два элемента И, регистр ошибок, регистр правильно принятого блока, регистр блока, принятого с ошибкой, и блок элементов И, при этом выход ошибка блока сравнения подключен к входам анализатора непосредственно, через последовательно соединенные регистр ошибок и блок элементов НЕ, через последовательно соединенные элемент запрета, к другому входу которого подключен эталонный выход первого регистра памяти, и регистр правильно принятого блока и через последовательно соединенные первый элемент И, к другому входу которого подключен проверочный выход первого ре 4 ф гистра памяти, и регистр блока, принятогос ошибкой, другой выход которого подключен к входу ключа, к управляющему входу которого подключены через блок элементов И выходы регистра ошибок, соответствующий выход которого через последовательно соединенные второй элемент И, к другому входу которого подключен выход верно блока сравнения, и элемент ИЛИ подключен к другим входам блока элементов И и к входу сброс регистра ошибок, выход пе реполнение которого подключен к входустирание накопителя, к другому входу которого подключен соответствующий выход первого регистра памяти, эталонный выход которого через второй регистр памяти подключен к другому ходу блока сравнения.2. Устройство по п.1, отличающееся тем,что анализатор выполнен в виде двух ключей, выходы которых подключены к входам663120 бтграюиеф едактор К. Щадилов аказ 2728/60 ач бд. 4/5 Проектная,фили блока сравнения, при этом входы этих ключей являются соответственно входами анализатора, управляющие входы ключей, объединенные между собой, и управляющий вход блока сравнения - соответственно первым и вторым управляющими входами аналиН И И П И Государ по делам из 035, Москва, Ж л ППП Патентзатора, а выход блока сравнения - выходом анализатора.Источники информации, принятые во внимание при экспертизе1. Авторское свидетельство СССР544151, кл. Н 04 1. 1/10, 1974. Составитель Г. Сехред О. Луговаяираж 774твенного комитетаретений и открь35, Раушская наг.,Ужгород, ул. ероваКорректор Е, ЛПодписноеСССРтий

СмотретьЗаявка

2461681, 04.03.1977

ОСМОЛОВСКИЙ СТАНИСЛАВ АНТОНОВИЧ, НАСЫПНЫЙ ВЛАДИМИР ВЛАДИМИРОВИЧ

МПК / Метки

МПК: H03M 13/05

Метки: дискретной, информации, исправления, ошибок, передачи, системах

Опубликовано: 15.05.1979

Код ссылки

<a href="https://patents.su/4-663120-ustrojjstvo-dlya-ispravleniya-oshibok-v-sistemakh-peredachi-diskretnojj-informacii.html" target="_blank" rel="follow" title="База патентов СССР">“устройство для исправления ошибок в системах передачи дискретной информации</a>

Предыдущий патент: Система связи с шумоподобными сигналами

Следующий патент: Устройство тактовой синхронизации и выделения сигналов широкополосной системы радиосвязи

Случайный патент: Исполнительный орган горной машины