Регенератор приемника стартстопных телеграфных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 641671

Авторы: Артемьев, Чернобыльский

Текст

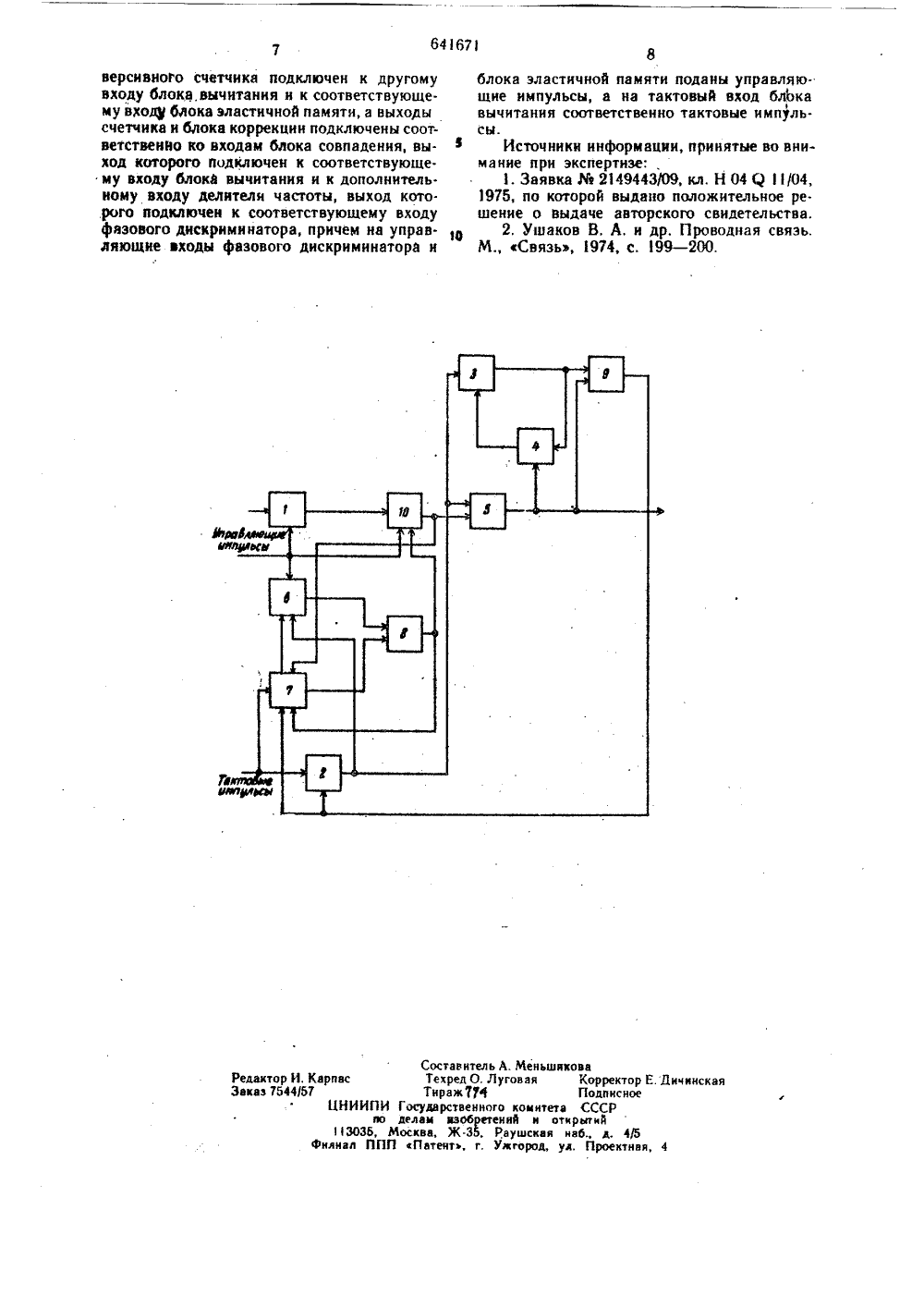

и 641671 Ссиоз СоветскихСоциалистическихРеспублик 6) Дополнительное к авт. с 22) Заявлено 14. 10.76 Ф) 2 М. Кл,Н 04 Х 25 исоединен аявкидарственный квинтет ссср делам неебретеннй н етнрытнйртемьев и Б. М. Ч льнский Заявитель 4) РЕГЕНЕРАТОР ПРИЕМНИКА СТАРТСТОПНЫХ ТЕЛЕГРАФНЫХ СИГНАЛОВ Изобретение отчосится к радиотехнике нможет быть использовано в системах передачи дискретных сигналов.Одним из известных стартстопных регенераторов, используемых для регенерации поформе и длительности посылок стартстопнойтелеграфной комбинации, является регенератор, содержащий входной, исправляющийи выходной узлы, а также управляемый делитель частоты и счетную схему со спусковым реле для управления упомянутым дели- тотелем 1.Однако известный регенератор нельзя использовать в приемниках стартстопно-синхронных систем для коррекции длительностистоповых посылок,Наиболее близким техническим решениемк предлагаемому устройству является регенератор приемника стартстопных телеграфных сигналов, содержащий формировательвходных сигналов, на управляющий вход которого поданы управляющие импульсы, ипоследовательно соединенные делитель частоты, на управляющий вход которого поданытактовые импульсы, счетчик и спусковое реле,к другому входу которого подключен выход блока коррекции, причем выход спускового реле подключен к другому входу счетчика, а выход делителя частоты подключен к тактовому входу блока коррекции 2.Однако и этот регенератор невозможно применять в приемниках стартстопно-синхронных систем для коррекции длительности стоповых посылок из-за низкой помехоустои. чивости. Цель изобретения - повышение помехо. устойчивости путем регенерации стоповой посылки телеграфных сигналов.Для этого в регеиератор приемника стартстопных телеграфных сигналов, содержащий формирователь входных сигналов, иа управ. ваяющий вход которого поданы управляющие импульсы, и последовательно соединенные делитель частоты, на управляющий вход которого поданы тактовые импульсы, счетчик и спусковое реле, к другому входу которого подключен выход блока коррекции, причем выход спускового реле подключен к другому входу счетчика, а выход делителя частоты подключен к тактовому входу блока коррекции, введены фазовый дискриминатор, блоквычитания, реверсивный счетчик, блок совпадения и блок эластичной памяти.Между выходом формирователя входных сигналов и информационным входом блока коррекции включен блок эластичной памяти, выход которого через блок вычитания подключен ко входу фазового дискриминатора и к вычитающему входу реверсивного счетчика. К суммирующему входу счетчика подключен выход фазового дискриминатора, выход реверсивного счетчика подключен к другому входу блока вычитания и к соответствующему входу блока эластичной памяти, а выходы счетчика и блока коррекции подключены соответственно ко входам блока совпадения, выход которого подключен к соот ветствующему входу блока вычитания и к дополнительному входу делителя частоты, Выход делителя частоты подключен к соответствующему входу фазового диск ри ми и а- тора, причем ца управляющие входы фазового дискриминатора и блока эластичной памяти поданы управляющие импульсы, а ца тактовый вход блока вычитания соответственно тактовые импульсы.На чертеже приведена структурная электрцческаг схема предложенного регеце ратора.Регенератор приемника стартстопцых телеграфных сигналов содержит формирователь входных сигналов 1, на управляющий вход которого поданы управляющие импульсы, и последовательно соединенные делитель частоты 2, ца управляющий вход которого поданы тактовые импульсы, счетчик 3 и спусковое реле 4, к другому входу которого под. ключец выход блока коррекции 5. Выход спускового реле 4 подключен к другому вхо- з ду счетчика 3, а выход делителя частоты 2 подключен к тактовому входу блока коррекции 5.Регецератор также содержит фазовый дискриминатор 6, блок вычитания 7, реверсивный счетчик 8, блок совпадения 9 и блок4 С эластичной памяти 10. Между выходом формирователя входных си 1 палов 1 ц информационным входом блока коррекции 5 включен блок эластичной памяти 10, выход которого через. блок вычитания 7 подключен ко входу фазового дискриминатора 6 и к вычитающему входу реверсивного счетчика 8.К суммирующему входу счетчика 8 подключен выход фазового дискримйцатора 6, выход реверсивного счетчика 8 подключен к другому входу блока вычитания 7 и к соответствующему входу блока эластичной памяти 10, Выходы счетчика 3 и блока коррекции 5 подключены соответственно ко входам блока совпадения 9, выход которого подключен к соответствующему входу блока вычитания 7 и к дополнительному входу делителя частоты 2. Выход последнего подключен к соответствующему входу фазового дискриминатора б, причем на управляющие входы фазового дискриминатора 6 и блока эластичной памяти 10 поданы управляющие импульсы, а на тактовый вход блока вычитания 7 со. ответственно тактовые импульсы.Регецератор работает следующим образом,В стоповом положении регенератора счет. чик 3 заблокирован в нулевом состоянии управляющим сигналом с выхода спускового реле 4, которое находится в стоповом положении. Кроме того, реверсивный счетчик 8 находится в нулевом состоянии, а управляемый делитель частоты 2 делит частоту вход. ных тактовых импульсов в К раз так, чтобы период следования выходных тактовых импульсов был равен длительности элементарной посылки р.В формирователе входных сигналов 1 с помощью управляющих импульсов из группового многоканального сигнала импульсной стартстопно-синхронной системы выделяется сигнал данного канала и с помощью этих же управляющих импульсов, период следовация которых( го, записывается в блок эластичной памяти 10. С выхода блока 1 О сигнал с помощью блока коррекции 5 считывается в моменты прихода тактовых импульсов на вход этого блока благодаря чему осуществляется коррекция длительнос. ти посылок принимаемого сигнала,Коррекция длительности стоповой посылки осуществляется при помощи счетчика 3, спускового реле 4, блока совпадения 9 и управляемого делителя частоты 2. В момент считывания в блоке коррекции 5 стартовой )осылкн срабатывает спусковое реле 4 и разрешает работу счетчика 3, подсчитывающего количество считывающих (выходцых тактовых) импульсов, начиная с первой (стартовой) посылки в стартстопной комбинации. После подсчета числа импульсов, равного минимальному числу посылок в стартстопной комбинации, на выходе счетчика 3 появляется сигнал, подаваемый на вход блока совпадения 9. Если ца другой вход блока совпадения 9 в этот момент с выхода блока коррекции 5 поступает столовая полярность, то с выхода блока совпадения 9 подается сигнал на управляющий вход управляемого делителя частоты 2 и увеличивает его коэффициент деления частоты до величины 1.)К так, чтобы следующий считывающий ( выходной тактовый), импульс был выработан через интервал т, со, Затем коэффици-, ент деления частоты управляемого делителя частоты 2 возвращается к прежнему значению К, что обеспечивает удлинение стоповой посылки на Ьт =ц - те Величина 1 выбирается таким образом, чтобы длительность стартстопного цикла на выходе регенератора не превышала минимально допустимую длительность стартстопного цикла на входе стартстопно-синхронной системы.Выходной сигнал счетчика 3 одновременно с поступлением на вход блока совпа.дсния 9 поступает также на другой вход спускового реле 4 и возвращает его в стоповое положение, что приводит к сбросу счетчика 3 в нулевое состояние и его блокировке, С момента считывания следующей стартовой посылки в блоке коррекции 5 описанный выше процесс в спусковомреле 4, счетчике 3, блоке совпадения 9 и делителе напряжения 2 повторяется.Поскольку средний период следования импульсов считывания всегда больше периода следования импульсов записи (управляющих импульсов), возникает задача согласования скоростей записи и считывания. Эта задача решается с помощью блока эластичной памяти 10, фазового дискриминатора 6, блока вычитания 7 и реверсивного счетчика В. Блок эластичной памяти О содержит накопитель из последовательно соединенных ячеек памяти ча один бит каждая, например сдвнго. вый регистр, дешифратор состояний реверсивного счетчика 8 и переключатель выхо. дов ячеек памяти. В исходном состоянии, когда реверсивный счетчик 8 находится в нулевом состоянии, переключатель выходов ячеек памяти накопителя подключает к выходу блока эластичной памяти 10 вход первой (выход нулевой) ячейки памяти накопителя.В процессе работы регенератора фазовый дискриминатор 6 сравнивает моменты прихода импульсов записи и считывания. Если в промежутке между 1-м и (+1)-м импульсом записи на тактовый вход фазового дискриминатора 6 не поступит импульс считывания, на его выходе в момент прихода на управляющий вход (+ )-го импульса записи вырабатывается суммирующий импульс, подаваемый на суммирующий вход реверсивного счетчика 8. В результате число, записанное в этом счетчике, увеличится на единицу, к выходу блока эластичной памяти 1 О вместо выхода К-й ячейки памяти накопителя подключится выход (К+1) й ячейки памяти, Благодаря этому на информационном входе блока коррекции 5, несмотря на продвижение принимаемого сигнала на одну посылку в блоке эластичной памяти 10, сохранится значение подлежащей очередному считыванию посылки, что обеспечивает считывание принимаемого сигнала без потерь посылок.Компенсация задержки принимаемого сигнала, накапливаемая в результате описанного выше процесса в блоке эластичной памяти 10, происходит в том случае, когда в принимаемом сигнале содержится две и более стоповых посылок. Происходит это следующим образом. В момент регистрации в блоке коррекции 5 стоповой посылки выход. ной сигнал блока совпадения 9 подается на управляющии вход блока вычитания У и переводит его из исходного состояния в рабочее, в котором разрешается прохождение вход тор приемника импульсной стартстопно.син. хронной системы Обеспечивает формнрова ние удлиненных стоповых посылок, длитель. нОсть которых 60 лю длительности элементар" ной слки, что приводит и поышеию помехоустойчивости приема стгртстопных ком. бинаций. Формула изобретения 35 Регенератор приемника стартстопных те. леграфных сигналов, содержащий формиро. Ватель Входных сигналовна управляющий вход которого поданы управляющие импуль. сы, и последовательно соединенные делитель частоты, на управляющий вход которого поданы тактовые импульсы, счетчик и спусковое реле, к другому Входу которого подклю. чен выход блока коррекции, причем выход спускового реле подключен к другому входу счетчика, а Выход делителя частоты подключен к тактовому Входу блока коррекции, отличающийся тем, что, с целью повышения помехоустойчивости путем регенерации стоповой посылки телеграфных сигналов, введены фазовый дискриминатор, блок вычита. ння, реверсивный счетчик, блок совпадения Й блок эластичной памяти, при этом между выходом формирователя входных сигналов и информационным входом блока коррекции включен блок эластичной памяти, выход которого через блок вычитания подключен ко входу фазового дискриминатора н к вычитающему входу реверсивного счетчика, к суммирующему входу которого подключен выход фазового дискриминатора, Выход ре 45 50 55 ных тактовых импульсов на вычитающий вход реверсивного счетчика Я. В результате число, записанное в этом счетчике, начинает уменьшаться., стремясь к нулю. Процесс вы читанняпродолжается до выполнения одно.го из двух условнй: ревсрснвный счетчик 8 находится в нулевом состоянии нлн на информационный вход блока Вычитания 7 с выхода блока эластичной памяти 10 поступи.ла стартовая полярность.В первом случае блок Вычитания У остается В рабочем состоянии, но Вычитзющие импульсы блокируются на выходе. блока вычитания 7 сигналом блокировка, приходящим с выхода реверсивного счетчика 8 5 в случае его нулеВОГО состояния на блоки.ровочный вход блока Вычитания 7.Во втором случае блок вычитания У сбрасыВается В исходное состояние, и Вследствие этОГО прскрзщается процесс Вычитания. В момент сброса блок вычитания 7 нч управ.ляющем выходе вырабатывает короткий уп.равляющий импульс, который, поступая на второй управляющий вход фазового дискриминатора 6, оказывает на последний такое же воздействие, как и любой импульс счи. )5 тывания,Таким образом, предлагаемый регенера646 А. Менвш говая Состав ител ьТехред О. ЛуТираж 73 Чдарственного комитет и изобретениЮ и о а, Ж.З 5, Раушская тент. г. Ужгород,иковаКорректор ЕПодписноеа СССРткрытиЮиаб., д. 4/5ул, Проектная,едактор И, аказ 7544/5 чииска 1 ИИИПИ осу по дела 1 ЗОЗЬ, Моски янал ППП Паверсивиого счетчика подключен к другому входу блока,вычитания н к соответствующему входф блока эластичной памяти, а выходы счетчика и блока коррекции подключены соответственйо ко входам блока совпадения, выход которого подключен к соответствующему входу блока вычитания и к дополннтель. ному входу делители частоты, выход кото.рого подключен к соответствующему входу фазового дискриминатора, причем на управ. ляющие входы фазового дискриминатора н блока эластичной памяти поданы управляю"щие импульсы, а на тактовый вход блока1вычитания соответственно тактовые импульсы.з Источники информации, принятые во внимание при экспертизе:,1, Заявка РЙ 2149443 Ю 9, кл. Н 04 Я/04,1975 по которой выдано положительное ре.шение о выдаче авторского свидетельства.2. Ушаков В. А, и др. Проводная связь.М., Связь, 1974, с, 99 - 200.

СмотретьЗаявка

2412137, 14.10.1976

ПРЕДПРИЯТИЕ ПЯ А-1221

АРТЕМЬЕВ ВЛАДИМИР ГРИГОРЬЕВИЧ, ЧЕРНОБЫЛЬСКИЙ БЕНЦИОН МОРДКОВИЧ

МПК / Метки

МПК: H04L 25/64

Метки: приемника, регенератор, сигналов, стартстопных, телеграфных

Опубликовано: 05.01.1979

Код ссылки

<a href="https://patents.su/4-641671-regenerator-priemnika-startstopnykh-telegrafnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Регенератор приемника стартстопных телеграфных сигналов</a>

Предыдущий патент: Устройство синхронизации по циклам

Следующий патент: Устройство цифровой передачи и приема телефонных сигналов

Случайный патент: Способ ультразвукового контроля качества листовых изделий