Запоминающее устройство с исправлением ошибок при считывании информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 607281

Автор: Култыгин

Текст

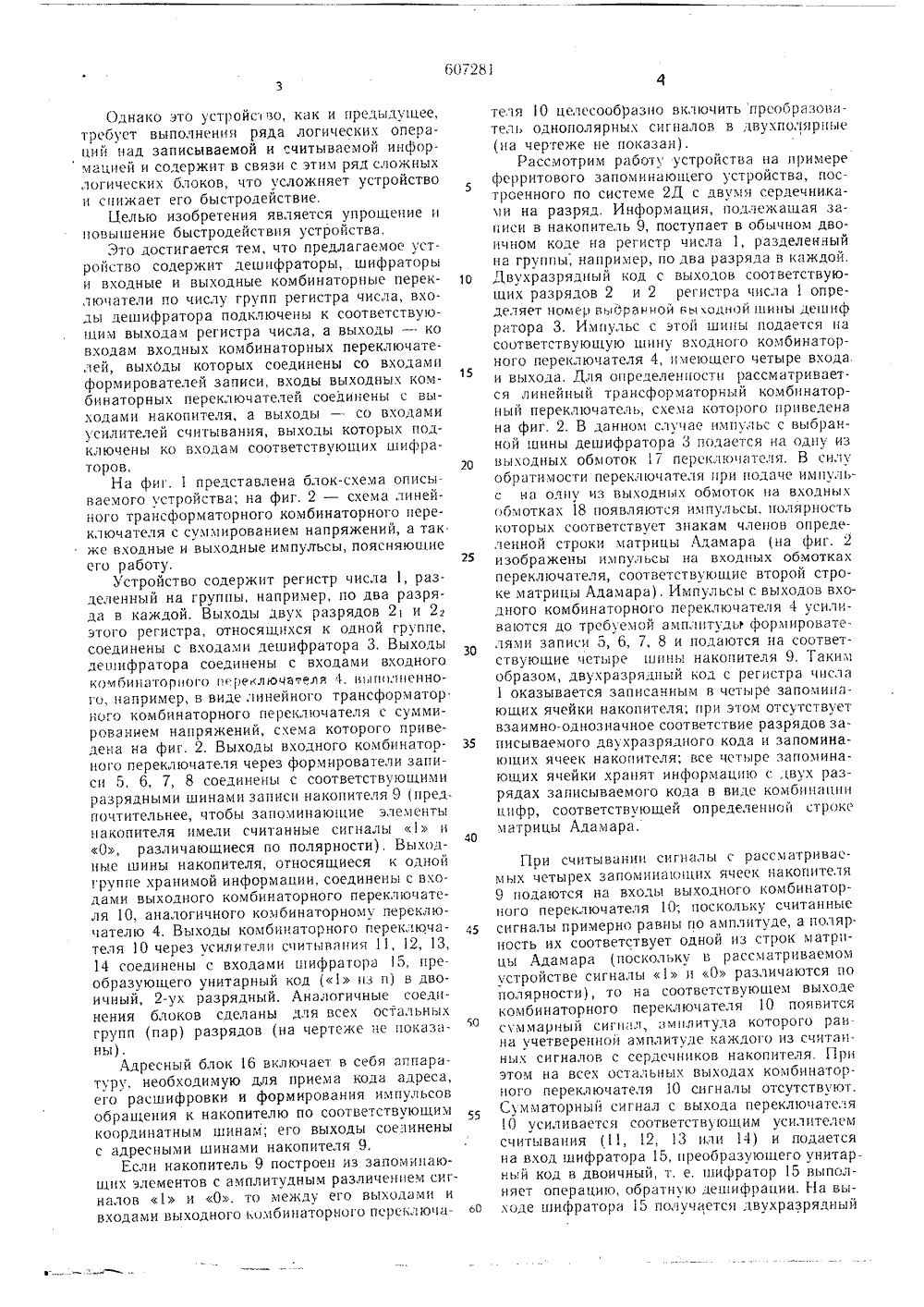

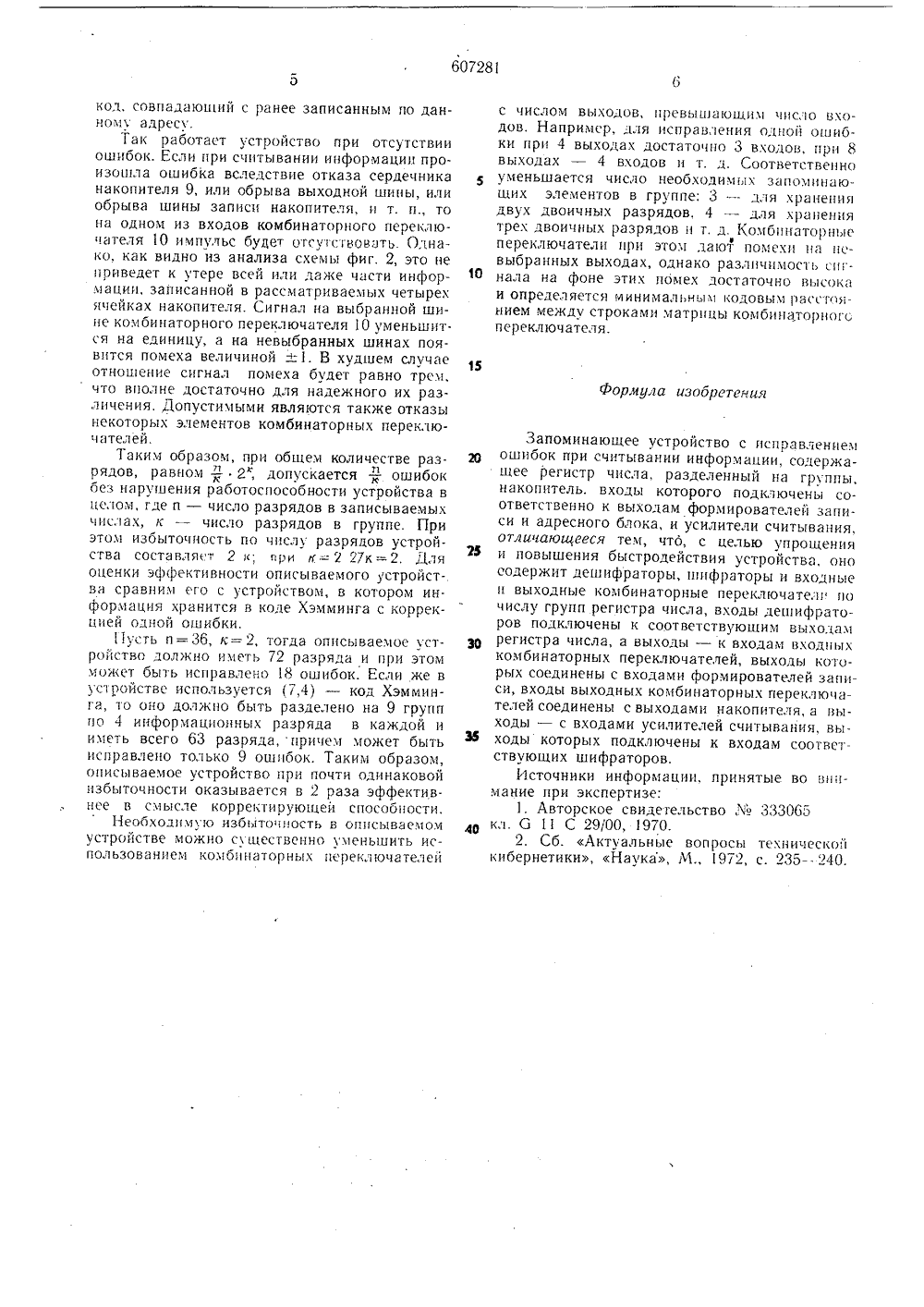

Сова Советских Соцмалмстмцаскнх РеспубеаОП ИСАНИЕИЗОБРЕТЕН ИЯ Ю АВТОУО 0 МУ СВИДВТВЛЬСТВУ(Я) М. К 9/О ис яеяяем заявк ударатееннмй камхтет Сефета 1 енннетрев СССР ае делам наееретеннй н еткрмтнй(54) ЗАПОМИНА 1 СШЕЕ ОШИБОК ПРИ СЧ требует й иад разря яет его 1 2Изобретение относятся к области запомнив- Наиболее близким по технической сущности ющих устройств. к изобретению является запоминающее устройИзвестны запоминающие устройства с ис. ство с исправлением ошибок при считывании правлением ошибок при считывании инфор- информации, содержащее регистр числа, размации, содержащие блок контроля достовер- деленный на группы, накопитель, входы кото- ности информации, соединенный с блоком уп-рого подключены к выходам формирователей равлеиия, и оперативный накопитель, подклю- записи и адрссногз блока, усилители считываченный через блок воспроизведения иблоккон- ния, кодирующий блок с входным регистром, троля дос 1 оверности информации к регистру блок образования контрольного кода, дешифрачисла, выполненному на триггерах со счетным тор адреса неисправности, блок исправления входом 1.ошибок, выходной регистр 121.В этом устройстве информация хранится в . В этом устройстве к числу, принятому на виде. кода с исправлением ошибок, содержаще. регистр, с помощью кодирующего блока добав. го информационные и контрольные разряды, ляются избыточные, проверочные разряды кода После считывания слова блок контроля досто- Хэмминга, после считывания хранимой в коде. верности информации образует из информаци- Хэмминга информации декодирующий блок.из онных разрядов контрольные и сравнивает их 1 з информационной части слова снова образует с хранимыми контрольными разрядами; в слу- проверочные разряды; считанные и вновь обрачае неравенства образованных и хранимых кон- зованиые проверочные разряды сравниваются трольных разрядов блок контроля достовернос. блоком образованияконтрольного кода; полути информации вырабатывает сигнал коррек- ченный в результате сравнения код ошибки. ции, который переводит соответствующий триг-подается на вход дешифратора адреса неисгер регистра числа в противоположное состо- правности, который дает сигнал на выходной якие. шине с тем же номером, который имеет неисОднако известное устройство вы- правный разряд, в блоке исправления ошибки полнения ряда логических операц ин- проводится инверсия информации в неисправ. формационными и контрольными дами иом разряде, и скоррек 1 чроваиная информация хранимой информации, что усложн, 25 устанавливается на выходном регистре.Однако это устройс 1 зо, как и прелылуш,ее,требует выполнения ряда логических операций пад записываемой и считываемой информацией и содержит в связи с этим рял сложныхлогических блоков, что усложняет устройствои снижает его быстродействие.Целью изобретения является упрощение иповышение быстродействия устройства.Это достигается тем, что предлагаемое устройство содержит лешифраторы, шифраторыи входные и выходные комбинаторные перек олючатели по числу групп регистра числа, входы лешифратора подключены к соответствующим выходам регистра числа, а выходы - ковходам входных комбинаторных переключателей, выхОды которых соединены со входами15формирователей записи, входы выходных комбинаторных переключателей соединены с выходами накопителя, а выходы - со входамиусилителей считывания, выходы которых подключены ко входам соответствующих шифраторов, 20На фиг. 1 представлена блок-схема описываемого устройства; на фиг, 2 - схема линейного трансформаторного комбинаторного переключателя с суммированием напряжений, а так.же входные и выходные импульсы, поясняющиеего работу.25Устройство содержит регистр числа 1, разделенный на группы, например, по два разряда в каждой. Выходы двух разрядов 2 и 2этого регистра, относящихся к одной группе,соединены с входами дешифратора 3. Выходылешифратора соединены с входами входногокомбинаторного ;релючателя 1, выполненного, например, в виде линейного трансформаторного комбинаторного переключателя с суммированием напряжений, схема которого приведена на фиг. 2, Выходы входного комбинатор- з 5ного переключателя через формирователи записи 5. 6, 7, 8 соединены с соответствующимиразрядными шинами записи накопителя 9 (предпочтительнее, чтобы запоминающие элементынакопителя имели считанные сигналы 1 и40О, различающиеся по полярности), Выходные шины накопителя, относящиеся к однойгруппе хранимой информации, соединены с входами выходного комбинаторного переключателя 10, аналогичного комоинаторному переключателю 4. Выходы комбинаторного переключателя 10 через усилители считывания 11, 12, 13,14 соединены с входами шифратора 5, преобразующего унитарный код (1 нз и) в двоичный, 2-ух разрядный. Аналогичные соединения блоков сделаны лля всех остальныхгрупп (пар) разрядов (на чертеже не показа 50ны),Адресный блок 16 включает в себя аппаратуру. необходимую для приема кода адреса,его расшифровки и формирования импульсовобращения к накопителю по соответствующимкоорлинатным шинам; его выходы соепиненыс адресными шинами накопителя 9.Если накопитель 9 построен из запоминающих элементов с амплитудным различением сигналов 1 и О, то между его выходами ивходами выходного комбинаторно о переключа- ьо теля 10 целесообразно включить преобразователь однополярных сигналов в двухполярные (на чертеже не показан).Рассмотрим работу устройства на примере ферритового запоминающего устройства, построенного по системе 2 Д с двумя сердечниками на разряд. Информация, подлеяагцая записи в накопитель 9, поступает в обычном двоичном коде на регистр числа 1, разделенный на группы, например, по два разряла в каждой. Двухразрялный код с выходов соответствующих разрядов 2 и 2 регистра числа 1 определяет номер вьс,"равной выходной шины дешиф ритора 3. Импульс с этой цины подается на соответствующую шину входного комбинатор- ного переключателя 4, имеющего четыре входа и выхода, Для опрелеленности рассматривается линейный трансформаторный комбинаторный переключатель, схема которого приведена на фиг. 2. В данном случае импульс с выбранной шины дешифратора 3 полается на одну из вьхолных обмоток 17 переключаптеля. В сил обратимости переключателя при подаче импульс на одну из выходных обмоток на входных обмотках 18 появляются импульсы, полярность которых соответствует знакам членов определенной строки матрицы Адамара (на фиг. 2 изображены импульсы на входных обмотках переключателя, соответствующие второй строке матрицы Адамара). Импульсы с выходов входного комбинаторного переключателя 4 усиливаются до требуемой амплитуда формировате. лями записи 5, 6, 7, 8 и подаются на соответствующие четыре шины накопителя 9. Таким ооразом, двухразрядный код с регистра числа 1 оказывается записанным в четыре запоминающих ячейки накопителя; при этом отсутствует взаимно-однозначное соответствие разрядов записываемого двухразрядного кода и запоминакпцих ячеек накопителя; все четыре запоминающих ячейки хранят информацию с двух разрядах записываемого кода в виде комбинации цифр, соответствующей определенной строке матрицы Адамара. При считывании сигналы с рассматриваемых четырех запоминающих ячеек накопителя 9 подаются на входы выходного комбинатор- ного переключателя 10; поскольку считанные сигналы примерно равны по амплитуде, а поляр. ность их соответствует одной из строк матрицы Адамара (поскольку в рассматриваемом устройстве сигналы 1 и О различаются по полярности), то на соответствующем выходе комбинаторного переключателя 10 появится суммарный сигнал, анлитула которого равна учетверенной амплитуде каждого из считанных сигналов с сердечников накопителя. При этом на всех остальных выходах комбинатор- ного переключателя 10 сигналы отсутствуют.Сумматорный сигнал с выхода перекл 1 очателя 10 усиливается соответствующим усилителем считывания (11, 12, 13 или 14) и подается на вход шифратора 15, преобразующего унитарнь;й код в двоичный, т. е. шифратор 15 вьполняет операцию, обратную дешифрации. На выходе шифратора 15 получается лвухразрядныйкод, совпадающий с ранее записанным по данному адресу.Так работает устройство при отсутствии ошибок. Если при считывании информации произошла ошибка вследствие отказа сердечника накопителя 9, или обрыва выходной шины, или обрыва шины записи накопителя, и т. и., то на одном из входов комбинаторного переключателя 1 О импульс будет отсутствовать. Однако, как видно из анализа схемы фиг. 2, это не приведет к утере всей или даже части информации, записанной в рассматриваемь 1 х четырех ячейках накопителя. Сигнал на выбранной шипе комбинаторного переключателя 10 уменьшится на единицу, а на невыбранных шинах появится помеха величиной +1. В худшем случае отношение сигнал помеха будет равно трем, что вполне достаточно для надежного их различения. Допустимыми являются также отказы некоторых элементов комбинаторных переключателей.Таким образом, при общем количестве разрядов, равном Я 2", допускается ф ошибок без нарушения работоспособности устройства в целом, где п - число разрядов в записываемых числах, к - число разрядов в группе. При этом избыточность по числу разрядов устройства составляет 2 к; при к: -- 2 27 к .= 2. Для оценки эффективности описываемого устройства сравним его с устройством, в котором информация хранится в коде Хэмминга с коррекцией одной ошибки.Пусть п=36, к=2, тогда описываемое устройство должно иметь 72 разряда и при этом может быль исправлено 18 ошибок. Если же в устройстве используется (7,4) - код Хэмминга, то оно должно быть разделено на 9 групп по 4 информационных разряда в каждой и иметь всего 63 разряда, причем может быть исправлено только 9 ошибок. Таким образом, описываемое устройство при почти одинаковой избыточности оказывается в 2 раза эффективнее в смысле корректирующей способности,Необходимую избыточность в описываемом устройстве можно существенно уменьшить использованием комбинаторных переключателей с числом выходов, превышающим число входов. Например, для исправления одной ошибки при 4 выходах достаточно 3 входов, при 8 выходах - 4 входов и т. д. Соответственно уменьшается число необходимых запоминающих элементов в группе: 3 - для хранения двух двоичных разрядов, 4 - для хранения трех двоичных разрядов н т. д. Комбпнаторные переключатели при этом дают помехи на не- выбранных выходах, однако различимость сиг нала на фоне этих помех достаточно высокаи определяется минимальным кодовым расстоянием между строками матрицы комбинаторного переключателя.15Формула изобретенияЗапоминающее устройство с исправлениемошибок при считывании информации, содержащее регистр числа, разделенный на группы, накопитель. входы которого подключены соответственно к выходам формирователей записи и адресного блока, и усилители считывания, отличающееся тем, что, с целью упрощения 25 и повышения быстродеиствия устройстьа, ононсодержит дешифраторы, шифраторы и входные и выходные комбинаторные переключатели по числу групп регистра числа, входы дешифраторов подключены к соответствующим выходам регистра числа, а выходы - к входам входных комбинаторных переключателей, выходы которых соединены с входами формирователей записи, входы выходных комбинаторных переключателей соединены с выходами накопителя, а выходы - с входами усилителей считывания, вы- М ходы которых подключены к входам соответствующих шифраторов.Источники информации, принятые во внимание при экспертизе:1. Авторское свидетельство333065 40 кл. б 1 С 29/00, 1970.2. Сб. Актуальные вопросы техническойкибернетики, Наука, М., 1972, с. 235 240.60728 Сос витель В. РудаО. Луговаи 7 Корректор Н. ТупицаПодписное ехреирв итета Совета М ениН и открыт Раушская иаб Ужгород, ул. БНИИПИ Государственного ко во делам изобреЗОЗЬ; Москва, ЖФиаиал ППП Патент, г

СмотретьЗаявка

2315242, 16.01.1976

ПРЕДПРИЯТИЕ ПЯ А-1178

КУЛТЫГИН АНАТОЛИЙ КОНСТАНТИНОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, информации, исправлением, ошибок, считывании

Опубликовано: 15.05.1978

Код ссылки

<a href="https://patents.su/4-607281-zapominayushhee-ustrojjstvo-s-ispravleniem-oshibok-pri-schityvanii-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением ошибок при считывании информации</a>

Предыдущий патент: Регистр сдвига

Следующий патент: Устройство для контроля постоянных блоков памяти

Случайный патент: Установка для грануляции шлака