Устройство для моделирования задач оптимального управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 507876

Автор: Башков

Текст

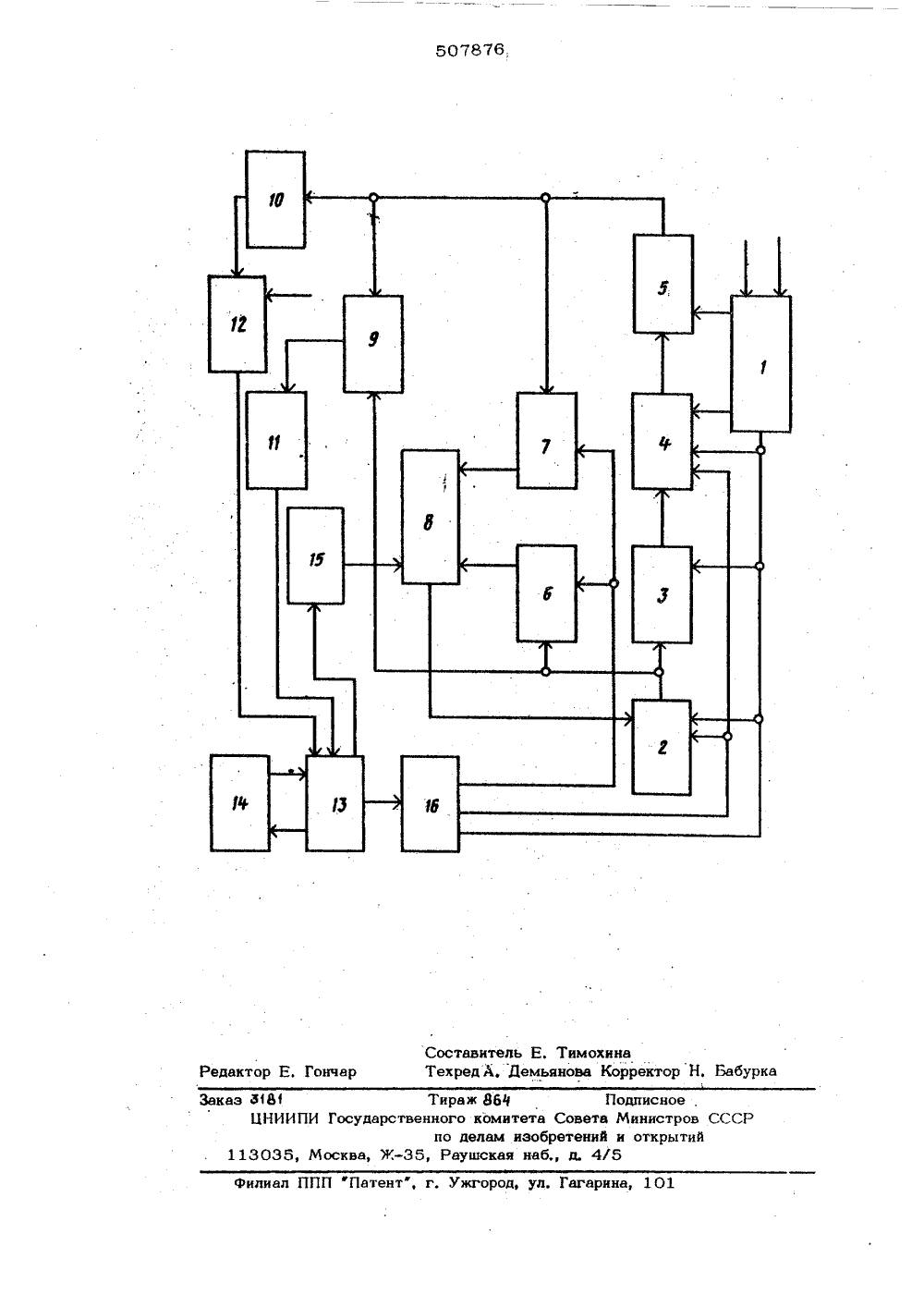

(45) Дата опубликовани Государстввнный номнтвт Саввта Мннлстров СССР но делам нзвбрвтвннй п откритнй(72) Автор изобретен Е. А. Баш 7 ) Заявител вого Красного Знамени политехничес институт онецкий орден 54) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ЗАДАЧ ОПТИМАЛЬНО УПРАВЛЕНИЯвто 5 орацифения произведения и определения невязок соединены со входам ровых компаратов. Выход бл подан на вход второго аналог тельного блока второй вход ;нен с одним иэ выходов блокбанального и конечного состояни ,ход второго аналогового вьч ормы веаналого ка управл ового вы ислисоеди которого а звданп й объекта исли телы на Вь о й аИзобретение осносится к средствам вы-числительной техники и может быть использовано при исследовании и моделированииоптимальных по быстродействию систем аматического управления объектами, поведение которых описывается линейными дифференциальными управлениями,Известно устройство для моделированиязадач. оптимального управления, представляющее собой гибридное вычислительное ус Отройство.Цель изобретения - создание устройства,позволяюшего автоматически, беэ вмешательства человека в процессе поиска, получать1за короткие промежутки времени и с достаточ 3ной точностью оптимальные решения, чторасширит круг исследователей, имеюших воэможность решать поставленную задаЧу придостаточно простой подготовке.Достигается это благодаря созданию гиб Оридного вычислительного устройства, содержа 1 шего дискретный блок управления, соединен-ный своими выходами через блок сопряженийс аналоговыми вычислительными блоками сФблоком задания начального и конечного сос 1 тояний объекта, с двумя блоками памяти, Дискретный блок управления своими выходами также соединен с входами блока определения и запоминания времени итерации и блока задания шага спуска, входы дискретного блока управления соединены . с выходами двух аналого-цифровых компараторов и с выходами,блока счета и запоминания времени итерации, Выход первого аналогового вычислительного ;блока подключен к входу одного из аналоговых блоков памяти к входу блока управле- ния, к входу блока скалярного произведения, на другой вход которого подключен выход едока образования вектора невязок, Выход блока образования вектора невязок подключен также к входу блока определения нормы ,вектора невяэок, Выходы блока скалярного507876 3,блока подключен ко входу блока образова- "; ния вектора невязок, второй вход которого связан с выходом блока задания начального и конечного состояний объекта и выход ко,торого подан на блок вычисления скалярного; . произведения и на аналоговый регистр памя- ти, Оба блока памяти своими выходами свя- заны с третьим аналоговым вычислительнымблоком, соединенным своим входом с блоком задания шага спуска и своим выходом с блоком решения сопряженной системы дифференциальных уравнений,Устройство требует только предварительных настроек (набор блок-схем решения 1 дифференциальных уравнений, задание начальных условий и некоторых параметров) и не нуждается во вмешательствА оператора в процессе поиска оптимального решения, В предлагаемом устройстве все дифференциальные уравнения решаются, аналоговыми средствами, что дает воэможность испольэовать режим периодизации с большой частотой повторения и решать задачу оптималь ного по быстродействию управления за малые промежутки времени, Время оптимального быстродействия определяется на цыфровой части устройства, что обеспечивает высокую точность решения задачи,На чертеже дана блок-схема предлагаемого устройства для решения задач оптима-, льного по быстродействию управления линейными системами.Устройство содержит блок 1 задания начального и конечного состояний объекта, аналоговый вычислительный блок 2 решения сопряженной системы дифференциальных уравненй, блок 3 управления, аналоговый вычислительный блок 4 решения дифференциальных уравнений объекта управления, блок 5 образования вектора невяэок, два аналоговых блока памяти - блоки 6 и 7 соответственно, аналоговый вычислительный блок 8определения нового приближения йптимальным зчачениям начальных условийопряженной системы, блок 9 скалярного произведения, блок 10 определения нормывектора невязок, два аналого-цифровых ком-, паратора 1 1 и 12 соответственно, дискрет-, ный вычислительный блок 13, блок 14 определения и запоминания времени итерации, блок 15 задания шагаспуска, блок 16 соп- ряжения вычислительного блока 13 с схемами управления на чертеже не показаны) аналоговых блоков 1-.7.Предлагаемое устройство работает следующим образом, Предварительно на блоке 1, задаются начальное и желаемое конечное состояние объекта и, если.йеобходимо величина интегрального ограничения на управле-4ние как одйа иэ координат вектора конечного состояния, на блоке 2 набирается соответствующай система сопряженных дифференциальных уравнений, на блоке 3 реализуются схе 5;мы вычисления компонентвектора управляюших параметров по координатам векторасопряженных переменных, поступающих сблока 2, на блоке 4 набирается схема длярешения дифференциальных уравнений объекЮта управления, на блок памяти 6 задаетсяначальное приближение к оптимальным значениям начальных условий сопряженной системы дифференциальных уравнений, на блок.памяти 7 заносится нулевой вектор невязок,на блок 12 задается необходимая точность15удовлетворения краевых условий, После этого устройство переводится в автоматический режим: работы и поиск оптимальногорешения осуществляется беэ вмешательства20оператора,Сначала выполняется нулевая итерация.Вектор начального приближения к оптимальным значениям начальных условий сопряженной системы с блока 6 через блок 8 посту 2 Ь пает на блок 2. С дискретного вычислительного блока 13 через блок 16 на блохи 1-4посылается сигнал о том что итерция выполняется во времени вперед и схемы этихблоков автоматически преобразуются" далее,30 аналогичным путем, на блоки 2 и 4 посылается сигнал пуска и начинается нулеваяитерация, которая длится до тех пор, покавычисляемое в блоке 9 скалярное произведение вектора невязок; постуающего с блока. ффЗф 5 и вычисляемого как разность между текушими координатами объекта и заданным конечным состоянием на вектор сопряженныхФпеременных, поступающий с блока 2, не станет равно нулю, В этот момент компаратор40 11 посылает сигнал на дискретный вичислительный блок 13, который через блок 16выдает сигналы; на блоки 2 и 4 - остановарешения, записи в регистры 6 и 7 значенийкомпонент ;вектора сопряженных перемен-.45 ных и компонент вектора невязок. Крометого, в процессе итерации в блоке 14 подсчитывалось текущее время, и в моментостанова блок 13 подает сигнал в блок 14,останавливающий подсчет времени итерации и сигнал на запоминание времени итерацииПосле этого дискретный блок 13 посылаетсигнал через блок 16 на блоки 2 и 4 опереводе их в исходное состояние, На этомзаканчивается нулевая итерация. 11 алее рассмотрим работу устройства ч какой-либо К-ой итерации. Блок 13 через блок 16 выдает сигнал о направлении решения задачи, если; итерация четная- вперед во времени, если итераця нечетная - низал5078Ф во времени, По этому сигналу соответствен,но преобразуются схемы блоков 1, 2, 3, 4, Затем по храняющимся в блоках 6 и 7 значениям вектора сопряженных переменных и вектора невяэок, записанным в момент окон чания предыдущей:итерации, в блоке 8 вычис: ляется новое приближение к вектору оптимальных значений начальных условий сопряженной системы, Вычисление производится по обычной градиентной формуле, причем шаг опус р ка задается с блоха 15, Полученные значения вектора начальных условий поступают на блок 2, Далее блок 13 подает сигнал пуска на блок 2 и 4 через блок 16 и сиг. нал, разрешающий счет времени на блок 14. Как и на нулевой итерации, в блоке 9 вычисляется скалярное произведение вектора сопряженных, переменных,; поступающего с блока 2, на вектор невяэок, поступающий с блока 5, В момент времени когда время К-ой итерации совпадает с временем предыдущей итерации, блок 14 выдает сигфчал на блок 13, который, после этого, опрашивает блок 11,Если этот блок выдаст сигнал о том, что скалярное произвйдение, вычисленное в блоке 9 в этот момент вре.- мени, положительно, то блок 13 вырабатывает сигнал в блок 15 на уменьшение шага спуска. Новые значения шага спуска блок 15 устанавливает в блоке 8 и К-я итерация начинается сначала. В противном слуход блока образования вектора невязок и.выход второго аналогового вычислительногоблока, блок:скалярного произведения, пер;вый вход которого соединен с выходомблока образования вектора невяэок, а вто,рой вход - с выходом второго аналогового вычислительного блока, а выход через,второй аналого-цифровой компаратор - свторым входом дискретного блока управления, к третьему входу которого подключенвыход первого аналого-цифрового компаратора и последовательйо соединенные блокзадания шага спуска, ко входу которогоподключен третий выход блока управления,и третий аналоговый вычислительный блок,к остальным входам которого .подключенывыходы аналоговых блоков памяти, а выход соединен с третьим входом второгоаналогового вычислительного блока,чае, сигнал, поступивший с блока 11, свидетельствует о том, что скалярноепроиз-, ведение отрицательно. Тогда блок 13 не прерывает решения и оновыполняется далее до тех пор, пока с блока 11 не будет получен сигнал о том, что скалярное произведение, вычисленное в блоке 9, стало равно1 нулю. В дальнейшем работа устройства аналогична нулевой итерации, но, дополнительно,блок 13 опрашивает блок 12, на которыйпоступает норма вектора невяэок, вычисленная в блоке 10 по компонентам вектора,поданным с блока 5, Если норма вектораневяэок больше заданной ошибки, то начи нается выполнение следющей итерации,если норма меньше заданной ошибки, то работа устройства прекращается. В блоке 14будет запомнено оптимальное время, нарегистре 6 будут хранится значения ком 1компонент.оптимального вектора начальныхусловий сопряженной системы,формула изобретения Устройство для Моделирования задач . э 5 оптимального управления, содержащее аналого-циФровые компараторы и блок задания начальных и конечных состояний объекта, 1первый выход которого подключен к первому ,входу блока. образования вектора Еевязох, второй выход - к первому входу первого аналогового вычислительного блока, третий выход блока задания начальных и конечных состояний обьекта соединен соответственносо вторым входом первого аналогового вычислительного блока, с первым входом бло ка управления и с первым входом второго аналогового вычислительного блока, выход вто-рого аналогового вычислИтельного блока сое 1 дийен со вторым входом блока управления, выход которого подключен к третьему входу первого аналогового вычислительного блока, выходом соединенного через блок образования вектора невязок со входом блока определения нормы вектора невязок, выход которого подключен ко входу первого аналого-цифрового компаратора, о т л и ч аю щ е е с я тем, что, с целью увеличение точности моделирования и быстродействия, оно содержит последовательно соединенные блок определения и запоминания времени ,итераций, дискретный блок управления и блок сопряжения,причем второй выход дискретного блока управления соединен со входом ,блока определения и запоминания времени итераций, аналоговые блоки памяти, к пер,вым входам которых подключен первый выход блока сопряжения, которой выход которого соединен с четвертым входом первого аналогового вычислительного блока и свторым входом второго аналогового вычислительного блока, а третий выход блокасопряжения подключен к третьему выходу блоказадания Йачального и конечного состоянийобъекта, ко вторым входам аналоговых блоков памяти подключены соответственно вы507876. тор Н. Редакто рк 035, Москва,илиад ППП "Патент, г. Ужгород, ул. Гагарина, 1 Заказ Ю 161 ОНИИПИ Государс Составитель Е. Тимохина Техред А. Демьянова Кор Тираж Вб 9 Подписное,твенного комитета Совета Министров СССР по делам изобретениИ и открытий

СмотретьЗаявка

2011371, 02.04.1974

ДОНЕЦКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

БАШКОВ ЕВГЕНИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06G 7/48

Метки: задач, моделирования, оптимального

Опубликовано: 25.03.1976

Код ссылки

<a href="https://patents.su/4-507876-ustrojjstvo-dlya-modelirovaniya-zadach-optimalnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для моделирования задач оптимального управления</a>

Предыдущий патент: Функциональный преобразователь

Следующий патент: Устройство для моделирования транспортно-технологической системы

Случайный патент: Устройство для автоматической остановки диска электропроигрывателя