Устройство для записи инфор1ации в полупроводниковые блоки постоянной памяти1изобретение относится к вычислительной технике и может использоваться при записи (программировании) информации в полу-. проводниковые

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

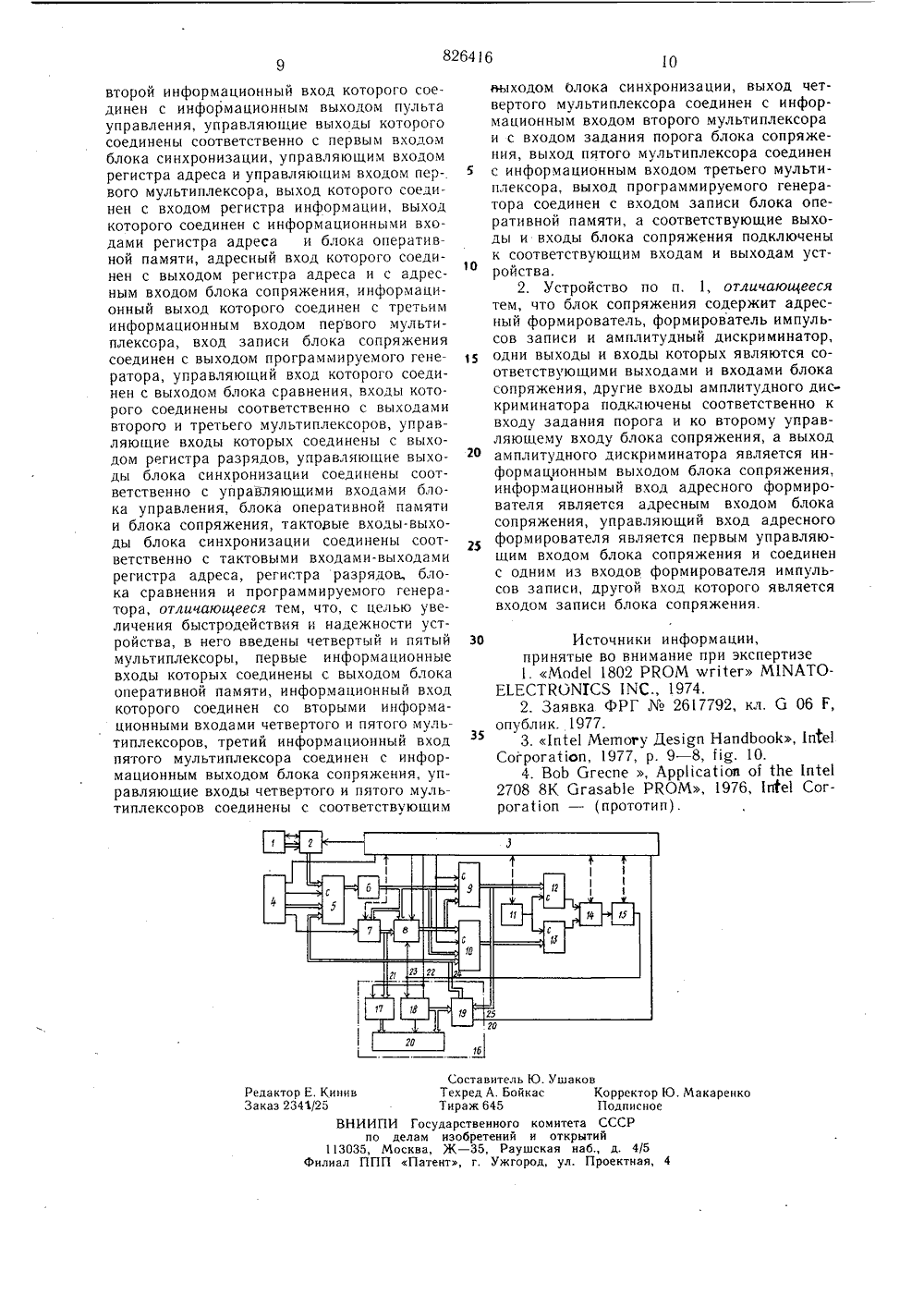

О П И С А Н И Е ии 826416ИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУСоюз СоветскннСоциалистическмкРеспубликОпубликовано 30.04.81. Бюллетень16Дата опубликования описания 05.05.81 но делан изобретений и открытий(54) УСТРОИСТВО ДЛЯ ЗАПИСИ ИНФОРМАЦИИ В ПОЛУПРОВОДНИКОВЫЕ БЛОКИ ПОСТОЯННОИ" ПАМЯТИ1Изобретение относится к вычислительной технике и может использоваться при записи (программировании) информации в полу-. проводниковые блоки постоянной памяти (микросхемы ППЗУ) и контроле этих блоков.Известно устройство для записи информации в полупроводниковые блоки памяти, содержащее блок управления, выполненный на микропроцессоре, блок оперативной и постоянной памяти, блок формирователей импульсов программирования, блок индикации и блок ввода информации. Это устройство обеспечивает запись информации с клавиатуры или с какого-либо внешнего устройства ввода и представляет собой по существу малую универсальную вычислительную машину с программным управлением 1 и 2.Недостатком его является большая сложность и необходимость разработки под каждый новый тип блока памяти кроме программного обеспечения еще и блоков электрического сопряжения интерфейсов.Другое устройство содержит блоки ввода и вывода информации, подключенные через входной буфер к информационным выводам узла фиксации блоков памяти, адресные выводы которых через адресный буфер подключены к блоку адресации а выводы программирования и выборки подключены соответственно к выходу узла программирующих импульсов узла распределителя импульсов, входы которых подключены к блоку синхронизации 3.Недостаток этого устройства состоит вмалрй функциональной возможности, так 10 как оно не может кроме последовательнойзаписи и последовательного контроля записанной информации выполнять другие функции, что в целом снижает надежность устройства.Наиболее близким техническим решени%ем к предлагаемому является устроиство для записи информации в полупроводниковые блоки постоянной памяти, содержащее первый мультиплексор, первый информационный вход которого подключен к выходу бло ка управления внешним носителем информации, второй информационный вход которого соединен с информационным выходом пульта управления, управляющие выходыкоторого соединены соответственно с первым входом блока синхронизации, управляю щим входом регистра адреса и управляющим входом первого мультиплексора, выход которого соединен с входом регистра информации, выход которого соединен с информационными входами регистра адреса и блока оперативной памяти, адресный вход которого соединен с выходом регистра адреса и адресным входом .блока сопряжения сполупроводниковым блоком постоянной памяти, информационный выход которого соединен с третьим инфоомационным входом первого мультиплексора, вход записи блока сопряжения соединен с выходом программируемого генератора, управляющий вход которого соединен с выходом блока сравнения, входы которого соединены соответственно с выходами второго и третьего мультиплексоров разрядов, управляющие входы которых соединены с выходом регистра разрядов информации, управляющие выходы блока синхронизации соединены соответственно с управляющими входами блока управления внешним носителем информации, блока оперативной памяти и блока сопряжения с полупроводниковым блоком постоянной памяти, тактовые входы-выходы блока синхронизации соединены соответственно стактовыми входами-выходами регистра адреса, регистра разрядов, блока сравнения и программируемого генератора.Кроме того, входы второго и третьего мультиплексоров разрядов информации подключены к информационному выходу блока оперативной памяти, блок синхронизации содержит генератор, счетчик и распределитель импульсов, а в качестве блока внешнихносителей информации используются фото- считыватель с перфолент или перфокарт 14.Основным недостатком этого устройства является низкое быстродействие, так как все операции проводятся последовательно и отсутствуют средства совмещения контроля блоков памяти, подбора информации к дефектным блокам памяти и т.д. из-за недостаточной функциональной гибкости устройства, следствием чего является его малая надежность.,Цель изобретения - увеличение быстродействия и надежности устройства для записи информации в полупроводниковые блоки памяти, что ведет к повышению производительности и экономии общественного труда.Поставленная цель достигается тем, что в устройство введены четвертый и пятыймультиплексоры, первые информационные входы которых соединены с выходом блокаоперативной памяти, информационный входкоторого соединен со вторыми информацион. ными входами четвертого и пятого. мультиплексоров, третий информационный вход пятого мультиплексора соединен с информационным выходом блока соцрпжения, управ.ляющие входы четвертого и пятого мультиплексоров соединены с соответствующими выходами блока синхронизации, выход четвертого мультиплексора соединен с информационным входом второго мультиплексора и с входом задания порога блока сопряжения, .выход пятого мультиплексора соединен с информационным входом третьего мультиплексора, выход программируемого генератора соединен с входом записи блока оперативной памяти, а соответствующие выходы и входы блока сопряжения подключены к соответствующим выходам и входам устройства.Кроме того, блок сопряжения содержитадресный формирователь, формирователь импульсов записи и амплитудный дискримина 5 ТОР, ОДНИ ВЪХОДЪ И ВХОДЪ КОТорЫХ ЯВЛЯЮТся соответствующими выходами и входами блока сопряжения, другие входы амплитудного дискриминатора подключены соответственно к входу задания порога и ко второму управляющему входу блока сопряжения, а выход амплитудного дискриминатора является информационным выходом блока сопряжения, информационный вход адресного формирователя являстся адресным входом блока сопряжения, управляющий вход адресного формирователя является первым управляющим входом блока сопряжения и соединен с одним из входов формирователя импульсов записи, другой вход которого является входом записи блока сопряжения.Такое построение устройства позволяет ЗЮ без значительного усложнения устройстваповысить его быстродействие и надежность .за счет совмещения операций записи, контроля и подбора информации путем подключения соответствующих блоков через четвертый и пятый мультиплексоры к полупроводниковому блоку постоянной памяти, тип которого может быть любым, поскольку он размещается в узле фиксации сменного блока сопряжения. 4 о На чертеже представлена функциональная схема устройства,Устройство содержит блок 1 внешних.носителей, блок 2 управления блоком вмешних носителей, блок 3 синхронизации, пульт, 4 управления, первый мультиплексор 5, ре-.гистр б информации, регистр 7 адреса, блок 8 оперативной памяти (ОЗУ),. четвертый 9 и пятый 10 мультиплексоры, регистр 11 разрядов, второй 12 и третий 13 мультиплексоры, блок 14 сравнения, программируемый 50 генератор 15 и блок 16 сопряжения, которыйв свою оЧередь состоит из адресного формирователя 17, формирователя 18 импульсов записи, амплитудного дискриминатора 19 и узла фиксации 20 положения блока постоянной памяти микросхемы ППЗУ.И Информационные шины показаны на чергеже двойными линиями, управляющие шины - одинарными, а тактовые шиныпунк тирными.В блоке сопряжения 6 основные входы и выходы обозначены цифрами: адресный вход 21, первый управляющий вход 22, вход 23 записи, информационный выход 24, вход 25 задания порога и второй управляющий вход 26, Соответствующие выходы и входы блока 16 сопряжения, идущие через узел фиксации 20 к ППЗУ, являются выходами и входами всего устройства.Выполнение блока сопряжения 16 в виде конструктивно-законченного узла удобно и позволяет заменять эти блоки 6 при прог. раммировании различных типов блоков постоянной памяти, так как каждый тип требует своей временной диаграммы и электрических сигналов в соответствии с требованиями технических условий, Таким образом, электрическая схема блока 6 для каждого типа будет разной, хотя функциональная схема остается прежней.Устройство может выполнять операции входного контроля, при котором проверяется отсутствие дефектов в незапрограммированных микросхемах ППЗУ или информационное содержимое ранее запрограммированных микросхем ППЗУ, ввода информации, при котором исходная информация, подлежащая записи в микросхему ППЗУ, может вводиться в блок оперативной памяти 8 с перфоленты, с магнитной ленты, ЭВМ, эталонной микросхемы ППЗУ, устанавливаемой в узел фиксации 20, с распечатки или другого документа клавиатурой пульта управления 4; программирования - запись информации в микросхему ППЗУ; входного контроля, при котором проверяется инфор мация микросхемы ППЗУ на соответствие исходной информации.Кроме того, в устройстве предусмотрен ряд других режимов, в том числе самоконтроля, непрерывного воздействия импульсами записи на плохо программируемые микросхемы, анализа процесса программирования, подбора информации к дефектным микросхемам ППЗУ или подбора микросхем ППЗУ к требуемой информации, выключение алгоритма программирования, запись инфор мации в инверсном коде, нахождения нужного файла в рулоне перфоленты и т.д,Устройство работает следующим образом.С помощью пульта 4 управления выбираются операции, которые необходимо выполнить над микросхемой ППЗУ, выбирается источник исходной информации, устанавливаются все регистры прибора в исходное состояние, в узел 20 фиксации устанавливается микросхема для контроля записи в нее информации, запускается программируемый генератор 15 и, если необходима операция входного кон 1 роля, то блок синхронизации 3 вырабатывает управляющие сигналы, по которым блок 14 сравнения и мультиплексоры 9 и 10 устанавливаются в режим входного контроля, при этом на адресные входы микросхемы, установленной в узел 20, фиксации через адресный формирователь 7 и регистра 7 адреса подается код адреса проверяемого слова, В режиме входного контроля исходное состояние регистра 6 ин 5 формации соответствует состоянию незапрограммированной микросхемы, Информация из регистра 6 информации через мульти.плексор 9 поступает на входы. мультиплек.сора 12 и на входы задания информации амплитудного дискриминатора 19, где срав нивается с информацией микросхемы ППЗУ,хранящейся в ней по данному адресу.С выхода амплитудного дискриминатора19 информация через мультиплексор 10 поступает на информационные входы мультиплексора 13. Мультиплексоры 12 и 13, управляемые регистром 11, выдают псючередно информацию соответствующих разрядов мультиплексоров 9 и 10 на входы блока сравнения 14. Если амплитудные значения сигналов с выходов проверяемой микросхе 2 ф мы ППЗУ отличаются от значений предусмотренных ТУ на незапрограммированную микросхему; то блок сравнения 14 выдает управляющий сигнал в блок синхронизации 3, по которому управляемый генератор 15 останавливается и индицируется адрес, информация микросхемы ППЗУ по этому адресу и сигнал брака входного контроля, Если амплитудные значения сигналов с выходов проверяемой м и кросхемы П ПЗУ соответствуют значениям, предусмотренным ТУ Зо на незапрограммированную микросхему, тоблок сравнения 14 выдает сигнал на генератор 5, по которому последний, работая в режиме контроля, выдает импульсы на блок синхронизации 3 для управления ре. гистром разрядов 1 и регистром адреса 7. З Проконтролировав последний разряд пос-. ,:леднего слова, блок синхронизации 3 останавливает генератор 15 и индицируетконец работы прибора, если другие операции не были ранее. выбраны на пульте управления 4;Если выбрана операция ввода и контроля информации с внешнего носителя, например с перфоленты, то блок управления внешним носителем 2 включает фотосчитывающее устройство блока внешних носителей 1 и после обработки кодов служебной инфор.45 мацни выдает информацию через мультиплексор 5 в регистр информация 6,вырабатывает сигнал пуска генератора 15 и оста.нова фотосчитывающего устройства блока 2.С регистра 6 информация поступает на информационные входы блока оперативной памяти 8 и через мультиплексор 9 на мультиплексор 12. Информация, хранимая блоком оперативной памяти 8 через мультиплексор 10. поступает на мультиплексор 13. Информация с мультиплексоров 2 и 13 поразрядно сравнивается в блоке 14 сравненйя и при ее неравенстве по управляющему сигналу из блока сравнения 14, управляемый генера- тор 15 вырабатывает сигнал записи, по ко.82641 5203040 торому в блок 8 оперативной памяти записывается входная информация, поступаюшая с регистра 6 информации.После контроля последнего разряда вводимого слова, генератор 15 выдает сигнал, по которому блок 3 синхронизации устанавливает следующий адрес в регистре 7 адреса через блок 2 управления, включает фотосчитываюшее устройство и останавливает генератор 15. Блок 1 внешних носителей считывает информацию с перфоленты через блок 2 и мультиплексор 5, вводит ее в регистр 6 информации. Блок 2 останавливает фотосчитывающее устройство и через блок 3 синхронизации запускает генератор 15. Далее процесс повторяется как описано выше, пока не будет закончен и проконтролирован ввод информации последнего слова, В случае ошибки при вводе информации блок 14 сравнения и блок 2 управления выдают в блок 3 синхронизаци сигналы сбоя, устройство останавливается, индицируется: адрес, вводимая и введенная информация и вид сбоя.После ввода информации устройство либо останавливается, либо переходит к выполнению следующей операции программирования. При программировании информация, считанная из блока 8 оперативной памяти через мультиплексор 9 поступает на мультиплексор 12, а информация, считанная из микросхемы ППЗУ, установленной в узел 20, через амплитудный дискриминатор 19 и мультиплексор 10 поступает на мультиплексор 13, Далее, как и при выполнении предыдугцих операций, информация с мультиплексоров 12 и 13 поразрядно сравнивается блоком 14 сравнения и в случае несовпадения информации, пои которой из микросхемы ППЗУ блок (20) считывается сигнал, соответствующий незапрограммированному биту, а из ОЗУ блок(8) - сигнал, соответствующий запрограммированному биту, генератор 15 по управляющему сигналу с блока 4 сравнения выдает импульс записи, по которому формирователь 18 программирования формирует импульсы напряжения и тока с амплитудными и временными параметрами, соответствующими нормам ТУ на программируемую микросхему.После воздействия импульсами записи предусмотренным способом программирования, если соотношение сигналов с ОЗУ и с ППЗУ не изменилось, адресный формирователь 7 во время действия импульсов записи, если это необходимо, формирует адресные входные сигналы, соответствующие требованиям ТУ на программируемую микросхему. По окончании импульсов записи адресный формирователь 17 формирует стандартные логические сигналы, необходимые для считывания из микросхемы ППЗУ информации выбранного слова, Если по выбранному разряду из микросхемы ППЗУ (узел 20) считывается сигнал, соответствующий за 6 8программированной ячейке, а из ОЗУ(блок 8) считывается сигнал, соответствующий исходному сигналу незапрограммированной микросхемы, то блок 14 сравнения выдает сигнал останова и индицируется адрес, информация ОЗУ, информация микросхемы ППЗУ и сигнал невозможности программирования.В случае совпадения информации, поступающей на входы блока 14 сравнения, генератор 15 выдает сигнал в блок 3 синхронизации, по которому к блоку 14 сравнения подключаются следующие разряды микросхемы ППЗУ (блок 20) и ОЗУ (блок 8) и т.д. После контроля и программирования последнего слова блок 3 синхронизации останавливает программу и индицирует сигнал окончания выполнения всех операций в том случае, если выбранные на пульте 4 управления операции выполнены.Если выбрана операция выходного контроля, т,е, контроля правильности программирования по установленным уровням дискриминации выходных напряжений микросхемы ППЗУ, то как и при выполнении операции программирования, информация из ОЗУ (блок 8) через мультиплексоры 9 и 12 поступает на один вход блока 14 сравнения, а информация, считываемая с микросхемы ППЗУ (блок 20), через мультиплексоры 10 и 13 на другой вход блока 14 сравнения.При выполнении операции выходного контроля устройство работает так же как и при программировании, за исключением случая, когда из ОЗУ (блок 8) считывается сигнал, соответствуюший запрограммированному биту, а из микросхемы ППЗУ (блок 20) считывается сигнал, соответствующий незапрограммированному биту. В этом случае генератор 15 выдает сигнал брака, по которому блок синхронизации 3 останавливает программу и индицирует адрес, информацию ППЗУ и ОЗУ и причину останова.Если информационное содержимое ОЗУ и микросхемы ППЗУ совпадает по всем словам, то после контроля последнего разряда последнего слова программа останавливается и индицируется сигнал окончания выполнения всех операций.Таким образом, предлагаемое устройство позволяет увеличить быстродействие устройства в 2 раза и повысить надежность записи информации и всего устройства за счет совмешения операций без усложнения конструкций.Формула изобретения1. Устройство для записи информациив полупроводниковые блоки постоянной памяти, содержашее блок управления, входы- выходы которого являются входами-выходами устройства, информационный выход блока управления соединен с первым информационным входом первого мультиплексора,826416 1 О Составитель Ю. Ушаков Редактор Е. Кинив Техред А. Бойкас Корректор Ю. Макаренко Заказ 2341/25 Тираж 645 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж - 35, Раушская наб., д. 4/5 Филиал ППП Патент, г. Ужгород, ул. Проектная, 4второй информационный вход которого соединен с информационным выходом пульта управления, управляющие выходы которого соединены соответственно с первым входом блока синхронизации, управляющим входом регистра адреса и управляющим входом пер-. вого мультиплексора, выход которого соединен с входом регистра информации, выход которого соединен с информационными входами регистра адреса и блока оперативной памяти, адресный вход которого соединен с выходом регистра адреса и с адресным входом блока сопряжения, информационный выход которого соединен с третьим информационным входом первого мультиплексора, вход записи блока сопряжения соединен с выходом программируемого генератора, управляющий вход которого соединен с выходом блока сравнения, входы которого соединены соответственно с выходами второго и третьего мультиплексоров, управляющие входы которых соединены с выходом регистра разрядов, управляющие выходы блока синхронизации соединены соответственно с управляющими входами блока управления, блока оперативной памяти и блока сопряжения, тактовые входы-выходы блока синхронизации соединены соответственно с тактовыми входами-выходами регистра адреса, регистра разрядов, блока сравнения и программируемого генератора, отличающееся тем, что, с целью увеличения быстродействия и надежности устройства, в него введены четвертый и пятый мультиплексоры, первые информационные входы которых соединены с выходом блока оперативной памяти, информационный вход которого соединен со вторыми информационными входами четвертого и пятого мультиплексоров, третий информационный вход пятого мультиплексора соединен с информационным выходом блока сопряжения, управляющие входы четвертого и пятого мультиплексоров соединены с соответствующим выходом блока синхронизации, выход четвертого мультиплексора соединен с информационным входом второго мультиплексораи с входом задания порога блока сопряжения, выход пятого мультиплексора соединенв с информационным входом третьего мультиплексора, выход программируемого генератора соединен с входом записи блока оперативной памяти, а соответствующие выходы и входы блока сопряжения подключенык соответствующим входам и выходам устройства.2. Устройство по п. 1, отличающеесятем, что блок сопряжения содержит адресный формирователь, формирователь импульсов записи и амплитудный дискриминатор,15 ОДНИ ВЫХОДЫ И ВХОДЪ КОТорЫХ ЯВЛЯЮТСЯ СОответствующими выходами и входами блокасопряжения, другие входы амплитудного дискриминатора подключены соответственно квходу задания порога и ко второму управляющему входу блока сопряжения, а выходамплитудного дискриминатора является информационным выходом блока сопряжения,информационный вход адресного формирователя является адресным входом блокасопряжения, управляющий вход адресногоформирователя является первым управляющим входом блока сопряжения и соединенс одним из входов формирователя импульсов записи, другой вход которого являетсявходом записи блока сопряжения,30 Источники информации,принятые во внимание при экспертизе1. Моде 1802 РВОМ ъг 11 ег М 1 хАТОЕ 1 ЕСТКОх 1 Сс 1 1 х 1 С., 1974.2. Заявка ФРГ,х 1"в 2617792, кл. б 06 Г,опублик. 1977.3. 1 пте Мегпогу Дез 1 дп НапдЬОО 1 с, 1 п 1 еСогрога 1 оп, 1977, р. 9 - 8, 11 д. 10.4. ВоЬ бгеспе, Арр 1 са 11 оа о 1 1 Те 1 п 1 е 12708 8 К бгазаЫе РКОМ, 1976, псе СогрогатОп - (прототип).

СмотретьЗаявка

2773895, 01.06.1979

ПРЕДПРИЯТИЕ ПЯ М-5769

МИРОНЦЕВ ВЯЧЕСЛАВ ИВАНОВИЧ, АКИНФИЕВ АНДРЕЙ БОРИСОВИЧ, УШАКОВ ЮРИЙ ЛЕОНИДОВИЧ

МПК / Метки

МПК: G11C 29/00, G11C 7/00

Метки: блоки, вычислительной, записи, инфор1ации, информации, использоваться, может, относится, памяти1изобретение, полу, полупроводниковые, постоянной, проводниковые, программировании, технике

Опубликовано: 30.04.1981

Код ссылки

<a href="https://patents.su/5-826416-ustrojjstvo-dlya-zapisi-infor1acii-v-poluprovodnikovye-bloki-postoyannojj-pamyati1izobretenie-otnositsya-k-vychislitelnojj-tekhnike-i-mozhet-ispolzovatsya-pri-zapisi-programmirovan.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для записи инфор1ации в полупроводниковые блоки постоянной памяти1изобретение относится к вычислительной технике и может использоваться при записи (программировании) информации в полу-. проводниковые</a>

Предыдущий патент: 826415

Следующий патент: Запоминающее устройство

Случайный патент: Стабилизированный источник напряжения постоянного тока