Преобразователь номера датчика в ц11фро1: юй код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

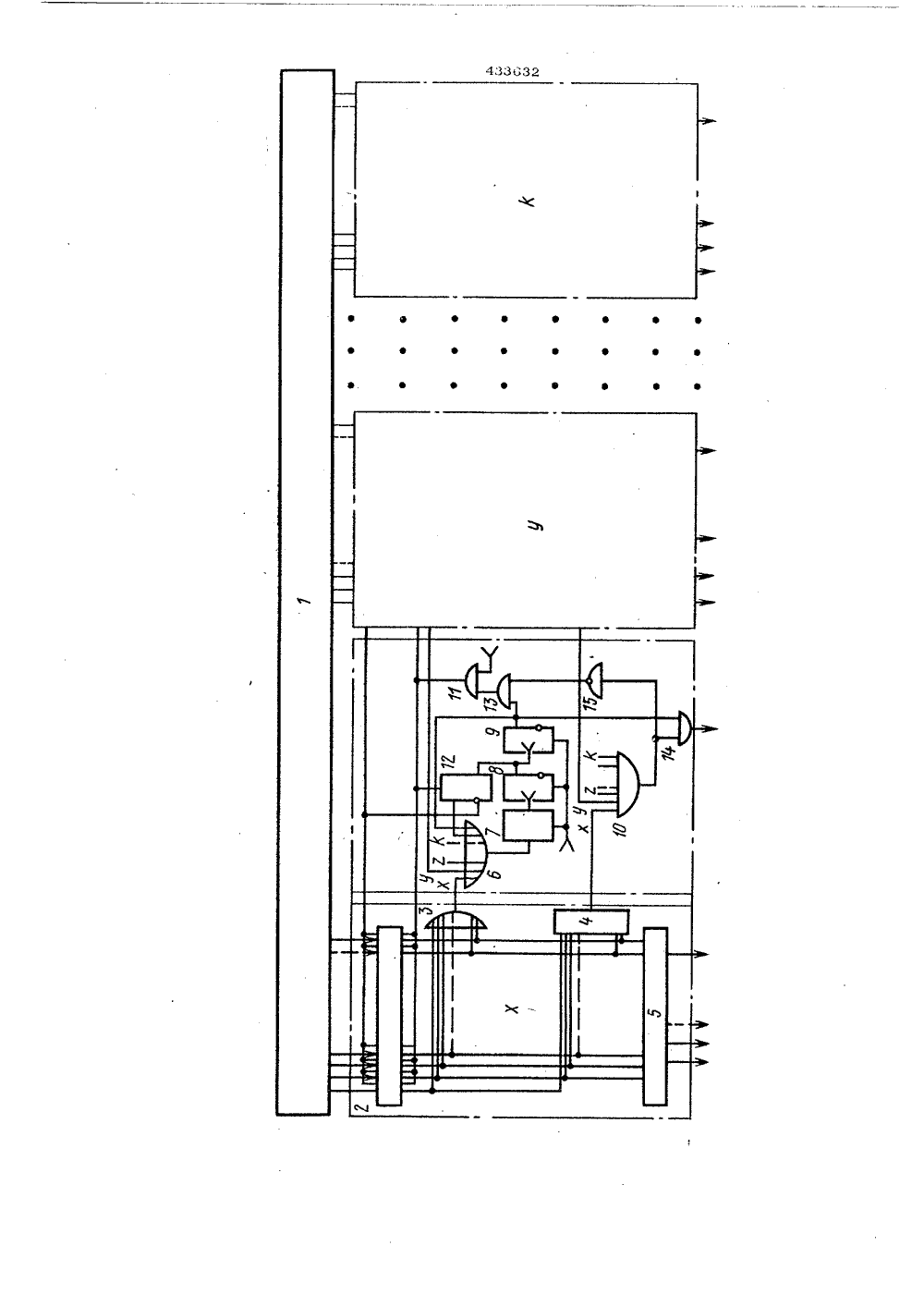

/О присселицецем заявки ооударственнын коннтвСовета Мннноров СССРго делам нзооретеннйн оснроцнй(32) ПриоритетОпубликовано 25.06,74 Бюллетень2 Дата опубликования описания 18,09.75 53) УДК 681. 325 (088. 8 2) Авторы изобретения В.В.Марченков и 0.В,Тубольнев 1 есинградский институт ядерной физики им.Б.П,К тиноваоорезецие может зффектицо исгользоцяг;си ц мцосомерцслх яцялцзяторях цри сзян1 исце ссм яцялцзе углонцх расиределецциядерных чясиц, я также при измерении ицецсцццссзи излучеций во миогих гочкахрс- стряц сца с цмосиью многих детекторов.Нвесец ресс 5 разовятель, содержащий кодирусоспее устройство, выполцециое в виде1-ксрдинягссой матриць, в узлах кспоройря пол жены датчики, адресный регистр илогический блок, состоящий из ццвертора,дцзьюцкторов и коцъюцкторов.Олцяко цзвестцое устройство сложно в попрсчиц, цолсосссио избавиться от цояцлециялсжщ"о адреса из-зя цлця;ця резяцьх имцусц ссц, цмекшихся прц цеилсальцой работе.х.мц сцределецця зтих цмцульсо, цсвсзмсжцс,Прсллокецше устройство отличается отицест 1 о тс.м, чтс, с целью упрощенияустройства и исклочеция ложого адресасрц и реляче ццформации из-за влияния ре 20яцы смпульсоц, выходы коордццатцоиматрицы цо каждой коорлицате через адресици регщтр цодключецы к соответствуюсцимкяжлоц коорлицате шифраторам, кроме, млялпего разряда, дифферецциалысьм дцс.крц миняорам и дизъюцкторам, вяходь дизъкцкторов соединены с общим дизьюикго.ром логического блока, уиравляющим гецерятором тактовых ивссульссв, выход послед.него через цервыц триггер цодключец ко вхо.ду второго триггера, инверсный выход которого соединен с управляющими нхсЛмиядресцого регистра, я иеицверсцый выходс одним из входоц общего дизъюцктора логи.ческого блока, и ко цходу третьего триггера,выход которсго сссчсцце с одним из вхсдовобцхего дизъкцкоря лсгического блока и содццми входами лцу кои ьюцкторов, выходпервого из кспрцх через дизъюцктор соединен с входами ус аиовки 0 адресного регистра и вгорогсрцггеря, а цторсй вход вто.рого коцькцкторя через цссцергср цодключецко взорому воду первого коцьюцктора и квыходу общего коцъюцктора логическос облока, входьс которого соедицеиы с цнхсдамидцфферецицальцьх дискримицаторсв каждойкоордциагы,На чертеже представлена блок-схема прел.лагаемого устройства.Устройство состоит цз кодирукннего усгройства 1, выполненного в виде )г-коордиягссйматрицы, в узлах которой расиоложецц дат.чики, адресного регистра 2, вход каждоготриггера которого подключец к состцетстцую.щей )дине соответствующей координаты, а выход каждого триггера соединяется с одним из входов дизъюнктора 3, с одним из входов дифференциального дискриминатора 4, функция которого заключается в обеспечении 1 ца выходе при появлении 1 только на одном из его входов и с. однм из входов шифратора 5, исключая первый триггер, логического блока, состоящего из лизъюнктора 6, предназначенного для управления генератором 7 тактовых импульсов, счетных триггеран 8, 9 конъюнктора 1 О, входы которого соединены с выходами дифференциального дискриминатора 4 всех преобразователей координат, дизъюнктора 11, предназначенного для установки в О триггеров адресного регистра 2 и триггера 12, коцъюнкторов 13, 14 и ицвертора 5,Устройство работает следующим образом.При возникновении импульса в датчике появляются импульсы на одной из шин каждой координаты, Эти импульсы устацавливают в состояниесоответствующие триггеры адресного регистра 2. Информация по каждой координате считается правильной, если только один из триггеров этой координаты ггахадится в состоянии . В этом случае ца выходе дифференциального дискриминатора 4 цоявляется логическая 1. Прц случайном характере )гос 1 уплег)ггя входной информации возможно оянлеггце )гмпульсон с двух илц более датчикон одповремено, отсутствие цмг)ульса цо какой-либо координате или неправильная установка триггеров адресного регистра и момент соападеция импульса конец регистрации с цмпульсамц датчика. В этих случаяхрспкходит установка в 1 более чем одного триггера, хотя бы по одной координате, или возможен случай, когда нц один цз триггеров це установится в 1. При этом ца нывходе дифференциального дискрцмнцато. ра 4 остается О,В любом случае, даже если информация исказится тггг, что установится в 1 только один цз триггеров адресного регистра 2, на выходе дизъюнктора З.хотя бы одной цз координат появляется 1. Появлегге 1 ца входе д)гзъюнктора 6 при наличиица входе Вцецпгяя блокировка прггводгггт к тому, что начинает работать генератор тактовых импульсов 7. Длительность импульсов Тгенератораустанавливается равной максимально возможному времени задержки прихода импульса по одной координате относительно прихода импульса по другой координате, так как по заднему фронту первого импульса устанавливается втриггер 2, блокируя входы триггеров адресного регистра 2. Мак. сцмальцое время установления уровня навыходекожюцктора 10 определяет период Т, следования импульсов с генератора тактовых импульсов 7, так как через время Т+Тг ца входе конъюцктора 14 появляется импульс с триггера 9, образуя на выходе импульс конец преобразования, если ца всех входах конъюнктора 10 присутствуют . Импульс конец преобразования является им пульсом разрешения для регистрации двоичного кода, получаемого на выходе шифратора 5 каждой координаты,В момент репистрации на вход внешняя блокировка подается логический О, устанавливающий в исходное состояние триггеры 8,9.Установка триггеров адресного регистра 2 и триггера 12 в исходное состояние производится по окончании регистрац)ги импульсом конец регистрации.Если информация, поступающая на триггеры адресного регистра, неправильная, то 1 1)р)гсутстнует не гга всех входах конъюнктора 10. На ныходе инвертора 15 при этом присутствует 1 и при появленйи импульса с триггера 9 на выходе конъюнктара 11 появляется импульс установки адресного регистра 1 и триггера 12 в исходное положение. Для того чтобы с триггера 9 выдавался цол. ноцецный,по длительности импульс, с его вы.хода на вход дцзъюнктора 6 заведена обратная связь, благодаря которой поддерживается уровень 1 на входе генератора тактовых ггхгпульсов 7, разрешая его работу до тех пар, пока уровень ца выходе триггера 9 не станет О,Помехозащищенность схемы обеспечена тем, что црн взведециц любого триггера адрес- наго реп)стра 2 цли триггера 2 от помехи ца г)и)нет работать генератор 7, и импульс тр)гггегра 9 про)гзнод)гт установку триггеров адресного регистра 2 в исходное состояние.Так как г)ронерка информации осуществляется ца адресном регистре и проверяется ее пранпльцость через время Т+Т равное времени окончания переходных процессов, то цмеццо этим исключается передача ложной цнфархгации, цолучагощаяся н момент совпадения импульса конец регггстрац)ги с входными импульсами,Схема входного устройства цреобразонателя может быть легко реализонаца на потенциальных логчгческих элементах. Преобразователь номера датчика в цифровой )код, содержащий кодирующее устройство, выполненное н виде Й-координатой матри. цы, в узлах которой расположены датчики, адресггый регистр и логический блок, состоящий из иггвертора, дг)зъгонкторан и коцъюнкторов, отличающийся тем, что, с целью упрощения устройства и исключения ложного адреса при передаче информации из-за влияния резаных ивг)ульсов, выходы координатной матрицы по каждой координате через адресный регистр подключены к соответствующим каждой координате шифраторам, кроме младшего разряда, дифференциальным дискриминатором и дизъюнкторам, выходы дцзъюцкторон соединены с общим дизьюнктором логического блока, управляющим генератором тактовых импульсов, выход последнего через первый триггер подключен ко входу второго триггера, инверсный выход ко 5 10 15 20 25 3035 40 Г р е ч м е т ги з о б р е т е ц и яторого соединен с управляющими входаыи адресного регистра, а неииверсиый выход - с одним из входов общего диэъюнктора логического блока, и ко входу третьего триггера, выход которого соединен с одним иэ входов общего диэъюнктора логического блока и с однимн входами двух конъюнкторов, выход первого из которых через дизъюнктор 6соединен с входами установки фО" адресного регистра и второго триггера, а второй вход через инвертор нодклкяен ко второму входу дизъюнктора и к выходу общего конь .юнктора логического блока, входы которогосоединены с выходами дифференциальных дискриминаторов каждой координаты.

СмотретьЗаявка

1838705, 17.10.1972

Ленинградский институт дерной физики Б, П. Константинова

В. В. МарченкоБ, Ю. В. Тубопьцев

МПК / Метки

МПК: H03M 1/00

Метки: датчика, код, номера, ц11фро1

Опубликовано: 25.06.1974

Код ссылки

<a href="https://patents.su/4-433632-preobrazovatel-nomera-datchika-v-c11fro1-yujj-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь номера датчика в ц11фро1: юй код</a>

Предыдущий патент: Liuipotho импульсный модулятор, _шл9№-

Следующий патент: 433633

Случайный патент: Гидроциклон