Устройство для суммирования чисел в дополнителььном коде с плавающей запятой

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

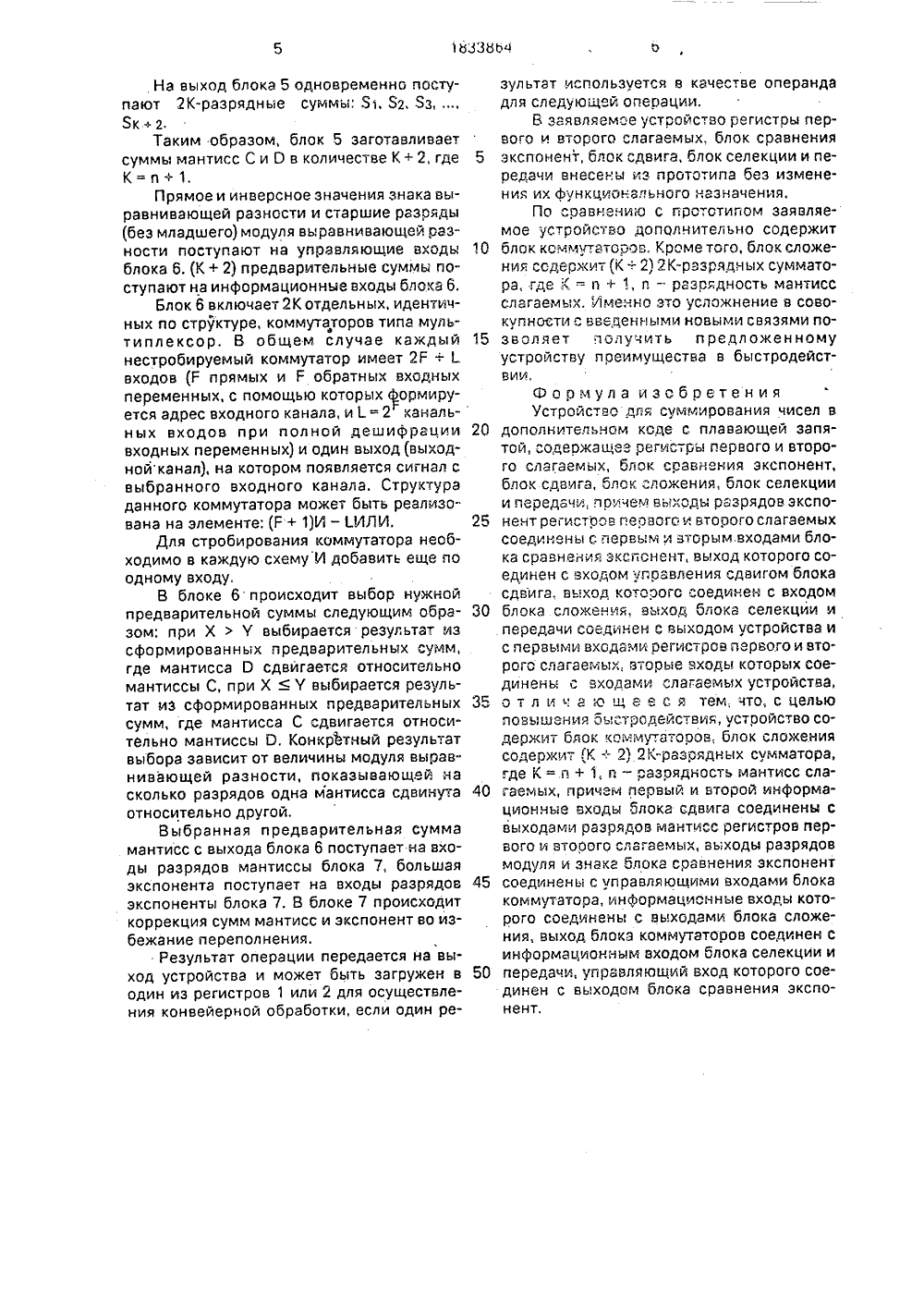

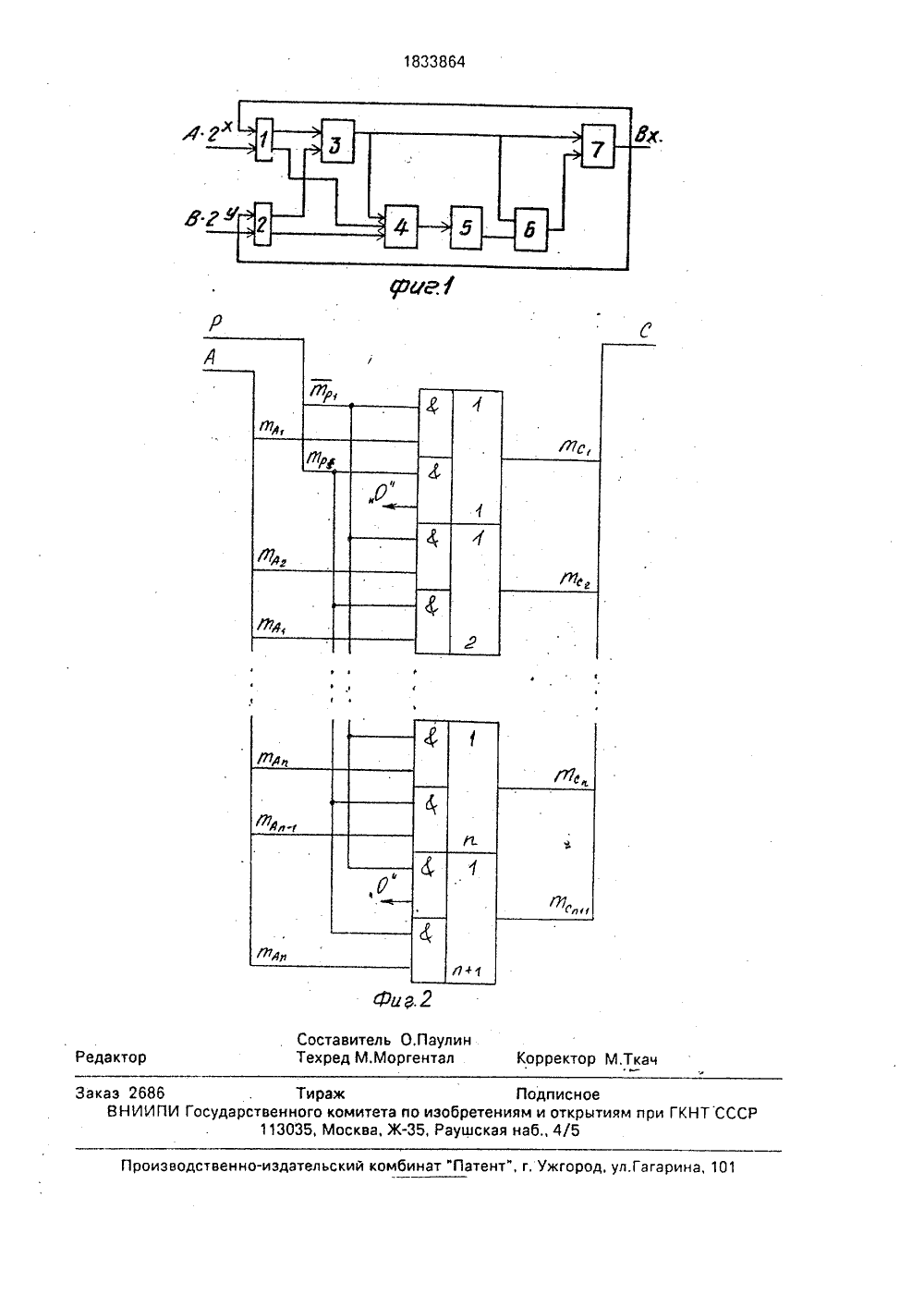

(51) 5 ГОСУДАРСТВЕННОЕ ПАТЕНТВЕДОМСТВО СССР) САНИЕ ИЗОБРЕТЕНИЯ ВАНИЯ КОДЕ С АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(71) Одесский политехнический институт(56) Карцев М.А, Арифметика цифровых машин. - М,: Наука, 1969, с. 327-328,Папернов А.А. Логические основы ЦВТ. -М.: Советское радио, 1972,Самофалов К.Г., Луцкий Г.М, Структураи функционирование ЭВМ и систем. - Киев:Вищэ школа, с, 101. Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств вычислительных машин с плавающей запятой,Цель изобретения - повышение быстродействия,Существенным отличием предложенного устройства является использование в блоке сложения (К+ 2) 2 К-разрядных сумматора (где К = и + 1, и - разрядность мантисс слагаемых) на которых происходит подготовка (К+ 2) 2 К-разрядных сумм мантисс Я 1, Я 2 ЯК+ 2, Причем сдвиг мантисс чисел А и В на сумматорах относительно друг друга происходит на два разряда, т.к, в блоке сдвига осуществляется предварительный сдвиг на один разряд мантисс первого и второго слагаемых в сторону младших разрядов при значении младшего разряда модуля, равном логической единице (в случае логического нуля сдвиг мантисс не происходит). В блоке коммутаторов под управлениемстарших разрядов модуля и знака выделяет(54) УСТРОЙСТВО ДЛЯ СУММИРО КИСЕЛ В ДОПОЛНИТЕЛЬНОМПЛАВАЮЩЕЙ ЗАПЯТОЙ(57) Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств вычислительных машин с плавающей запятой. Целью изобретения является повышение быстродействия. Устройство содержит регистры 1, 2 первого и второго слагаемых, блок 3 сравнения экспонент, блок 4 сдвига, блок 5 сложения, блок 6 кол 1 мутаторов, блок 7 селекции и передачи. 2 ил. ся единственный правильный результат суммирования,Следовательно, в предложенном устройстве совмещаются во времени процессы формирования старших разрядов модуля (для сдвига мантисс) и сложения мантисс, т.е. совмещаются во времени операции, выполняемые в прототипе последовательно, что приводит к повышению быстродействия. Кроме того, блок сдвига в заявляемом устройстве функционирует в среднем в п/2 раз быстрее, чем блок сдвига прототипа.На фиг. 1 представлено устройство для суммирования чисел в дополнительном коде с плавающей запятой, которое содержит регистры 1 и 2 первых и вторых слагаемых соответственно, блок сравнения экспонент 3, блок сдвига 4, блок сложения 5, блок коммутаторов 6, блок селекции и передачи 7.Выходы разрядов экспонент регистров 1 и 2 соединены с первым и вторым входами блока 3, выход которого соединен с входом управления сдвигом блока 4, выход которого соединен с входом блока 5, выход блока7 соединен с выходом устройства и с первыми входами регистров 1 и 2, вторые входы которых соединены с входами слагаемых устройства, первый и второй информационные входы блока 4 соединены с выходами разрядов мантисс регистров 1 и 2, выходы разрядов модуля и знака блока 3 соединены с управляющими входами блока б, информационные входы которого соединены с выходами блока 5, выход блока б соединен с информационным входом блока 7, управляющий вход которого соединен с выходом блока 3.Устройство работает следующим образом,Поступающие на входы регистров 1 и 2 слагаемые А 2" и В 2" запоминаются на время, необходимое для выполнения операции их алгебраического сложения в дополнительном коде, Экспоненты Х и У с выходов регистров поступают на входы блока 3, где они сравниваются (вычисляется в дополнительном коде т.,н. выравнивающая разность Х - У); большая по модуля экспонента сохраняется. Знак и модуль выравнивающей разности также сохраняются и далее используются в качестве критерия выбора. из предварительно заготовленных сумм коэффициентов А и В соответствующей суммы,Коэффициенты А и В с выходов регистров 1 и 2 поступают соответственно на первый и второй информационные входы блока 4, а не его вход управления поступают прямое и инверсное значения младшего разряда модуля выравнивающей разности. Блок 4 включает узел сдвига мантиссы А и узел сдвига мантиссы В, Функциональная схема узла сдвига мантиссы А показана на фиг. 2.Узел сдвига мантиссы А состоит из и + 1 элементов 2 - 2 И - 2 ИЛИ, На первые входы каждого первого элемента И всех элементов 2 - 2 И - 2 ИЛИ поступает инверсное значение младшего разряда модуля выравнивающей разности вр 1. На пе,рвые входы каждого второго элемента И всех элементов 2 - 2 И - 2 ИЛИ поступает прямое значение младшего разряда модуля выравнивающей разности вр 1. На вторые входы каждого первого элемента И элементов 2 - 2 И - 2 ИЛИ с номерами 1 - и поступают соответственно разряды с первого по и-й мантиссы . А: ид 1, ., вдп, на второй вход первогоэлемента И элемента 2 - 2 И - 2 ИЛИ с номером и+ 1 поступает логический О. На вторые входы каждого второго элемента И элементов 2 - 2 И - 2 ИЛИ с номерами 2 - и + 1 поступают соответственно разрядц мантиссы А; вд 1,вд. На второй вход второго элемента И элемента 2 - 2 И - 2 ИЛИ с номером 1 поступает логический О,Аналогично углу сдвига мантиссы А устроен узел сдвига мантиссы В.5 Узел сдвига мантиссы А функционируетследующим образом.При значении младшего разряда модуля выравнивающей разности, равном логическому нулю (в этом случае значение вр 1равно логическому нулю, а вр 1 - логическойединице) к выходам элементов 2 - 2 И 2 ИЛИ подключаются выходы первых элементов И всех элементов 2 - 2 И - 2 ИЛИ исдвига мантиссы А в сторону младших раэ 15 рядов не происходит. При значении млад шего разряда модуля выравнивающейразности, равном логической единице (вэтом случае значение вр 1 равно логическойединице, а гпр 1 - логическому О) к выходам20 элементов 2 - 2 И - 2 ИЛИ подключаютсявыходы вторых элементов И всех элементов2 - 2 И - 2 ИЛИ. и происходит сдвиг мантиссыА на один разряд в сторону младших разрядов. На выходах элементов 2 - 2 И - 2 ИЛИформируются разряды вс 1, ., всп+1, гдевс 1 - первый разряд, всп+1 - (и + 1)-й разряд мантиссы С, которая поступает на выходблока 4.Аналогично узлу сдвига мантиссы А30 функционирует узел сдвига мантиссы В, Наего выходах формируется мантисса О разрядностью и - 1, поступающая на выходблока 4.Мантиссы С и О поступают на вход бло 35 ка 5, На чертеже 3 показана функциональная схема блока 5, гдево 1 - 1-й разряд мантиссы О;ваап+1 - (и + 1)-й разряд мантиссы О;вз 1/1 - 1-й разряд мантиссы Я первой40 эаготавливаемой суммы;вягп+г/1 - (2 и + 2)-й разряд мантиссы Япервой эаготавливаемой суммы;вя 1/к+г -1-й разряд мантиссы Я (К+ 2)-йзаготавливаемой суммы;45 . вЯпги+г - (2 и + 2)-й разряд мантиссы Я(К+ 2)-й заготавливаемой суммы,Блок 5 работает следующим образом.На сумматорах 1 - К/2+ 1 (где К = и+ 1)происходит заготовка (К/2 + 1) 2 К-разрядных сумм Я 1, Яг, , Як/г+ 1 при условии, чтомантисса О остается неподвижной, а мантисса С последовательно сдвигается на дваразряда: О, 2, 4, К разрядов,На сумматорах К/2 + 2 - К + 2 п роисходит заготовка (К/2 + 1) 2 К-разрядных сумм Яка + г, Яка + 3, , Як+ г при условии. что мантисса С остается неподвижной, а мантисса О последовательно сдвигается на два разряда: О, 2, 4, К разрядов.На выход блока 5 одновременно поступают 2 К-разрядные суммь, 31, 52, Яэ, , Як+ 2Таким образом, блок 5 заготавливает суммы мантисс С и О в количестве К+ 2, где К= и+1.Прямое и инверсное значения знака выравнивающей разности и старшие разряды (без младшего) модуля выравнивающей разности поступают на управляющие входы блока 6. К+ 2) предварительные суммы поступают на информационные входы блока 6.Блок 6 включает 2 К отдельных, идентичных по структуре, коммутаторов типа мультиплексор, В общем случае каждый нестробируемый коммутатор имеет 2 Е +входов (Е прямых и Е обратных входных переменных, с помощью которых формируется адрес входного канала, и .= 2 канальных входов при полной дешифрации входных переменных) и один выход выходнойканал), на котором появляется сигнал с выбранного входного канала. Структура данного коммутатора может быть реализована на элементе; (Е+ 1)И - 1 ИЛИ.Для стробирования коммутатора необходимо в каждую схему И добавить еще по одному входу,8 блоке 6 происходит выбор нужной предварительной суммы следующим образом; при ХУ выбирается результат из сформированньх предварительных сумм, где мантисса О сдвигается относительно мантиссы С, при ХУ выбирается результат иэ сформированных предварительных сумм, где мантисса С сдвигается относительно мантиссы О, Конкретный результат выбора зависит от величины модуля выравнивающей разности, показывающей на сколько разрядов одна мантисса сдвинута относительно другой,Выбранная предварительная сумма мантисс с выхода блока 6 поступает на входы разрядов мантиссы блока 7, большая экспонента поступает на входы разрядов экспоненты блока 7. В блоке 7 происходит коррекция сумм мантисс и экспонент во избежание переполнения.Результат операции передается на выход устройства и может быть загружен в один из регистров 1 или 2 для осуществления конвейерной обработки, если один ре 5 10 15 20 30 35 40 45 50 зультат используется в качестве операнда для следующей операции.В заявляемое устройство регистры первого и второго слагаемых, блок сравнения экспонент, блок сдвига, блок селекции и передачи внесены иэ прототипа беэ изменения их функционального назначения.Па ссавнению с прототипом заявляемое устройство дополнительно содержит блок коммутаторов, Кроме тога, блок сложения ссдержит К+ 2) 2 К-разрядных сумматора, где К.= и + 1, и - разрядность мантисс слагаемьх. Именно это усложнение в совокупности с введенными новыми связями позволяет получить предложенному устройству псеимущества в быстродействии,Фасмула изобретения Устройства для суммирования чисел в дополнительном коде с плавающей запятой, содержащее регистры первого и второго слагаемых, блок сравнения экспонент, блок сдвига, блок сложения, блок селекции и передачи причем выходы разрядов экспонент регистссв первого и второго слагаемых соединены с первым А вторым.входами блока сравнения экспонент, выход которого соединен с входом управления сдвигом блока сдвига, вь.ход котарогс соединен с входом блока сложения, выход блока селекции и передачи соединен с вьхадам устройства и с первыми входами регистров первого и второго слагаемых втссые входы которых соединены с входами слагаемых устройства, а т л и: а ю щ е е с я тем, что, с целью повышения быстродействия, устройство содержит блок коммутаторов, блок сложения содержит К + 2) 2 К-разрядных сумматора, где К = и + 1, и - разрядность мантисс слагаемых, прием первый и второй информационные входы блока сдвига соединены с выходами разрядов мантисс регистров первого и втоссга слагаемых, въходц разрядов модуля и знака блока ссавнения экспонент соединены с управляющими входами блока коммутатора, информационные вхсдц которогс соединены с выходами блока сложения, выход блока коммутаторов соединен с информационным входом блока селекции и передачи, управляющий вход которого соединен с вьхадсм блока сравнения экспонент.1833864 оставитель О.Паули ехред М.Моргентал Редакто орректор М,Тка изводственно-издательский комбинат "Патент", г, Ужгород, ул.Гагар з 2686 Тираж ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб., 4/5

СмотретьЗаявка

4913672, 20.02.1991

ОДЕССКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ДРОЗД АЛЕКСАНДР ВАЛЕНТИНОВИЧ, ПАУЛИН ОЛЕГ НИКОЛАЕВИЧ, СИНЕГУБ НИКОЛАЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/50

Метки: дополнительном, запятой, коде, плавающей, суммирования, чисел

Опубликовано: 15.08.1993

Код ссылки

<a href="https://patents.su/4-1833864-ustrojjstvo-dlya-summirovaniya-chisel-v-dopolnitelnom-kode-s-plavayushhejj-zapyatojj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования чисел в дополнителььном коде с плавающей запятой</a>

Предыдущий патент: Функциональный синусный преобразователь

Следующий патент: N-разрядный параллельный сумматор

Случайный патент: Плав индулина для черной газетной краски