N-разрядный параллельный сумматор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1833865

Авторы: Гроль, Петлин, Романкевич

Текст

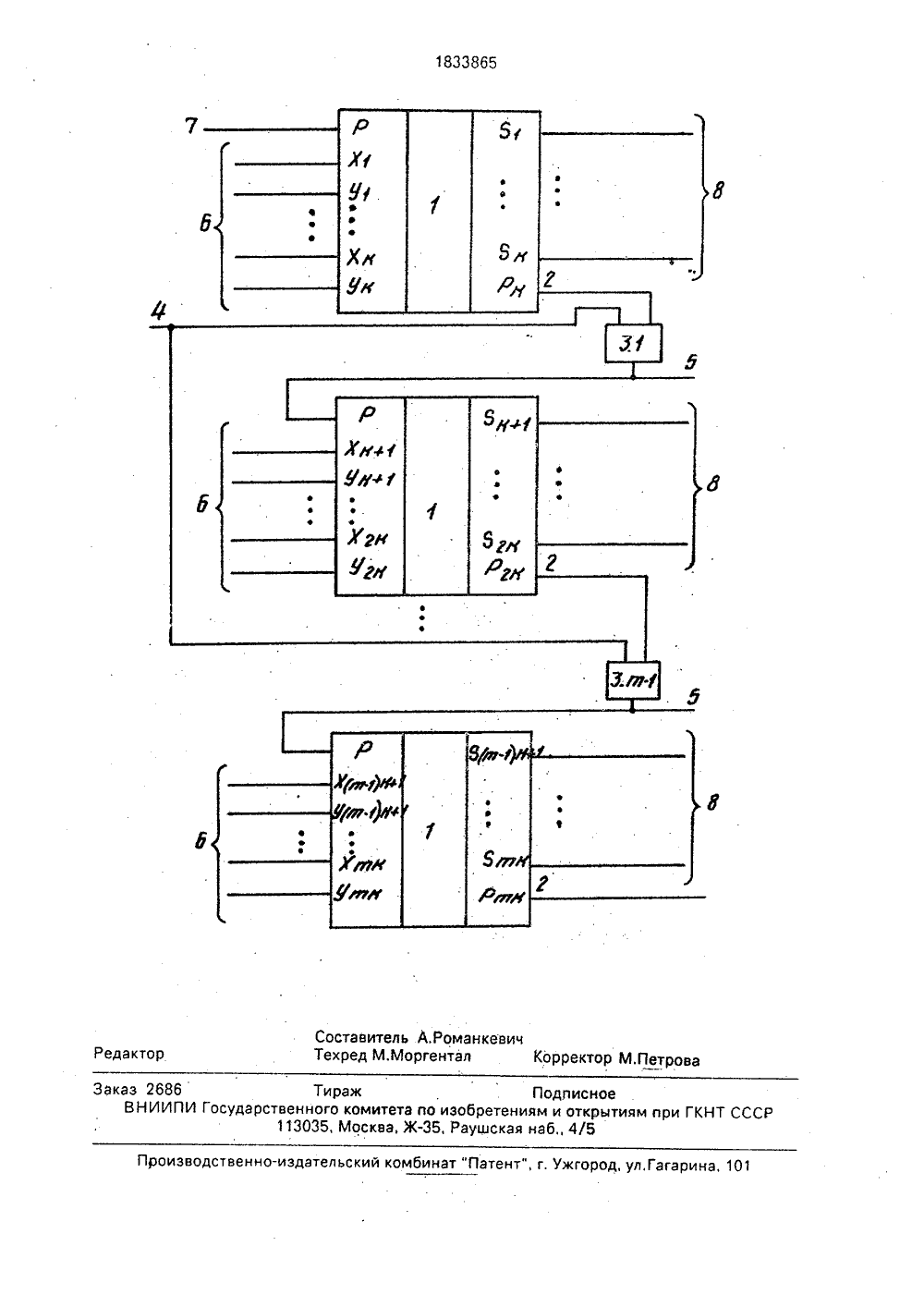

(51 ЕНТНОЕ ГОСУДАРСТВЕННО ВЕДОМСТВО ССС (ГОСПАТЕНТ ССС т.,:ц 0303 ЕЛЬСТВ ческий институт им. рьской социалистиИСАНИЕ ИЗ АВТОРСКОМУ СВ(71) Киевский политех50-летия Великой Октческой революции(56) Корнейчук В,И.,шинский Ю.Н. Вычисна микросхемах, Спрка, 1986, рис. 2.19 в, стКорнейчук В,И.,шинский Ю.Н. Вычисна микросхемах, Спрка, 1986, рис. 2,19 б, ст В.В.Гроль и О.А.ПетТарасенко В.П., Миительные устройства авочник, Киев, Технир, 245.Тарасенко В.П., Милительные устройства авочник, Киев, Технир. 245. 54) М-РАЗРЯДНЫЙ ПАРАЛЛЕЛЬНЬУММАТОР Изобретение относится к области автоматики и вычислительной техники и может быть эффективно использовано при организации псевдослучайного тестирования многоразрядных суммирующих схем,Целью изобретения является уменьшение длительности интервала времени псевдоисчерпывающего тестирования параллельного двоичного, сумматора.На чертеже представлена структура йразрядного параллельного сумматора., й-разрядный параллельный двоичный сумматор содержит группу из пй-разрядных двоичных сумматоров 1 (й Гп М), выход 2 переноса каждого из которых (кроме в-го сумматора 1) подключен к первому входу(57) Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении легко тестируемых многоразрядных суммирующих схем, Целью изобретения является уменьшение длительности псевдоисчерпывающего тестирования параллельного сумматора, йразрядный параллельный сумматор содержит пй-разрядных (КМ) сумматоров 1, выходы 2 переноса сумматоров, группу из (а - 1) двухвходовых сумматоров 3 по модулю два, тестовый вход 4 сумматора, тестовые выходы.5, входы 6 суммирования операндов, вход 7 переноса, выходы 8 суммы. Й-разрядный параллельный сумматор позволяет сократить время контроля суммирующих схем псевдослучайными наборами и может быть эффективно использован для построения контроле-.пригодных цифровых блоков. 1 ил,соответствующего двухвходового сумматора 3 по модулю два группы. Второй вход каждого из сумматоров 3 группы связан с тестовым входам 4 пврвллельного сумматора. При этом выход 5 1-го ( = 1, гп - 1) сумматора 3 группц из (щ - 1) двухвходовых сумматоров 3 по модулю два подсоединен одновременно к входу переноса ( + 1)-го сумматора 1 группы и к соответствующему тестовому выходу 5 параллельного сумматора. Входы 6 каждого из сумматоров 1 группы являются входами суммирования операндов. Вход 7 первого сумматора 1 группы является входом суммирования внешнего переноса Й-разрядного параллельного сумматора, Выходы 8 каждого из сумматоров 1группы являются выходами суммы И-разрядного параллельного сумматора,Предлагаемый сумматор функционирует в двух режимах; первый - системный режим (выполнение функции суммирования системных операндов), второй - тестовый режим (проведение проверки правильности функционирования Й-разрядного параллельного сумматора).Рассмотрим работу И-разрядного параллельного сумматора в системном режиме. На входе 4 оператором с пульта управления устанавливается потенциал, соответствующий уровню логического нуля. При этом сум латоры 3 группы выполняют/ функции повторителей сигналов с выходов 2 соответствующих сумматоров 1 группы. На входы б параллельного сумматора поступают И-разрядные (Й = гп к) двоичные операнды, а на выходах 8 формируется й-разрядная сумма (на выходе 2 последнего сумматора 1 группы формируется сигнал переноса). Выходы 5 И-разрядного параллель- нага сумматора не используются как информационные.В тестовом режиме на входы 4, б и 7 й-разрядного параллельного сумматора поступают стимулирующие воздействия с выходов генератора псевдослучайных последовательностей, а выходы 5, 8 и 2 под. ключаются к входам многоканального сигнатурного анализатора. В результате при проведении псевдослучайного тестирования проверка Й-разрядного параллельного сумматора сводится к параллельной и независимой проверке пй-разрядных двоичных сумматоров 1, что уменьшает время псевдо-. исчерпывающего тестирования М-разрядного параллельного сумматора, Параллельная и независимая проверка пйразрядных сумматоров 1 обеспечивается следующим свойством сумматора по моду,лю два; при подаче на один из входов двухвходового сумматора 3 по модулю два псевдослучайной последовательности (т.е. последовательности двоичных сигналов с вероятностью появления Рпсп 0,5 единичного (нулевого) сигнала) вероятность появления единичного (нулевого) сигнала на выходе сумматора по модулю два будет также равна 0,5;=Р +Р -2 Р Р,где Рсм 2, Рпсп, Рс - вероятности появления единичного сигнала на выходе двухвходового сумматора по модулю два, выходе генератора псевдослучайных последовательностей и в системной последовательности сигналов, поступающих на второй входдвухвходового сумматора по модулю два втестовом режиме, соответственно.5 Так как Рпсп = 0,5, то Рсмг "0,5++Рс - 2 05 Рс -05Следствие: сигналы на выходе сумматора по модулю два являются статистическинезависимыми ог системных сигналов приподаче на один из его входов псевдослучайной последовательности,Таким образом, технико-экономическаяэффективность заявляемого Й-разрядногопараллельного сумматора по сравнению с15 прототипом определяется уменьшениемдлительности псевдоисчерпывающего тестирования за счет того, что при проведениипроцедуры псевдослучайного тестированияпроверяемый параллельный сумматор раз 20 бивается на группу двоичных сумматоровменьшей разрядности, тестируемых параллельно и независимо друг от друга.С наибольшей эффективностью можноиспользовать заявляемый М-разрядный параллельный сумматор для организации самотестирования комбинационных схем,входящих в состав БИС и СБИС, где наибольшее распространение нашли методыкомпактного тестирования,30 Формула изобретенияИ-разрядный параллельный сумматор,содержащий группу из т К-разрядных двоичных сумматоров (причем М = щ К), первыйи второй информационные входы которых35 соединены с входами соответствующих разрядов первого и второго слагаемого сумматора, выходы результата которогосоединены с выходами суммы всех К-разрядных двоичных сумматоров группы и переноса т-го К-разрядного двоичногосумматора группы, вход переноса первогоК-разрядного двоичного сумматора группысоединен с входом переноса сумматора, о тл и ч а ю щ и й с я тем, что, с целью уменьшения длительности псевдоисчерпывающего тестирования, сумматор содержит группусумматоров по модулю два, причем выход1-го сумматора по модулю два (где = 1, 2, .,гп - 1) соединен с входом переноса ( + 1)-гоК-разрядного двоичного сумматора группыи с 1-м тестовым выходом сумматора, выходпереноса 1-го К-разрядного двоичного сумматора группы соединен с первым входом1-го сумматора по модулю два группы, второй вход которого соединен с тестовым входом сумматора.1833865 Составитель А.Романкевич еда ктор Техред М.Моргентал Корректор М.ПетроваПроизводс каз 2686 ВНИИПИ Госуда Тираж Подписноевенного комитета по изобретениям и открытиям при ГКНТ 113035, Москва, Ж, Раушская наб 4/5 издательский комбинат "Патент", г. Ужгород, ул,Гагарина,

СмотретьЗаявка

4929201, 18.04.1991

КИЕВСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

РОМАНКЕВИЧ АЛЕКСЕЙ МИХАЙЛОВИЧ, ГРОЛЬ ВЛАДИМИР ВАСИЛЬЕВИЧ, ПЕТЛИН ОЛЕГ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 11/26, G06F 7/50

Метки: n-разрядный, параллельный, сумматор

Опубликовано: 15.08.1993

Код ссылки

<a href="https://patents.su/3-1833865-n-razryadnyjj-parallelnyjj-summator.html" target="_blank" rel="follow" title="База патентов СССР">N-разрядный параллельный сумматор</a>

Предыдущий патент: Устройство для суммирования чисел в дополнителььном коде с плавающей запятой

Следующий патент: Устройство для умножения

Случайный патент: Шихтованный сердечник статора электрической машины