Запоминающее устройство с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

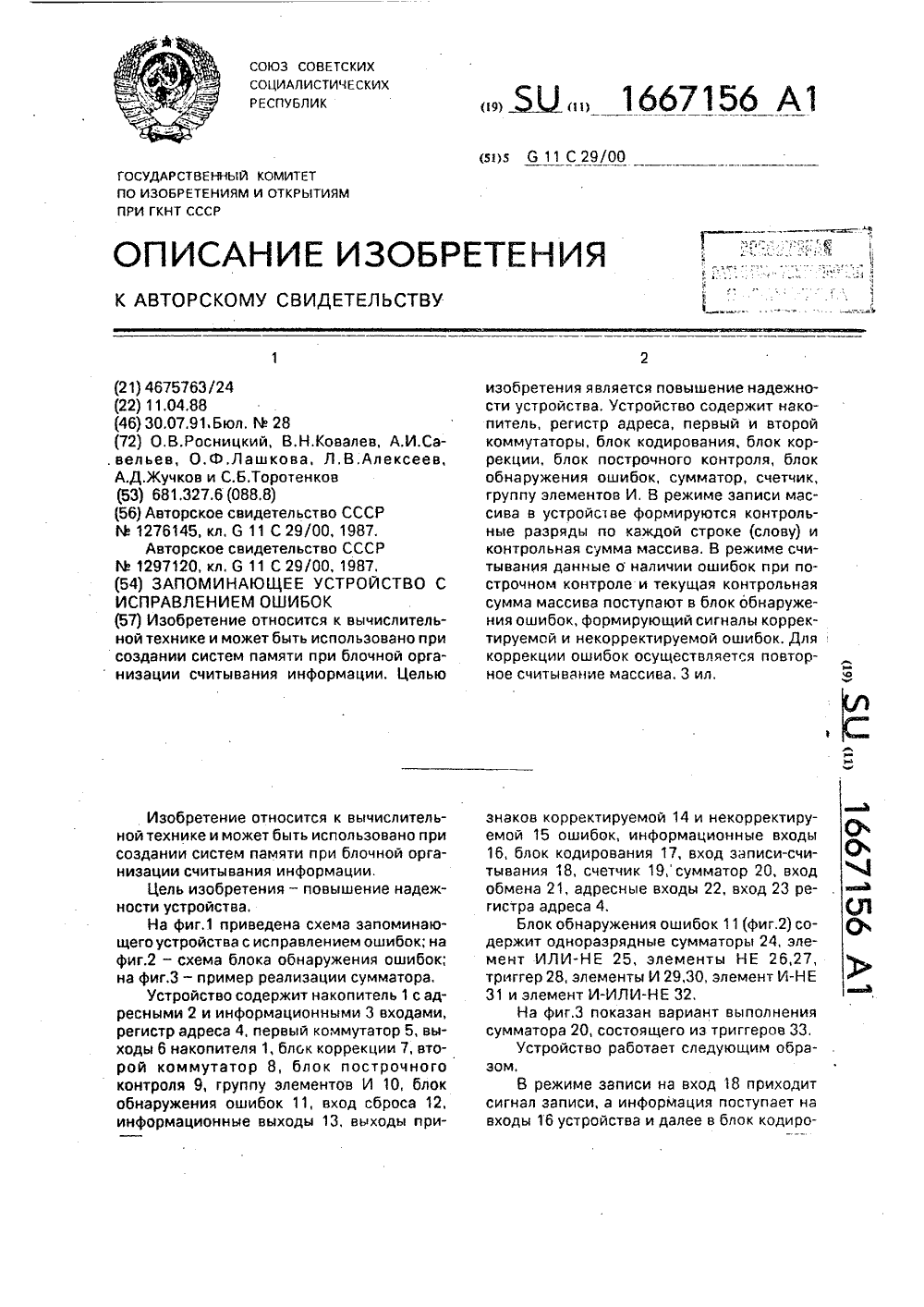

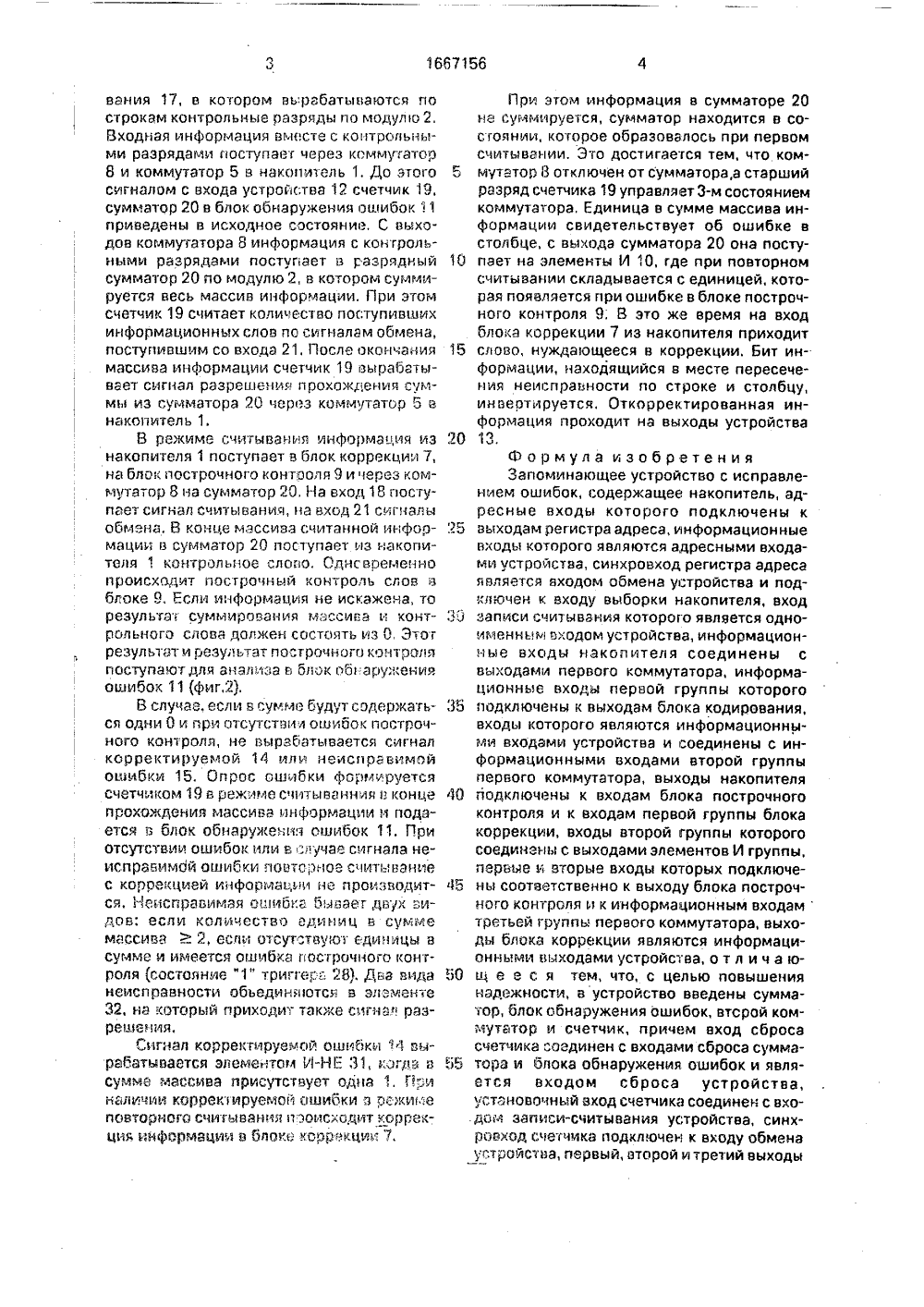

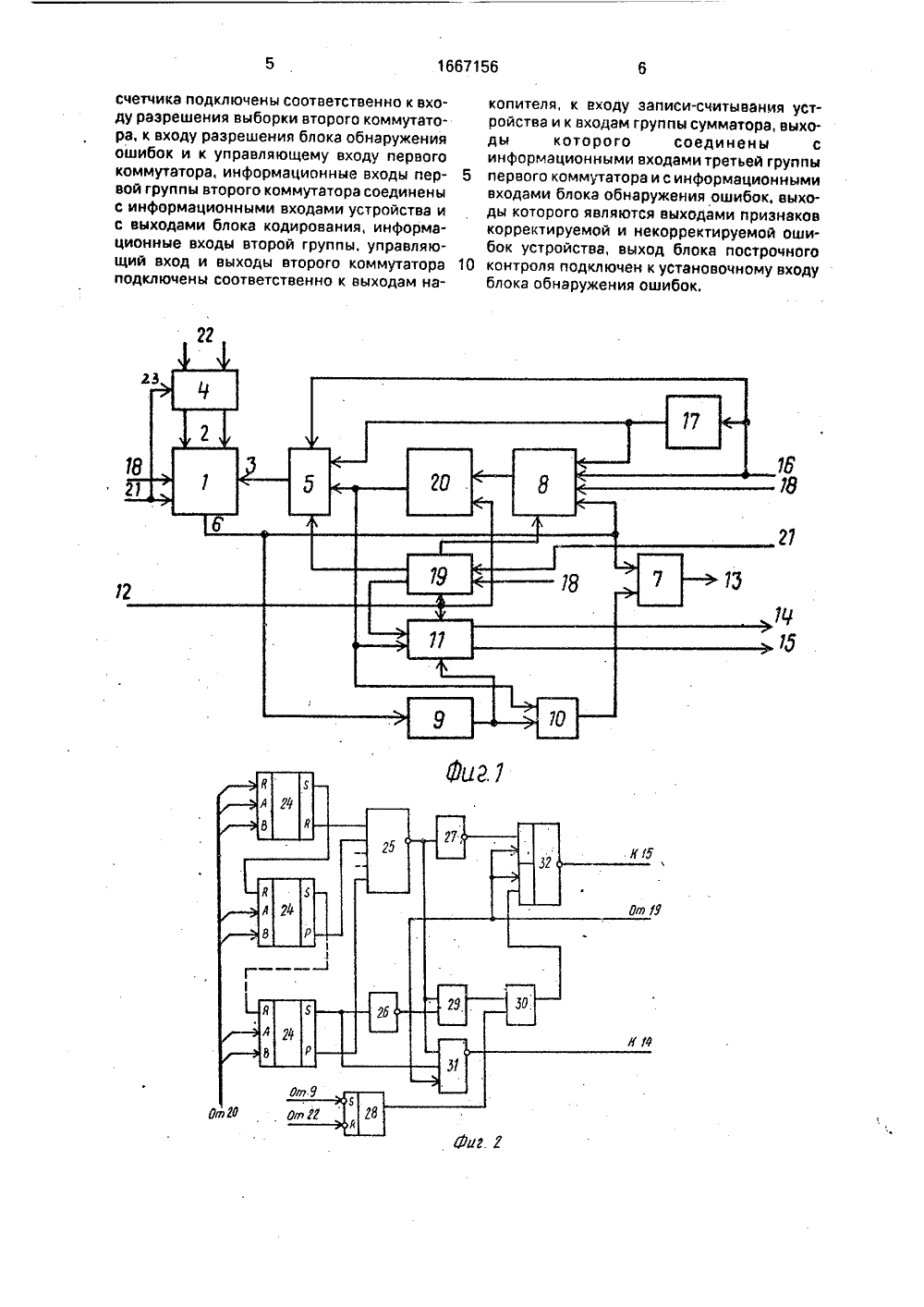

(19) (11) 7156 А 1 я)5 С 11 С 29/00 АНИЕ ИЗОБРЕТЕНИЯ ОСУДАРСТВЕННЫЙ КОМИТЕТО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМРИ ГКНТ СССР АВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Авторское свидетельство СССРВ 1276145, кл, 0 11 С 29/00, 1987,Авторское свидетельство СССРМ 1297120, кл, 6 11 С 29/00, 1987,(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО СИСПРАВЛЕНИЕМ ОШИБОК(57) Изобретение относится к вычислительной технике и может быть использовано присоздании систем памяти при блочной организации считывания информации, Целью Изобретение относится к вычислительной технике и может быть использовано при создании систем памяти при блочной организации считывания информации.Цель изобретения - повышение надежности устройства.На фиг.1 приведена схема запоминающего устройства с исправлением ошибок; на фиг.2 - схема блока обнаружения ошибок; на фиг.З - пример реализации сумматора,Устройство содержит накопитель 1 с адресными 2 и информационными 3 входами, регистр адреса 4, первый коммутатор 5, выходы 6 накопителя 1, блок коррекции 7, второй коммутатор 8, блок построчного контроля 9, группу элементов И 10, блок обнаружения ошибок 11, вход сброса 12, информационные выходы 13, выходы приизобретения является повышение надежности устройства. Устройство содержит накопитель, регистр адреса, первый и второй коммутаторы, блок кодирования, блок коррекции, блок построчного контроля, блок обнаружения ошибок, сумматор, счетчик, группу элементов И. В режиме записи массива в устройс 1 ве формируются контрольные разряды по каждой строке (слову) и контрольная сумма массива, В режиме считывания данные о наличии ошибок при построчном контроле и текущая контрольная сумма массива поступают в блок обнаружения ошибок, формирующий сигналы корректируемой и некорректируемой ошибок. Для коррекции ошибок осуществляется повторное считывание массива. 3 ил. знаков корректируемой 14 и некорректируемой 15 ошибок, информационные входы 16, блок кодирования 17, вход записи-считывания 18, счетчик 19,сумматор 20, вход обмена 21, адресные входы 22, вход 23 регистра адреса 4,Блок обнаружения ошибок 11 (фиг.2) содержит одноразрядные сумматоры 24, элемент ИЛИ-НЕ 25, элементы НЕ 26,27, триггер 28, элементы И 29,30, элемент И-НЕ 31 и элемент И-ИЛИ-НЕ 32.На фиг.З показан вариант выполнения сумматора 20, состоящего иэ триггеров ЗЗ,Устройство работает следующим образом.В режиме записи на вход 18 приходит сигнал записи, а информация поступает на входы 16 устройства и далее в блок кодирования 17, В котором Вьрэбатываются по строкам контрОльные разряды по модулю 2, Входная информация вместе с контрольными разрядами поступает через коммутатор 8 и коммутатор 5 в накопитель 1. До этага сигналам с входа устройства 12 счетчик 19, сумматор 20 в блок обнаружения ошибок 11 приведены в исходное состояние, С Выходов коммутатора 8 информация с контрольными разрядами поступает В разрядный сумматор 20 по модулю 2, В катарам суммируется весь массив информации. При этом счетчик 19 считает Колиество поступивших информационных слов па сигналам обмена, поступившим со входа 21, После окончания массива информации счетчик 19 Вырабатывает сигнал разрешения прохождения суммьг из сумматора 20 через коммутатор 5 в накопитель 1.В ре)киме очигывэния инфо)мая из накопителя 1 поступает В блок коррекции 7, нэ блок построчного контаоля 9 и через коммутатор 8 на сумматор 20, На вход 18 гюступэет сигнал считьвания, на Вход 21 сигналы обмена. В конце массива считанной информации В сумматор 20 поступает из накопителя 1 контрольное слово. Однсвременно происходит построчный контроль слов В блоке 9, Если информация не искажена, то результэ суммирования массива и конт" рольнага слава должен состоять из О, Эта г резуль) эт и результат построчного кон) роля поступают для анэли.а В блок аб аружения ошибок 11 (фиг,2).В случае, если В сумме будут с одер)каться одни О и при отсутствии ошибок построчного контроля, не Вырабатывается сигнал корректируемай 14 или неисправимой )шибки 15 Опрос ашгбки фогмируется счетчикам 19 в режиме счгтывэнния В конце прохОждения массива гнфармэции и падэется В блок Обнаружения ащфок 11. При отсутствии ошибок или в .;учае сигнала неиспрэвимсгй ошибки повто,)ое считывание С КООРЕкЦИЕИ ИгфаамаЬ 1 И Не ПРОИ,)ВОЦИТ- ся, Неиспрэв 4 мэя а 1 и 1 О;э бываег Двух Видав; 8 сли кОличестВО едииц В сумме мэссиВВ2 если Отсут"ТВ 1 ют ециницы в сумме и имеется ошибка Осгрочного контроля состояние "1" трипера 261, Два Вида неисправности ОбьеДинягатся В элзм 8 нте 32, нэ катарьЙ приходит тэкх(с сигнал раэрешеия.игЯал корректируемггй Огрбкд 4 Вырэбагцвается элеме том И-НЕ 31, когда В сумме массива присутствует одна 1, П:,и наличии коррекгируемо) сшибки В 8)киье пав горного считывания пс)оисходит каррекЦия информации В блоке ка)р;кции 10 15 20 25 :;О 35 40 45 50 55 При этом информация в сумматоре 20 не суммируется, сумматор находится в состоянии, которое образовалось при первом считывании, Это достигается тем, что коммутатор 8 отключен от сумматора,а старший разряд счетчика 19 управляет 3-м состоянием коммутатора, Единица в сумме массива информации свидетельствует об ошибке в столбце, с выхода сумматора 20 она поступает на элементы И 10, где при повторном считывании складывается с единицей, которая появляется при ошибке в блоке построчного контроля 9; В это же время на вход блока коррекции 7 из накопителя приходит слово, нуждающееся в ко)рекции. Бит информации, находящийся в месте пересечения неисправности по строке и столбцу, инвеотируется, Откорректированная информация проходит на выходы устройства 1 ф)Формула изобретения Запоминакнцее устройство с исправлением ошибок, содержащее накопитель, адресные входы которого подключены к Выходам регистра адреса, информационные входы которого являются адресными входами устройства, синхровход регистра адреса является входом обмена устройства и подключен к входу выборки накопителя, вход записи считывания которого явлвется одноименным Входам устройства, информационные входы накопителя соединены с выходами первого коммутатора, информационные входы первой группы которого подключены к выходам блока кодирования, входы которого являются информационными входами устройства и соединены с информационными входами второй группы первого коммутатора, выходы накопителя подключены к входам блока построчного контроля и к входам первой группы блока коррекции, входы второй группы которого соединены с выходами элементов И группы, первыевторые входы которых подключены соответственно к выходу блока построчного контроля и к информационным входамтретьей группы первого коммутатора, вцходц блока коррекции являются информационными выходами устройства, о т л и ч а ющ е е с я тем, что, с целью повышения надежности, в устройство введены сумматор, блок обнаружения ошибок, второй коммутатор и счетчик, причем вход сброса счетчика соединен с входами сброса сумматора и блока обнаружения ошибок и является входом сброса устройства, установочный вход счетчика соединен с вхо.дам записи-считывания устройства, синхровход счетчика подключен к входу обмена устрОйства, п 8 рВый, Второй и третий выходысчетчика подключены соответственно к входу разрешения выборки второго коммутатора, к входу разрешения блока обнаружения ошибок и к управляющему входу первого коммутатора, информационные входы первой группы второго коммутатора соединены с информационными входами устройства и с выходами блока кодирования, информационные входы второй группы, управляющий вход и выходы второго коммутатора подключены соответственно к выходам накопителя, к входу записи-считывания устоойства и к входам группы сумматора, выходы которого соединены с информационными входами третьей группы 5 первого коммутатора и с информационнымивходами блока обнаружения ошибок, выходы которого являются выходами признаков корректируемой и некорректируемой ошибок устройства, выход блока построчного 10 контроля подключен к установочному входублока обнаружения ошибок.Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 1 Заказ 2529 ВНИИПИ Государ Тираж 352 Подписноенного комитета по изобретениям и открцтиям при ГКНТ СССР 3035, Москва, К, Раушская наб., 4/5

СмотретьЗаявка

4675763, 11.04.1989

ПРЕДПРИЯТИЕ ПЯ Г-4677, МОСКОВСКИЙ ТЕКСТИЛЬНОЙ ИНСТИТУТ ИМ. А. Н. КОСЫГИНА

РОСНИЦКИЙ ОЛЕГ ВЛАДИМИРОВИЧ, КОВАЛЕВ ВЛАДИМИР НИКОЛАЕВИЧ, САВЕЛЬЕВ АНАТОЛИЙ ИВАНОВИЧ, ЛАШКОВА ОЛЬГА ФЕДОРОВНА, АЛЕКСЕЕВ ЛЕВ ВЛАДИМИРОВИЧ, ЖУЧКОВ АЛЕКСАНДР ДМИТРИЕВИЧ, ТОРОТЕНКОВ СЕРГЕЙ БОРИСОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, ошибок

Опубликовано: 30.07.1991

Код ссылки

<a href="https://patents.su/4-1667156-zapominayushhee-ustrojjstvo-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением ошибок</a>

Предыдущий патент: Ассоциативное оперативное запоминающее устройство

Следующий патент: Устройство для контроля и коррекции адресных сигналов памяти последовательного действия

Случайный патент: Устройство для отбора проб жидкости