Процессор для мультипроцессорной системы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

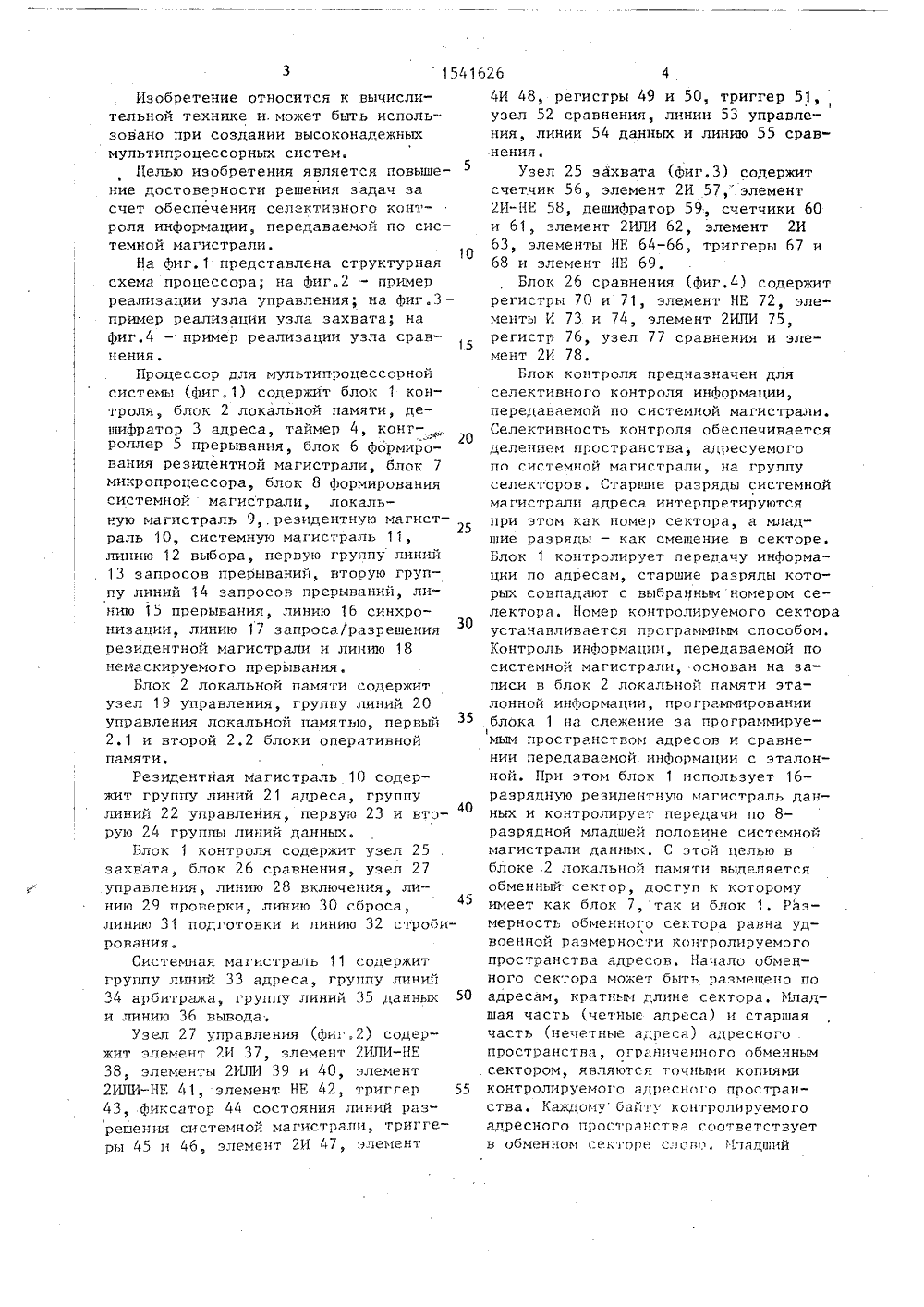

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН О 1541 1)5 с Р 151 ОПИСАНИЕ ИЗОБРЕТЕН льти обре верно печен мации магие что в 7 мпк преры з иден миров каль троля блока 4 ил. СЬ ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМПРИ ГННТ СССР К АВТОРСКОМУ СВИДЕТЕЛЬ(56) Авторское свидетельство СССРР 1295410, кл, С 06 Р 15/16, 1985.Модуль центрального процессораСМ 1810. 2204. Техническое описаниеи инструкция по зксплуатации3,057.130 ТО.(57) Изобретение относится к вычислительной технике и может быть испо при создании высоконадежных процессорных систем. Целью тения является повышение досто ти решения задач за счет обеся селективного контроля инфорпередаваемой по Системной рали, Цель достигается тем, процессор, состоящий из блока опроцессоров, дешиФратора 3таймера 4, контроллера 5 алия, блока 6 Аормирования реной магистрали, блока 8 Форния системной магистрали, лой памяти 2, введен блок 1 консостоящий из узла захвата, сравнения и узла управления.Изобретение относится к вычислительной технике и.может быть использовано при создании высоконадежныхмультипроцессорных систем.Целью изобретения является повышение достоверности решения задач засчет обеспечения селективного контроля информации, передаваемой по системкой магистрали.На фиг. 1 представлена структурнаясхема процессора; на фиг.2 - примерреализации узла управления; на фиг.З -пример реализации узла захвата; нафиг.4 - пример реализации узла срав 15нения.Процессор для мультипроцессорнойсистемы (фиг,1) содержит блок 1 контроля, блок 2 локальной памяти, дешифратор 3 адреса, таймер 4, конт-"ф" 20роллер 5 прерывания, блок б формирования резидентной магистрали, блок 7микропроцессора, блок 8 формированиясистемной магистрали, локальную магистраль 9,.резидентную магистраль 10, системную магистраль 11,линию 12 выбора, первую группулиний13 запросов прерываний, вторую группу линий 14 запросов прерываний, линию 15 прерывания, линию 16 синхронизации, линию 17 запроса/разрешениярезидентной магистрали и линию 18немаскируемого прерывания.Блок 2 локальной памяти содержитузел 19 управления, группу линий 20управления локальной памятью, первый2,1 и второй 2.2 блоки оперативнойпамяти.Резидентная магистраль 10 содержит группу линий 21 адреса, группулиний 22 управления, первую 23 и вто 40рую 24 группы линий данных,Блок 1 контроля содержит узел 25захвата, блок 26 сравнения, узел 27управления, линию 28 включения, линию 29 проверки, линию 30 сброса,линио 31 подготовки и. линию 32 стробирования.Системная магистраль 11 содержитгруппу линий 33 адреса, группу линий34 арбитража, группу линий 35 данных 50и линию 36 вывода.Узел 27 управления (фиг.2) содержит элемент 2 И 37, элемент 2 ИЛИ-НЕ38, элементы 2 ИЛИ 39 и 40, элемент2 ИЛИ-НЕ 41, элемент НЕ 42, триггер 5543, фиксатор 44 состояния линий разрешения системной магистрали, триггеры 45 и 46, элемент 2 И 47, элемент 4 И 48, регистры 49 и 50, триггер 51,узел 52 сравнения, линии 53 управления, линии 54 данных и линию 55 сравнения,Узел 25 захвата (фиг,З) содержитсчетчик 56, элемент 2 И 57,.элемент2 И-НЕ 58, дешифратор 59, счетчики 60и 61, элемент 2 ИЛИ 62, элемент 2 И63, элементы НЕ 64-66, триггеры 67 и68 и элемент НЕ 69.Блок 26 сравнения (фиг.4) содержитрегистры 70 и 71, элемент НЕ 72, элементы И 73 и 74, элемент 2 ИЛИ 75,регистр 76, узел 77 сравнения и элемент 2 И 78.Блок контроля предназначен дляселективного контроля информации,передаваемой по системной магистрали.Селективность контроля обеспечиваетсяделением пространства, адресуемогопо системной магистрали, на группуселекторов. Старшие разряды системноймагистрали адреса интерпретируютсяпри этом как номер сектора, а младшие разряды - как смещение в секторе,Блок 1 контролирует передачу информации по адресам, старшие разряды которых совпадают с выбракным нокером селектора. Номер контролируемого сектораустанавливается программным способом.Контроль информации, передаваемой посистемной магистрали, основан на записи в блок 2 локальной памяти эталонной информации, программированииблока 1 на слежение за программируемым пространством адресов и сравнении передаваемой информации с эталонной. При этом блок 1 использует 16 разрядную резидентную магистраль данных и контролирует передачи по 8 разряцной младшей половине системноймагистрали данных, С этой целью вблоке .2 локальной памяти выделяетсяобменный сектор, доступ к которомуимеет как блок 7, так и блок 1. Размерность обменного сектора равна удвоенной размерности контролируемогопространства адресов. Начало обменного сектора может быть размещено поадресам, кратным длине сектора, Младшая часть (четные адреса) и старшаячасть (нечетные адреса) адресногопространства, ограниченного обменньцчсектором, являются точными копиямиконтролируемого адресного пространства. Каждому байту контролируемогоадресного пространства соответствуетв обменном секторе слово. Младщийли. Блок 7 завершает текущий шинныйцикл, освобождает резидентную магистраль 10 и передает по линии 17 на/ блок 1 импульс разрешения магистрали , Импульсы запроса и разрешения блокируют обновление регистров 70и 71 блока 26 и фиксатора 44 узла 27.После этого узел 25 передает по линии 28 в блок 26 сигнал низкого уровня. Этот сигнал разрешает подключение блока 26 к резидентной магистрали. Блок 26 устанавливает на резидент" ной магистрали адрес обменного сектора блока 2 и сигналы чтения и записи. Узел 19 управления, используягруппу линий 20 управления, записывает во второй блок 2.2 памяти информацию, хранимую в регистре 71 блока26, и считывает эталонную информацию с первого блока 2.1. Считаннаяинформация по младшей половине линийданных резидентной магистрали 10 поступает в блок 26, который сравнивает считанную информацию с информацией, хранимой в регистре 71.После завершения операций записии чтения со сравнением узел 25 устанавливает сигнал высокого уровняналинии 28, отключая тем самым блок26 от резидентной магистрали, и передает по линии 17 импульс освобождения, Этот импульс разрешает блоку 7продолжить использование резидентной магистрали, В следующем такте35 узел 25 устанавливает сигнал сбросана линии 30, которым снимается блокировка регистров 70 и 71 блока 26и фиксатора 44 узла 27, Если передаваемая информация идентична эталонной,40 то операция контроля информации "прозрачна" для блока 7.При несовпадении передаваемой инФормации блок 26 сравнения устанавливает сигнал немаскируемого преры 45 вания, поступающий по линии 18 наблок 7, Этим же сигналом блокируетс я обновление фиксатора 44 узла 27.Обновление Фиксатора 44 разрешаетсяпрограммным способом,50Формула изобретения Процессор для мультипроцессорной системы, содержащий блок микропроцессора, блок формирования системной магистрали, блок формирования резидентной магистрали, контроллер прерывания, таймер, дешифратор адреса, блок локальной памяти, включающий 5 1541626 6бланк обменного сектора используетсядля хранения эталонной информации,подлежащей передаче по системной магистрали данных в область контролируемых адресов. Старший бланк обменного сектора используется для записи информации, переданной по системной магистрали данных при обращении любого процессора в область конт 10ролируемых адресов.Предполагают, что в исходном состоянии процессор выполняет задачи,не связанные с контролем информации,передаваемой по системной магистрали,а работа блока 1 запрещена.15Для контроля информации, передаваемой по системной магистрали 11,блок 7 выделяет в блоке 2 обменныйсектор, в который заносятся результаты вычислений, предназначенныедля вывода. При этом в первый блок2.1 блока 2 заносится прямое значение байта информации, а во второйблок 2.2 - инверсное. Смещение за- .писываемого слова относительногоначального адреса обменного сектора равно смещению контролируемогобайта относительно начала контролируемого сектора в.пространстве адресовсистемной магистрали, После этогоблок 7 выполняет инициализацию блока 1. Блок 7 записывает в регистр76 блока 26 базовый адрес обменногосектора блока 2 локальной памяти,а в регистры 49 и 50 узла 27 - кодразмерности контролируемого сектораи номер контролируемого секторасоответственно, Одновременно с записью номера контролируемого сек"тора разрешается работа блока 1,Блок 1 осуществляет контрольинформации, передаваемой по системной магистрали, в случае совпадениястарших разрядов системной магистрали 11 адреса с номером контролируемого сектора, хранимым в регистре50. В этом случае узел 27 вырабатывает сигнал стробирования, поступающий в узел 25 и блок 26,По сигналу стробирования в фиксаторе 44 узла 27 фиксируется состояниелинии разрешения магистрали арбитража, а в регистрах 70 и 71 блока 26 состояние системных магигтралей адреса и данных соответственно. Узел 5525 по сигналу стробирования выполняет операцию захвата резидентной магистрали, При этом узел Д 5,передаетпо линии 17 импульс запроса магистра"узел управления и два блока памяти, причем первые входы-выходы адреса данных и входы-выходы управления блока микропроцессора через локальную магистраль соединены с одноименными первыми входами блока Формирования системной магистрали и блока Формирования резидентной магистрали, вход адреса и вход управления дешифратора адреса соединены с одноименными вторыми входами-выходами Формирователя резидентной магистрали, входы-выходы адреса данных и входы-выходы управления контроллера прерывания, тай мера и локальной памяти через резидентную магистраль соединены с одноименными вторыми входами Формирователя резидентной магистрали, выход запросов прерывания таймера соединен с одноименным первым входом контроллера прерываний, выход прерывания которого соединен с одноименным входом блока микропроцессора, о т - л и ч а ю щ и й с я тем, что, с целью 2 повышения достоверности решения задач за счет обеспечения селективного контроля информации, передаваемой по системной магистрали, в него включен блок контроля, содержащий узел захвата, блок сравнения и узел управления, выход стробирования которого соединен с одноименными входами блока сравнения и узла захвата, выходы включения и проверки которого соединены с одноименными входами блока сравнения, выход немаскируемого прерывания .которого соединен с одноименными входами узла управления блокаконтроля и блока микропроцессора, выход синхронизации которого соединен с одно 40 именным входом узла захвата, входвыход запроса разрешения которогосоединен с одноименными входами-выходами блока микропроцессора и узла управления блока контроля, вторые входы-выходы адреса блока Формированиясистемной магистрали через системнуюмагистраль соединены с одноименнымипервыми входами-выходами блока сравнения и узла управления блока контро"ля и являются входами-выходами адреса1 Ьпроцессора, вторые входы-выходы данных блока формирования системной магистрали соединены через системную магистраль с одноименными первыми входами-выходами блока сравнения и являются входами-выходами данных процессора, входы-выходы запроса прерывания блока Формирования системной1магистрали через системную магистральсоединены с одноименными вторыми входами контроллера прерываний и являются входами-выходами запроса прерыванияпроцессора, входы-выходы арбитражаи вывода блока Формирования магистрали через системную магистраль соединены с одноименными входами-выходами узла управления блока контроля иявляются входами-выходами арбитражаи вывода процессора, вторые входы-выходы адреса., входы-выходы данных ивходы-выходы управления узла управления блока контроля, вторые входывыходы адреса данных и входы-выходыуправления блока сравнения, входывыходы управления узла захвата соединены через резидентную магистраль содноименными входами-выходами блокалокальной памяти и одноименными вторыми входами-выходами блока формирования резидентной магистрали,1541626 Щог,4Составитель В,Резван ктор О.Ярковецкая Техред М.Дидь 1 к Коррек черявая Тираж 566 омитета по изо осква, Б, Р Заказ 282 Подпися НИИПИ Государственного 113035, м и открьтиям при ГКНТ СССРнаб., д. 4/5 н ка роизводственно-издательский комбинат "Патент", г Ужгород, ул. Гагарина, 101

СмотретьЗаявка

4419632, 03.05.1988

ПРЕДПРИЯТИЕ ПЯ А-7240

АНТОНЮК БОРИС ВИТЕЛЬЕВИЧ, ОМЕЛЬЧУК ИГОРЬ ВЛАДИМИРОВИЧ, ПРИСЯЖНЮК ВАЛЕРИЙ НИКОЛАЕВИЧ, ТЕРЕЩЕНКО ГЕННАДИЙ ГЕОРГИЕВИЧ

МПК / Метки

МПК: G06F 15/16

Метки: мультипроцессорной, процессор, системы

Опубликовано: 07.02.1990

Код ссылки

<a href="https://patents.su/6-1541626-processor-dlya-multiprocessornojj-sistemy.html" target="_blank" rel="follow" title="База патентов СССР">Процессор для мультипроцессорной системы</a>

Предыдущий патент: Устройство для сопряжения абонента с общей магистралью

Следующий патент: Устройство для формирования последовательностей дискретно частотных сигналов

Случайный патент: Индукционная установка повышенной частоты для непрерывной варки оптического стекла