Устройство для программирования дешифратора

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

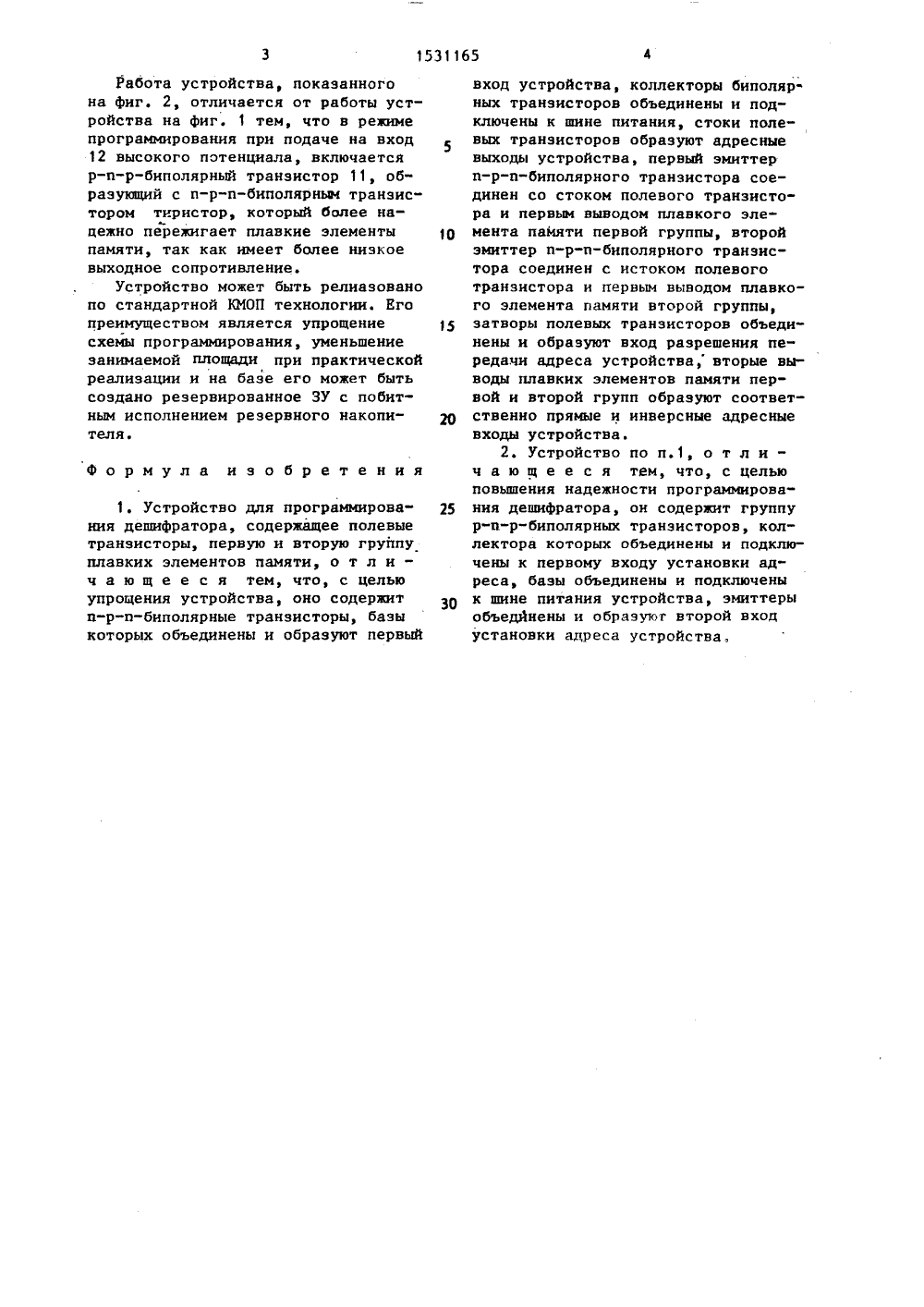

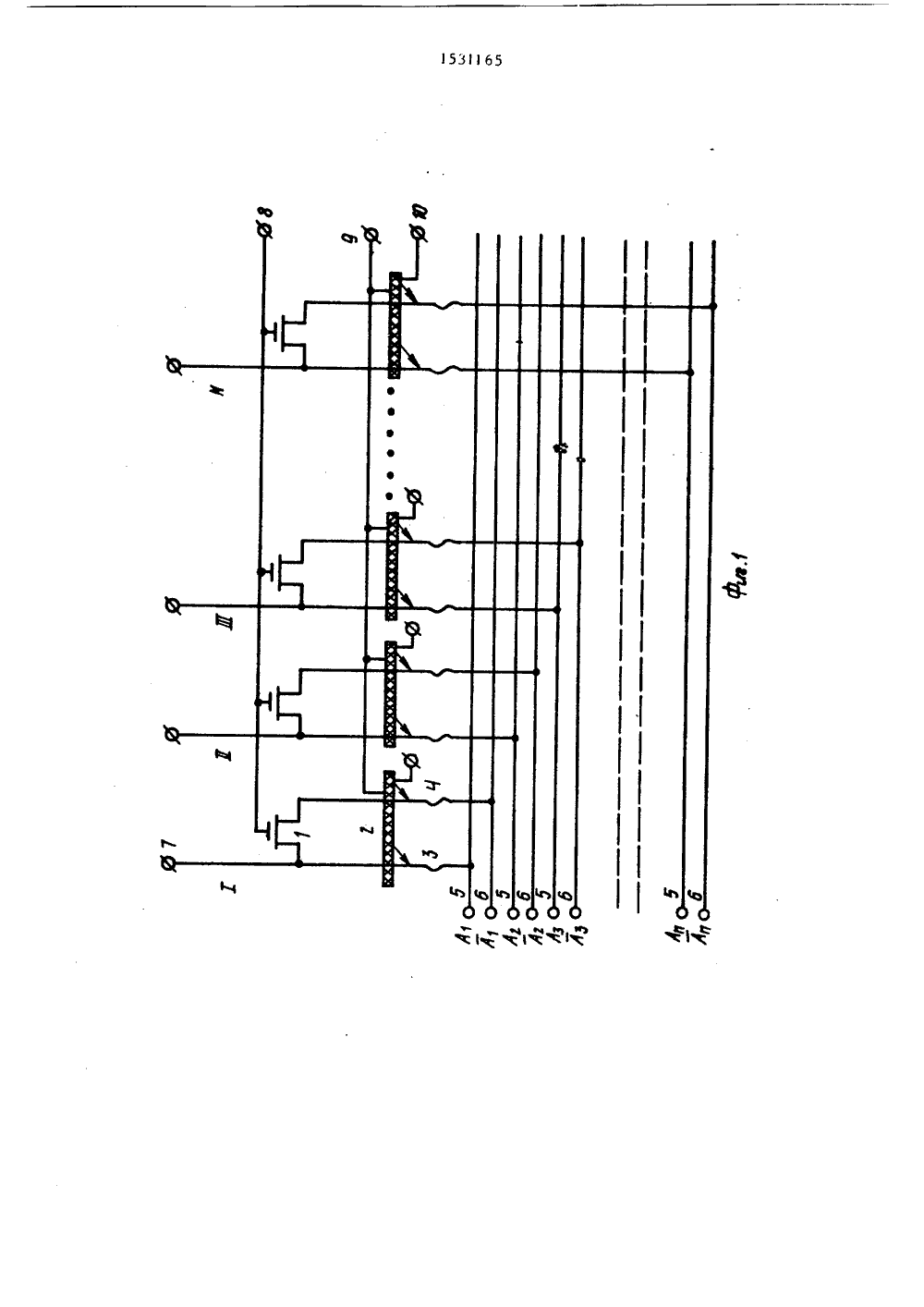

(57) Иэобретени РОГ РАМИИР О ВАНИЯ тносится к ми ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМПРИ ГННТ СССР ОПИСАНИЕ И ВТОРСКОМУ СВИДЕТЕЛЬСТВ Изобретение относится к микроэлектонике и может быть использовано при проектировании и изготовлении запоминающих устройств с резервированием.Целью изобретения является упрощение устройства.На фиг. 1 приведена электрическая схема устройства для программирования дешифратора; на фиг, 2 - то же, с дополнительным р-и-р-биполярным транзистором.Устройство (фиг, 1 и 2) содержит полевой ИДП-транзистор 1, двухэмиттерный и-р-и-биполярный транзистор 2, плавкий элемент 3 памяти первой группы, элемент 4 памяти второй группы, прямой адресный вход 5, инверсный адресный вход 6, адресный выход 7, вход 8 разрешения передачи адреса, первый вход 9 установки адреса, шину 10 питания, р-и-р-биполярный транзистор 11 и второй вход 12 установки адреса.Устройство для программирования дешифратора в режиме резервирования работает следующим образом. электронике и может бь ь использованопри проектировании и и готовлениизапоминающих устройств с резервированием. Цель изобретения - упрощениеустройства дпя программирования дешифратора. Поставленная цель достигается тем, что устройство содержити-р-и-биполярные транзисторы для пережигания плавких элементов памяти.В реюьмах записи и считывания информации используются полевые транзисторы., 1 з.,п. Ф-лы, 2 ил. При наличия на адресных входах 5 и6 кодов адреса с.трохи и столбпа дефектной ячейки памяти в виде логических "О" и "1" на вход 9 подается высокий потенциал (логическая "1"), врезультате чего включаются п-р-и-биполярные транзисторы и через их эмиттерл 1, находящиеся под воздействиемнизкого потенциала, начинает протекать ток, который иережигает соответствующие плавкие элементы памяти. Навходе 8 в режиме программированияподдерживается потенциал, выключающий полевые транзисторы 1,В режиме записи и считывания информации на вход 9 подается низкийпотенциал, в результате закрыты всеи-р-и-биполярные транзисторы 2 независимо от потенциалов на адресныхвходах. На вход 8 подается потенциал,открывающий транзисторы 1, в резуль-тате чего на адресных выходах 7 появляются сигналы, определяемые состоянием плавких элементов памяти икодом адресных входов.Работа устройства, показанного на фиг. 2, отличается от работы устройства на фиг. 1 тем, что в режиме программирования при подаче на вход 12 высокого потенциала, включается р-и-р-биполярный транзистор 11, об" разующий с п-р-и-биполярным транзистором тиристор, который более надежно пережигает плавкие элементы памяти, так как имеет более низкое выходное сопротивление.Устройство может быть релиазовано по стандартной КМОП технологии. Его преимуществом является упрощение схемы программирования, уменьшение занимаемой площади при практической реализации и на базе его может быть создано резервированное ЗУ с побитным исполнением резервного накопителя. 1 О 15 формула изобретения 1. Устройство для программирования дешифратора, содержащее полевыетранзисторы, первую и вторую группуплавких элементов памяти, о т л и -ч а ю щ е е с я тем, что, с цельюупрощения устройства, оно содержити-р-п-биполярные транзисторы, базыкоторых объединены и образуют первый вход устройства, коллекторы биполярных транзисторов объединены и подключены к шине питания, стоки полевых транзисторов образуют адресныевыходы устройства, первый эмиттери-р-и-биполярного транзистора соединен со стоком полевого транзистора и первым выводом плавкого элемента пайяти первой группы, второйэмиттер и-р-и-биполярного транзистора соединен с истоком полевоготранзистора и первым выводом плавкого элемента памяти второй группы,затворы полевых транзисторов объединены и образуют вход разрешения передали адреса устройства, вторые выводы плавких элементов памяти первой и второй групп образуют соответственно прямые и инверсные адресныевходы устройства.2. Устройство по п.1, о т л и "ч а ю щ е е с я тем, что, с цельюповышения надежности программирования дешифратора, он содержит группур-и-р-биполярных транзисторов, коллектора которых объединены и подключены к первому входу установки адреса, базы объединены и подключенык шине питания устройства, эмиттерыобъедйнены и образуот второй входустановки адреса устройства,153 1165 орректор С,дактор М. нар Заказ 7962/53 Тираж 558 ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС113035, Москва, Ж, Раушская наб д. 4/5 оизводственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарин Составител Техред М.Д Б. Венковык

СмотретьЗаявка

4359483, 28.12.1987

ПРЕДПРИЯТИЕ ПЯ В-2892

МУРАШЕВ ВИКТОР НИКОЛАЕВИЧ, ПАНКРАТОВ АЛЕКСАНДР ЛЬВОВИЧ, ЛЕОНОВ ПАВЕЛ ВАСИЛЬЕВИЧ, КОВАЛЕВ РУДОЛЬФ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G11C 11/40

Метки: дешифратора, программирования

Опубликовано: 23.12.1989

Код ссылки

<a href="https://patents.su/4-1531165-ustrojjstvo-dlya-programmirovaniya-deshifratora.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для программирования дешифратора</a>

Предыдущий патент: Полупроводниковое оперативное запоминающее устройство

Следующий патент: Многоканальный параллельный оптический преобразователь для оптоэлектронного запоминающего устройства

Случайный патент: Устройство для разогрева вязких материалов