Устройство для программирования микросхем памяти

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

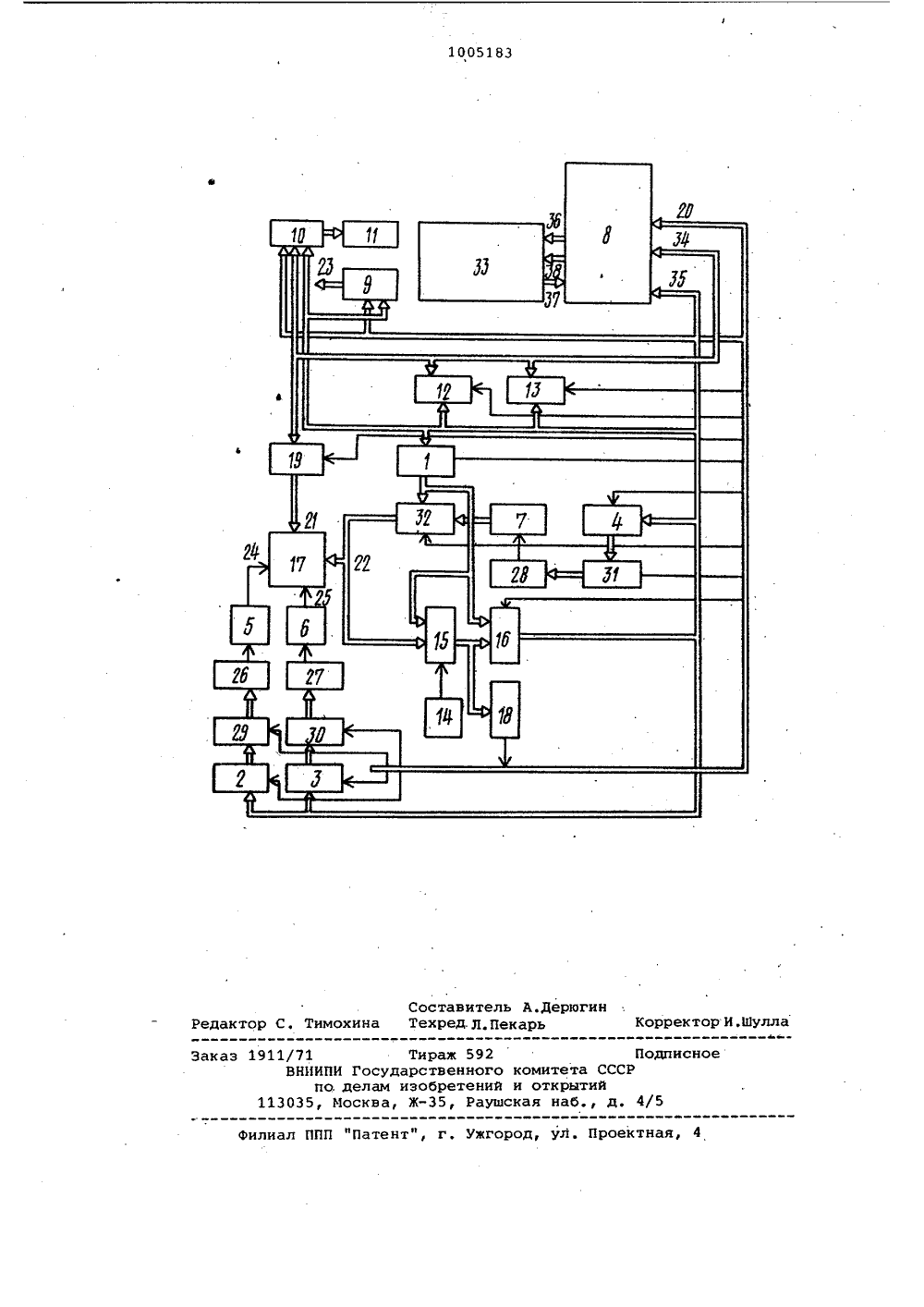

(22) Заявлено 1307.81 (21) 3317158/18-24 (31) М. КЛ. 6 11 С 7/00О. 11 С 17/00 с присоединением заявки Нов Государственный комитет СССР но делам изобретений н открытий(23) Приоритет Опубликовано 15.0333. Бюллетень Йо 10 Дата опубликования описания 15,03. 83 53) УДК 681, 327, ,бб (088.8).(72) Авторы изобретения М,Э Иванов, А.Н, Цурпал и Г.А. Бородин Московский ордена Ленина и ордена ОктябрьскоК-,РевЬМЬЦиц,.;энергетический институт3 уИзобретение относится к вычислительной технике и может быть использованопри прогваммировании репрограммируемых и однократно программируемых микросхем памяти.Известно устройство для программирования микросхем памяти, содержащее пульт управления, блок индикации, блок формирования программы программирования, таймер, блок контроля, коммутатор, усилители мощности и осуществляющее программирование информации по кодам, набираемым на пульте управления 11.Недостатками этого устройства. являются низкая производительность работы, невозможность программирования микросхем различных типов, недостаточная точность контроля параметров микросхем после программиро-. вания.Наиболее близким к предлагаемому по технической сущности и схемному решению является устройство для программирования микросхем памяти, содержащее пульт управления, блок управления, блок индикации, усилители мощности, буферные регистры, блок сравнения, регистры адреса и числа, шины управления, адресные и числбвые, блок сопряжения с внешнимиустройствами, таймер и осуществляющее ручной и автоматический вводинформации, ручное и автоматическоепрограммирование, контроль параметров запрограммированных микросхем 2).Недостатки этого устройства заключаются в следующем. Устройство непозволяет производить функциональный контроль. При программированиимикросхем различных типов необходимаперестройка блока управления н блокапитания для выработки соответствующих серий программирующих импульсов.Отсутствие перестройки приводит книзкой достоверности записи информации, Отсутствие возможности изменения лрограммы программирования,определяющее достоверность записиинформации, является основным недостатком йзвестного устройства.Целью изобретения является повышение достоверности записи информации в программируемые и репрограммируемые устройства эа счет обеспечения возможности изменения формыпрограммирующих импульсов,Указанная цель достигается тем,что устройство для программироваЗ 0 ния микросхем памяти, содержащее45 5 О 55 6 О 65 регистр числа, первый, второй и третий буферные регистры, первый, второй и третий усилители моцности,блок управления, блок сопряжения свнешними устройствами, пульт управления, блок индикации, оперативныйнакопитель, эталонный накопитель,блок задания опорных напряжений,блок компараторов, блок сравнения,блок выработки ошибки, регистр адреса, выходы которого являются ад- Оресными выходами устройства адресные выводы оперативного накопителя,эталонного накопителя, пульта управления, регистра адреса и блока управления соединены с адресными шинами,управляющие выводы регистра адреса,регистра числа, оперативного накопителя, эталонного накопителя, первого, второго и третьего буферныхрегистров, пульта управления, блокауправления, блока сопряжения с внешними устройствами, блока сравнения иблока выработки ошибки соединены сшинами управления, числовые выводырегистра числа, блока управления,оперативного накопителя, эталонногонакопителя блока сопряжения с внешними устройствами, первого,.второгои третьего буферных регистров иблока сравнения соединены с числовыми шинами, выходы первого и второго усилителей мощности являются соответственно первым и вторым программируюШими выходами устройства, входыблока выработки ошибки соединены свходами первой группы блока сравнения и выходами блока компараторов,входы первой группы которого являются числовыми выходами устройства,входы второй группы блока сравнениясоединены с выходами регистра числа 4 Ои со входами второй группы блокакомпараторов, управляюшие выводыкоторого соединены с выходами блоказадания опорных напряжений, входыблока индикации соединены с регистрирующими выходами пульта управления, выходы блока сопряжения с внешними устройствами являются входамиввода-вывода устройства, дополнительно содержит первый, второй итретий цифроаналоговые преобразователи, первый, второй и третийпромежуточные регистры, блок формирователей, блок хранения микропрограмм, адресные, числовые и управляюцие выводы которого соединеныс соответствующими шинами, выходыпервого, второго и третьего буферных регистров соединены с входамисоответствующих промежуточных регистров, выходы которых соединеныс входами соответствующих цифроаналоговых преобразователей, выходыкоторых соединены с входами соответствующих усилителей мощности,выходы третьего усилителя мощности соединены со входами первой группыблока формирователей, входы второйгруппы которого соединены с выходами регистра числа, выходы блокаформирователей соединены со входамипервой группы блока компараторов,управляющие входы первого, второгои третьего промежуточных регистрови блока формирователей соединеныс управляющими шинами.На чертеже представлена структурная схема устройства для программирования микросхем памяти.Устройство для программированиямикросхем памяти содержит регистр 1числа, первый 2, второй 3 и третий 4буферные регистры, первый 5, второй6 и третий 7 усилители мощности,блок управления 8, блок сопряженияс внешними устройствами 9, пульт управления 10, блок индикации 11,оперативный 12 и эталонный 13 накопители, блок задания опорных напряжений 14, блок компараторов 15, блоксравнения 16, разъем для подключенияпрограммируемой микросхемы 17, блоквыработки ошибки 18, регистр адреса 19, управляющие шины 20, адресные выходы устройства 21, числовыевыходы устройства 22, выходы вводавывода устройства 23, первый 24 ивторой 25 программирующие выходыустройства, первый 26, второй 27и третий 28 цифроаналоговые преобразователипервый 29, второй 30 итретий 31 промежуточные регистры,блок формирователей 32, блок храйенйямикропрограммы 33, адресные 34 и числовые 35 шины, дбполнительные адресные 36, числовые 37 и управляющие38 шины,Выходы регистра адреса 19 являются адресными выходами устройства 21, адресные выводы оперативного накопителя 12, эталонного накопителя 13, пульта управления 10,регистра адреса 19, блока управления 8 соединены. с адресными шинами 34, управляющие выводы регистра адреса 19, регистра 1 числа, оперативного накопителя 12, эталонного накопителя 13, первого 2, второго 3 и третьего 4 буферных регистров, первого 29, второго 30 и третьего 31 промежуточных регистров, блока сопряжения с внешними устройствами 9, блока сравнения 16, блока выработки ошибки 18, блока формирователей 32, блока управления 8 и пульта управления 10 соединены с управляющими шинами 20, числовые выводы блока сопряжения с внешними устройствами 9, пульта управления 10, регистра 1 числа,оперативного накопителя 12, эталонного накопителя 13, первого 2, второго 3 и третьего 4 буферных регистров, блока управления 8 и блока сравне.35, входы блока индикации 11 соединены с регистрирующими выводами пульта управления 10, выходы блока сопряжения с внешними устройствами 9являются выходами ввода-вывода уст-.ройства 23, выводы .блока хранениямикропрограмм 33 дополнительнымиадресными 36, числовыми 37 и управляющими 38 шинами соединены с блоком управления 8, выходы первого 2, 10второго 3 и третьего буферных ре-гистров соединены соответственнос первым 29, вторым 30 и третьим 31промежуточными регистрами, выходыкоторых соединены соответственно с 15первым 26, вторым 27 и третьим 28цифроаналоговыми преобразователями,выходы которых соединены .соответственно с первым 5, вторым б и третьим 7 усилителями мощности, выходыпервого 5 и второго б усилителеймощности являются соответственнопервым 24 и вторым 25 программирующими выходами устройства, выходытретьего усилителя мощности 7 соедииены со входами первой группы блокаформирователей 32, входы второй группы которого. соединены с выходамирегистра 1 числа, второй группбйвходов блока компараторов 15 и второй группой входов блока сравнения16, первая группа входов которогосоединена со входами блока выработки ошибки 18 и выходами блока компараторов 15, первая группавходовкоторого соединена с выходами блокаформирователей 32 и является числовыми выходами устройства .22, управляющие выводы блоха компараторов15 соединены с выходами блока задания опорных напряжений 14, адрес Оные 21, числовые 22, первйй 24 ивторой 25 программирующие выходыустройства подсоединяются к соответствующим контактам разъема дляустановки программируемой микросхемы 17,Устройство работает следующим образом.1Ввод исходных данных для про О граммирования.При автоматическом вводе с внешних устройств на пульте управления 10 устанавливается режим работы с внешними устройствами, задается устройство, с которого осуществляется ввод, а также объем вводимой информации и область оперативного накопителя 12, в которой она размещается, затем блок управления 8 через блок сопряжения 9 устанавли вает свяэь с выбранным внешним устройством и осуществляет ввод информации и запись ее в заданную .область оперативного накопителя 12.Информационная емкость накопителя 11 65 в несколько раз больше информационной емкости одной программируемой микросхемы, что позволяет ввести в накопитель 12 массив чисел, соответствующий нескольким микросхемам. В процессе ввода для каждого массива чисел подсчитывается контрольная сумма, которая сравнивается с вводимой контрольной суммой с целью контроля правильности вводаКроме того, осуществляется контроль по четности каждого вводимого слова инФормации.При ручном вводе на пульте управления 10 устанавливается режим ручного ввода данных и затем поочередно набираются адреса и коды чисел, подлежащие записи. Блок индикации11 производит индикацию набранных адресов и кодов. Программированиенабираемых кодов может осуществлять"ся сразу же после набора очередного кода, либо массив чисел может быть предварительно сформирован в-оперативном накопителе 12 и затем осу ществлено программирование.При вводе данных с эталонного накопителяэтот режим необходим для осуществления копирования данных ) на пульте управления 10 устанавливается режим копирования эталонного накопителя 13, набираются начальный и конечный адреса копирования,в эталонный накопитель 13 устанавли"вается нужная микросхема и управление передается в блок управления, который в этом режиме поочередносчитывает информацию, подлежащуюзаписи и осуществляет программирование.2, Вывод информации на внешние устройства.Этот режим необходим для сохранения содержимого оперативного накопителя 12 в случае отключения напряже"ния питания вывод на перфоленту ), а также для получения документа на содержимое запрограммированноймикросхемы вывод на пишущую машинку) На пульте управления 10 устанавливается режим работы с внешними устройствами, задается устройство на которое осуществляется вывод, а также начальный.и конечный адреса выводимого массива информации в оперативном накопителе 12. Затем блок управления 8 через блок сопряжения 9 устанавливает связь с выбранным внешним устройством и осуществляет вывод необходимой информации.3КонтроЛь содержимого программируемой микросхемы.Этот режим необходим для следующего:а) определения того,: запрограммирована микросхема памяти или нет;б) определения свободных адресов, если микросхема памяти запрограммирована частично, 1005183.35 В соответствии с кодом, занесенным в регистр 1 числа, подготавливаются к включению соответствующие формирователи блока формироватедей 32.По управляющим сигналам, поступаю О щим с блока управления 8, происходитперезапись кодов из буферных регистров 2, 3, 4 в первый 29, второй 30и третий 31 промежуточные регистры, свыходов которых они поступают соот ветственно на входы первого 26,второго 27 и третьего 28 цифроанало- е говых преобразователей. Выходныенапряжения первого 26 и второго 27цифроаналоговых преобразователейчерез первый 5 и второй 6 усилителимощности поступают. на программирующие выходы 24 и .25 устройства, соединенные с соответствующими входамипрограммирования микросхем.Выходноенапряжение с третьего 28цифроаналогового преобразователя через третий усилитель мощности 7 иподготовленные к включению формирователи блока формирователей 32поступает на первые программирующие 60 выходы устройства, соединенные ссоответствующими числовыми входамимикросхемы. После передачи кодов избуферных регистров 2, 3, 4 в промежуточные регистры 29, 30, 31 в бу ферные регистры 2, 3, 4 заносятся нов) определения. дефектных ячеек, если микросхема памяти частично годная.С этой целью из блока управления 8в регистр 1 числа заносится код числа, соответствующий исходному (не - запрограммированному) состоянию данного типа микросхемы все единицы или нули), Через буферные регистры 2, 3, 4, промежуточные регистры 29, 30, 31, цифроаналоговые преобразователи 26, 27, 28 на выходах усилителей мощности 5, 6, 7 блок управления 8 устанавливает напряжение, соответствующие граничным условиям считывания соответствующего логического состояния программируемой микросхемы предельно допустимые значения напряжений питания, входных управляющих напряжений и т.п.). Из блока управления 8 по адресным шинам 34 в регистр адреса 19поступают последовательно коды адресов. Считываемые коды с программируемой микросхемы памяти поступаютв блок компараторов 15, где производится их сравнение с опорными напряжениями, поступающими из блоказадания опорных напряжений 14. Вблоке компараторов 15 осуществляется,параметрический контроль логическийноль не должен превышать своего значения для данного типа микросхем,например 0,4 В для 155 РЕЗ логическаяединица должна быть больше минимально допустимого значения, например,2,4 В ). В случае несравнения какоголибо разряда блок выработки ошибки18 вырабатывает сигнал ошибки, ко" .торый по шине 20 поступает в блокуправления 8. В блоке сравнения 16происходит .определение неисправного разряда и по команде из блока управления 8 код, соответствующий считанному коду из программируемой микросхемы памяти, поступает в блок управления 8, а также вместе с адресом - в блок индикации 11. В случа необходимости программирования по данному адресу считанный код сравнивается с тем, который в зависимОсти от режима ввода исходных данных поступает из оперативного накопителя 12, эталонного накопителя 13 или с пульта управления 10. Если дефектные разряды не совпадают с разрядами, подлежащими программированию, то могут быть приняты следующие решения:а ) в случае ручного ввода информации и пословного программирования необходимо заменить программируемую микросхему памяти;б) в случае ввода с эталонного накопителя 13 необходимо заменить либопрограммируемую микросхему, либо микросхему-эталон,в) в случае предварительного ввода информации в оперативный накопитель 12, когда вводятся несколько массивов информации, соответствующих нескольким микросхемам, осуществляется сравнение с каждым измассивов; когда находится соответствие, то контроль заканчиваетсяесли и в этом случае соответствие ненайдено, то необходимо либо заменитьпрограммируемую микросхему памяти,либо осуществить дополнительный вводинформации.4, Программирование микросхем.По командам из блока управления15 8 в регистр адреса 19 заносится код,соответствующий адресу программируемой ячейки памяти. В первый 2, второй 3 и третий 4 буферные регистрызаносятся коды, соответствующие зна 20 чениям напряжений, которые необходимо подавать на соответствующие входымикросхемы. В регистр 1 числа в зависимости от типа программируемоймикросхемы заносятся:25 а ) полный код числа при программировании микросхем, допускающихзапись одновременно по всем разрядам числа,б) частичный код числа, имеющийединицу в программируемом разряде;и нули в остальных разрядах, припрограммировании микросхем, допус кающих запись отдельно по каждомуразряду числа,Формула изобретения 55 60 65 вые значения кодов, соответствующиетребуемым значениям напряжения, Изменяя двоичные коды в регистрах 2,3, 4, 29, 30, 31,.можно создаватьлюбую определенную техническими условиями Форму программирующих им-5пульсов длительность, скважность,форму и длительность Фронтов.Адреса и разряды, не подлежащиепрограммированию, определяются блоком управления 8 и пропускаются при 10программировании. Необходимое коли-чество программирующих импульсови .режимы программирования устанавливаются блоком управления . 8 путемвыбора соответствующей микропраграммы из блока 33, В,случае изменения режима программирования микросхемы, появления новых микросхем сновым режимом программирования засчет изменения микрокоманд, хранящихся в блоке хранения микропрограмм33, легко перейти на другой режим.программирования. Цифроаналоговые преобразователи 26, 27, 28 позволяютобеспечить практически любую требуемую форму и амплитуду импульсовпрограммирования5. Контроль программирования,При параметрическом контроле послепрограммирования: каждого слова осуществляется контроль программирования, Для этой цели на первом, втором и третьем выходах устройстваустанавливаются необходимые присчитывании напряженияКоды считанных чисел поступают на соответствующие входы первой группы блокакомпараторов 15, на управляющиевходы которого с блока задания опорных напряжений 14 поступают опорныенапряжения, соответствующие уровню 40логического нуля и .уровню логической единицы. Кодом регистра 1 числа, поступающим на вторую группувходов блока компараторов 15, устанавливается режим проверки, При 45этом коды считанных чисел, в соответствующих разрядах регистра 1 числа которых находится единица, проверяются на единичное состояние,а в разрядах которых находится нульна нулевое. Выходные сигналы с блока компараторов 15 поступают на входы первой группы блока сравнения 16и на входы блока выработки ошибки.18, На входы второй группы блокасравнения 1 б поступает код с ре-.гистра . 1 числа. На выходе блока.сравнения 16 появляется код, в котором разряды, имеющие "плохие нули",т.е. уровень считанных сигналов которых больше нулевого опорного напряжения, имеют единичное значение,а разряды, имеющие фплохие единицыф,т,е. уровень считанных сигналов которых меньше единичного опорногонапряжения, имеют нулевое значение. Сигналы с блока сравнения 16 иблока выработки ошибки 18, по шинам 20 поступают в блокуправления8. Если ошибки нет, то начинаетсяпрограммирование следующего слова,если есть ошибка, то в зависимости .от алгоритма программирования, возможен повторный, дополнительный режим программирования или необходимозаменить ьщкросхему как дефектную.При функциональном контроле пос/ле программирования всего массивачисел производится контроль функционирования на высокой частоте считывания. С блока управления 8 в регистр адреса 19 поступают коды адресов. На выходах устройства 24, 25,22.устанавливаются напряжения, необходимые при считывании. Коды считан-.ных чисел через блок компараторов 15,блок сравнения 16 по числовым ши-нам 35 поступают в блок управления 8,В блоке управления 8 может быть произведено поразрядное сравнение ссоответствующим кодом, считанным изэталонного накопителя 13 или оперативного накопителя 12, или можетбыть подсчитана контрольная сумма,которая сравнивается с эталонной,Технико-экономическое преимуществопредлагаемого устройства для программирования микросхем памяти заключает.ся в следу:ощем. Это устройство относится к классу универсальных автоматических программаторов. Введениецифроаналоговых преобразователей,промежуточных регистров и блока хранения микропрограммы позволяет использовать это устройство дляпрограммирования микросхем различных ти"пов, а также легко вводить коррекцию в программу прожига или обеспечивать программирование вновь появляющихся микросхем без переделки усилителей мощности и блоков питания.Это. повышает достоверность программирования микросхем за счет подбораоптимального значения параметров программирующих импульсов, не внося изменений в блоки устройства,Устройство для программирования микросхем памяти, содержащее регистр числа, первый, второй и третий буферные регистры; первый, второй и третий усилители мощности, блок управления, блок сопряжения с внешними устройствами, пульт управления, блок индикации, оперативный накопитель, эталонный накопитель, блок задания опорных напряжений, блок компараторов, блок сравнения, блок выработки ошибки, регистр адреса, выходы которого являются адресными выходами устройства, адресные .выводы оперативного накопителя, эталонного накопителя, пульта управления, регистра адреса и блока управления соединены с адресными шинами, управляющие выводы регистра адреса, регистра числа, оперативного накопителя эталонного накопителя, первого, второго и третьего буферных регистров, пульта управления, блока управления, блока сопряжения с внешними устройствами, блока сравнения и бло ка выработки ошибки соедииены с шинами управления, числовые выводы регистра числа, блока управления, оперативного накопителя, эталонного накопителя, блока сопряжения с внешни ми устройствами, первого, второго и третьего буферных регистров и блока сравнения соединены с числовыми шинами, выходы первого и второго усилителей мощности являются соответ ственно первым и вторым программирующими выходами устройства, входы бло ка выработки ошибки соединены с входами первой группы блока сравнения и выходами блока компараторов, входы 25 первой группы которого являются числовыми выходами устройства, входы второй группы блока сравнения соединены с выходами регистра числа и со входами второй группы блока ком-З параторов, управляющие выводы которого соединены с выходами блока задания опорных напряжений, входы блока индикации соединены с регистрирующими выходами пульта управления, выходы блока сопряжения с внешними устройствами являются входами вводавывода устройства, о т л и ч а ющ е е с я тем, что, с целью повышения достоверности записи информации,оно содержит первый, второй и третий цифроаналоговые преобразователи,первый, второй и третий промежуточные регистры, блок формирователей,блок хранения микропрограмм, адресные, числовые и управляющие выводыкоторого соединены с соответствующими дополнительными шинами блока управлениявыходы первого, второгои третьего буферных регистров соединены со входами соответствующихпромежуточных регистров, выходы которых соединены со входами соответствующих цифроаналоговых преобразователей, выходы которых соединенысо входами соответствующих усилителей мощности, выходы третьего усилителя мощности соединены со входамипервой группы блока формирователей,входы второй группы которого соединены с выходами регистра числа, выходы блока формирователей соединенысо входами первой группы блока компараторов, управляющие входы первого, второго и третьего промежуточных регистров и блока формирователей соединены с управляющими шинами.Источники информации,принятые во внимание при экспертизе1. РВОМ Ргодгаваегз. Оеь 19 п пеив.1979, чо 1. 35, Р 8, р, 144,2. Устройство записи в программируемое ПЗУ модели Т 310/27 фирмы.ТЛКЭДА, Денси кагаку. 1977, том 27,В 5, с. 33-37 (прототип).1005183 Составитель А.Дерюгиедактор С, Тимохина Техред Л.Пекарь орректор И.Шулл аказ 1911 одписно ИИП 13035 П "Патент", г. Ужгород, ул, Проектна илиа Тираж 59 Государственно елам изобретен сква, Ж, Ра Пкомитета СССРи открытийкая наб., д. 4/5

СмотретьЗаявка

3317158, 13.07.1981

МОСКОВСКИЙ ОРДЕНА ЛЕНИНА И ОРДЕНА ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ ЭНЕРГЕТИЧЕСКИЙ ИНСТИТУТ

ИВАНОВ МИХАИЛ ЭДУАРДОВИЧ, ЦУРПАЛ АЛЕКСАНДР НИКОЛАЕВИЧ, БОРОДИН ГЕННАДИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G11C 17/08

Метки: микросхем, памяти, программирования

Опубликовано: 15.03.1983

Код ссылки

<a href="https://patents.su/7-1005183-ustrojjstvo-dlya-programmirovaniya-mikroskhem-pamyati.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для программирования микросхем памяти</a>

Предыдущий патент: Способ прошивки запоминающей матрицы на ферритовых сердечниках

Следующий патент: Устройство для записи информации в оперативную память

Случайный патент: Устройство управления силовым коммутатором