Устройство для вычисления тригонометрических функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

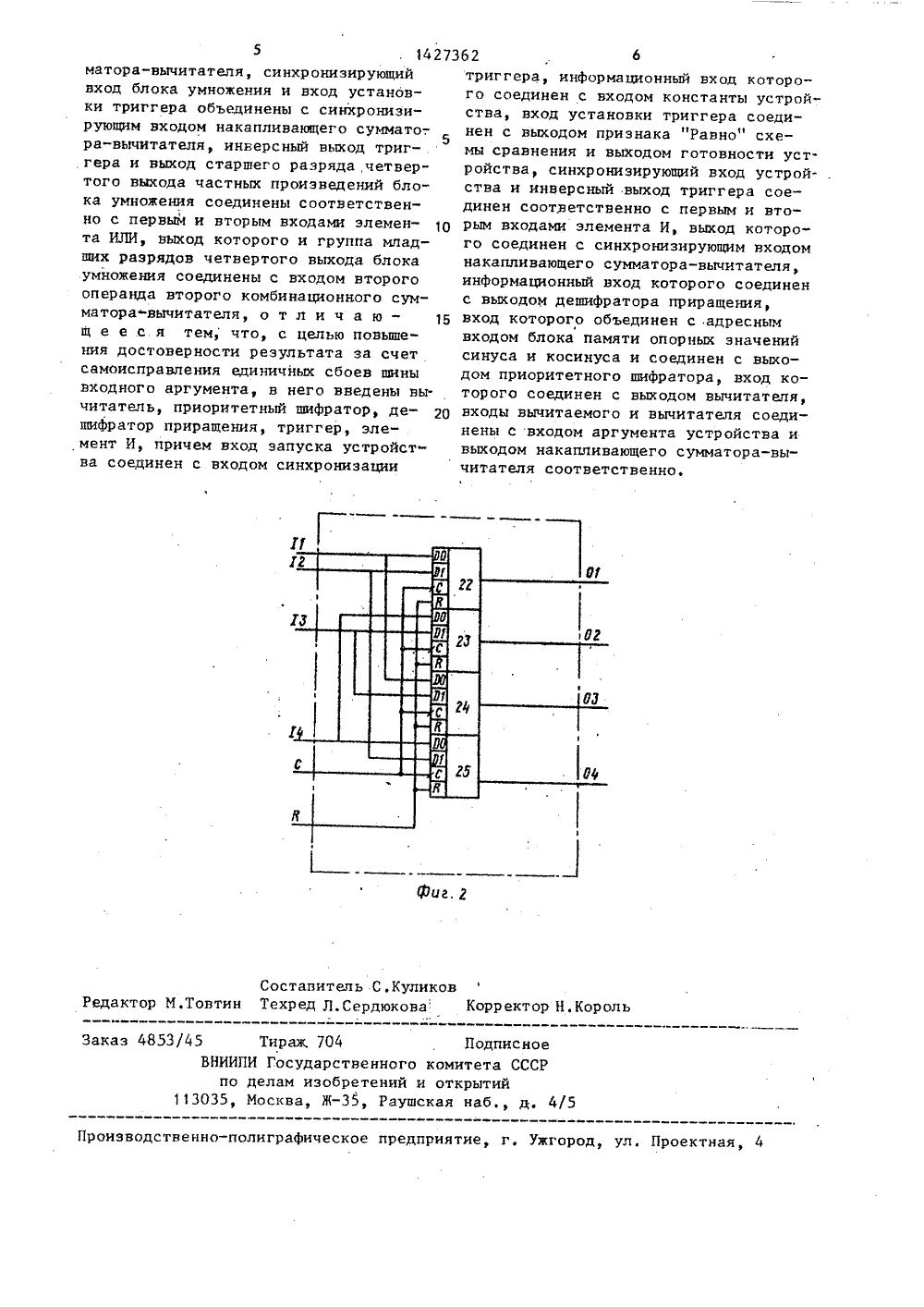

ОЮЗ СОНЕТСН ОЦИАЛИСТИЧРЕСПУБЛИК их 80427 6(51)4 С 0 ОПИСАНИЕ ИЗОБРЕТЕНИЯ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 4 ь ОСУДАРСТВЕННЫЙ НОМИТЕТ ССС ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫ(71) Ленинградский электротехнический институт им, В.И,Ульянова(Ленина) (72) А.А.Валов и Л,М.Виткин ф (53) 681.325(088.8)(56) Авторское свидетельство СССР У 1140116, кл. С 06 Р 7/548, 1984.Авторское свидетельство СССР Р 832552, кл. С 06 Р, 7/548, 1980.(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ТРИГОНОМЕТРИЧЕСКИХ ФУНКЦИЙ(57) Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях, обладающих нысоким быстродействием и высокой достоверностью результатов. Целью изобретения является понышение достоверности результата засчет самоиснравления единичных сбоенаргумента и повышение быстродействияза счет уменьшения числа итераций,Устройство содержит блок 1 памятиопорных значений синуса и косинуса,блок 2 умножения, первый комбинационный сумматор-нычитатель 3, второйкомбинационный сумматор-вычитатель 4,схему сравнения 5, накапливающий сумматор-вычнтатель 6, синхронизирующийвход 7, вход 8 аргумента, вход 9 константы, выход 10 синуса, выход 11 косинуса, вход. 12 начальной установки,вычнтатель 13, приоритетный шифратор14, дешифратор приращения 15, триггер 16, элемент И 17, нход 18 запуска, выход 19 готовности, триггер 20,элемент ИЛИ 21, 2 ил.Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях, обладающих высоким быстродействием и высокой достоверностью резуль 5татов,Цель изобретения - повышение достоверности результата эа счет самоисправления единичных сбоев шины входного аргумента и повышение быстродей-ствия за счет уменьшения числа итерации.На фиг. 1 представлена Функциональная схема устройства; на фиг. 2 - 15Функциональная схема блока умножения.Устройство содержит блок 1 памятиопорных значений синуса и косинуса,блок 2 умножения, первый комбинационный сумматор-вычитатель 3, второй ком бинационный сумматор-вычитатель 4,схему сравнения 5, накапливающий сумматор-вычитатель 6, синхрониэирующийвход 7, вход 8 аргумента, вход 9 константы выход 10 синуса, выход 11 косинуса, вход 12 начальной установки,вычитатель 13, приоритетный шифратор14, дешифратор приращения 15, триггер 16, элемент И 17, вход 18 запуска, выход 19 готовности, триггер 20, 30элемент ИЛИ 21. Блок умножения содержит умножители 22-25 с первого почетвертый,Устройство функционирует следующим образом.35Работа устройства заключается ввычислении функций синуса и косинуса по следующим рекуррентным соотношениям:40-Рсоях;,=соях:,соя 2 -и яхпх;яп 2; (4)х = хп,2Р50где Х - заданное значение аргумента;х, - текущее значение аргумента;- номер шага вычислений;р - номер старшего значимогоразряда двоичного представления2; 1,В качестве начального значения х может быть выбрано либо нулевое значение, либо некоторое известное значение Х. При этом я 1 пх, = О, соях,1, при х = О или яхпх = я 1 п 7,- осоях = сояХ, при х = Х,В исходное состояние устройствопереводится импульсным сигналом установки по входу 12 начальной установки устройства. При этом на выходе накапливающего сумматора-вычитателя 6 аргумента и на выходе первогокомбинационного сумматора-вычитателя3 появляется код нуля (яп 0=0), навыходе второго комбинационного сумматора-вычитателя 4 - код единицы(соя 0=1) .Код единицы образуется на выходесумматора 4 следующим образом. Сигнал установки со входа 12 начальнойустановки устройства, поступая навход обнуления блока 2 умножения,переводит в нулевое состояние умножители 22-25 и триггер 20. В результате, на первом - третьем выходахблока 2 умножения появляется код нуля. На четвертом выходе - код единицы, (1.0000), так как значениестаршего разряда равно единице,поступающей через элемент ИЛИ 21 с инверсного выхода триггера 20,Таким образом, в исходном состоянии на выходе накапливающего сумматора-вычитателя 6 и на выходе 10синуса устройства присутствует коднуля, на выходе 11 косинуса устройства - код единицы.Поступление данных на вход 8 аргумента устройства сопровождаетсястробирующим сигналом пуска по входу 18 пуска устройства, Сигнал готовности результата на выходе 19 готовности принимает нулевое. значение.Если Х ) х (исходно х, = 0),то нулевой сигнал с выхода признака"Меньше" схемы 5 сравнения настроитнакапливающий сумматор-вычитатель6 и первый комбинационный сумматорвычитатель 3 на операцию суммирования, единичный сигнал с выхода признака "Больше" схемы 5 сравнения настроит второй комбинационный сумматор-вычитатель 4 на операцию вычита-ния. На выходе приоритетного шифратора 14 появится код старшего значимого разряда величины,Задним (положительным) фронтомсигнала пуска производится переводтриггера 16 в нулевое состояние, итем самым разблокируется элемент Из 1427317 для пропускания импульсов с синхронизирующего входа 7 устройства,По фронту каждого тактового импульса осуществляется увеличение5(уменьшение) содержимог о накапливающего сумматора-вычитателя 6 на велиРчину 2 , где р - номер старшего значимого разряда величины. Одновременно осуществляется вычисление значения здпх;, и созхпо соотношениям (3), (4) с помощью блока 2 умножения и комбинационных сумматоров3,4.После очередного тактового импульса в накапливающем сумматоре-вычйтателе 6 появится код, совпадающий созначением аргумента, В этом случаепроявляющийся единичный сигнал навыходе признака "Равно" схемы 5 сравнения установит триггер 16 в единичное состояние, блокируя тем самым элемент И 17 для прохождения тактовыхимпульсов с синхронизирующего входа7 устройства, Данный единичный сигнал поступает также на выход 19 готовности устройства, свидетельствуяоб окончании вычислительного процесса, Вычисленные значения зпХ и созХнаходятся на выходах 10, 11 устройства соответственно,50 55 В ряде случаев необходимо вычислять значение функций синуса и косинуса для некоторого набора аргументов, являющихся близкими одно другому числами, т.е. необходимо организовать работу устройства в динамическом режиме для малых приращений аргументаВ этом случае сигнал установки на вход 12 устройства не выдается, В накапливающем сумматоре-вычитателе 6 содержится предыдущее значение аргумента, на выходах 10, 11 устройства присутствуют вычисленные значения функций синуса и косинуса для этого аргумента, После поступления на вход 8 аргумента устрой ства нового значения аргумента Х и запуска устройства оно будет функционировать также, как было рассмотрено выше, за исключением того, что на выходе приоритетного шифратора 14 в каждом такте работы устройства будет появляться код старшего значи/ мого разряда числа 2 =Х -Х, а не числа Х . При значениях Х и Х, близких одно другому такой режим работы устройства позволяет существенно 25 3035 ао уменьшить время вычисления функций синуса и косинуса,При наличии единичных сбоев на входе аргумента значение аргумента Х может измениться. На следующем шаге изменится и значение зпх (созх ) на величину 2 , "отслеживая" изменение Х.Так как к началу очередного такта значение восстановится, то на этом шаге восстановится и прежнее значение х . Таким образом единичный сбой, приведший к искажению входного аргумента" не повлечет в общем случае искажения результата вычислений,формула изобретенияУстройство для вычисления тригонометрических функций, содержащее блок памяти опорных значений синуса и косинуса, два комбинационных сумматоравычитателя, схему сравнения, накапливающий сумматор-вычитатель, блок умножения, триггер и элемент ИЛИ, причем входы первого и второго операндов схемы сравнения соединены с входом аргумента устройства и выходом накапливающего сумматора-вычитателя соответственно, выход признака "Меньше" схемы сравнения соединен с входами выбора режима накапливающего сумматора-вычитателя и первого комбинационного сумматора-вычитателя, вход вь 5 ора режима второго комбинационного сумматора-вычитателя соединен с выходом признака "Больше" схемы сравнения, вход начальной установки устройства соединен с входом сброса накапливающего сумматора-вычитателя,входом обнуления блока умножения ис входом сброса триггера, выход первого комбинационного сумматора-вычитателя, первый и второй выходы блока памяти опорных значений синуса и косинуса и выход второго комбинационного сумматора-вычитателя соединены с входами операндов блока умножения с первого по четвертый соответ твенно, первый и второй выходы частных произведений блока умножения соединены с входами соответственно первого и второго операндов первого комбинационного сумматора-вычитателя, третий выход частных произведений блока умножения соединен с входом первого операнда второго комбинационного сум4 Подписноеитета СССРкрытийнаб д 4/5 к осударственного ко ам изобретений и о ква, Ж, Раушска роизводственно-полиграфическое предприятие, г, Ужгород, у ектна 5 14273 матора-вычитателя, синхронизирующий вход блока умножения и вход установки триггера объединены с синхронизирующим входом накапливающего суммато-.5 ра-вычитателя, инверсный выход триггера и выход старшего разряда, четвертого выхода частных произведений блока умножения соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого и группа младших разрядов четвертого выхода блока умножения соединены с входом второго операнда второго комбинационного сумматоравычитателя, о т л и ч а ю - 1 Б щ е е с я тем, что, с целью повыше ния достоверности результата за счет самоисправления единичных сбоев шины входного аргумента, в него введены вычитатель, приоритетный шифратор де шифратор приращения, триггер, элемент И, причем вход запуска устройства соединен с входом синхронизации 62 6триггера, информационный вход которого соединен с входом константы устройства, вход установки триггера соединен с выходом признака "Равно" схемы сравнения и выходом готовности устройства, синхрониэирующий вход устройства и инверсный выход триггера соединен соответственно с первым и вторым входами элемента И, выход которого соединен с синхронизирующим входомнакапливающего сумматора-вычитателя,информационный вход которого соединенс выходом дешифратора приращения,вход которого объединен с адреснымвходом блока памяти опорных значенийсинуса и косинуса и соединен с выходом приоритетного шифратора, вход которого соединен с выходом вычитателя,входы вычитаемого и вычитателя соединены с входом аргумента устройства ивыходом накапливающего сумматора-вычитателя соответственно,

СмотретьЗаявка

4216542, 27.03.1987

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. УЛЬЯНОВА

ВАЛОВ АЛЕКСАНДР АЛЕКСАНДРОВИЧ, ВИТКИН ЛЕВ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 7/548

Метки: вычисления, тригонометрических, функций

Опубликовано: 30.09.1988

Код ссылки

<a href="https://patents.su/4-1427362-ustrojjstvo-dlya-vychisleniya-trigonometricheskikh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления тригонометрических функций</a>