Логарифматор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

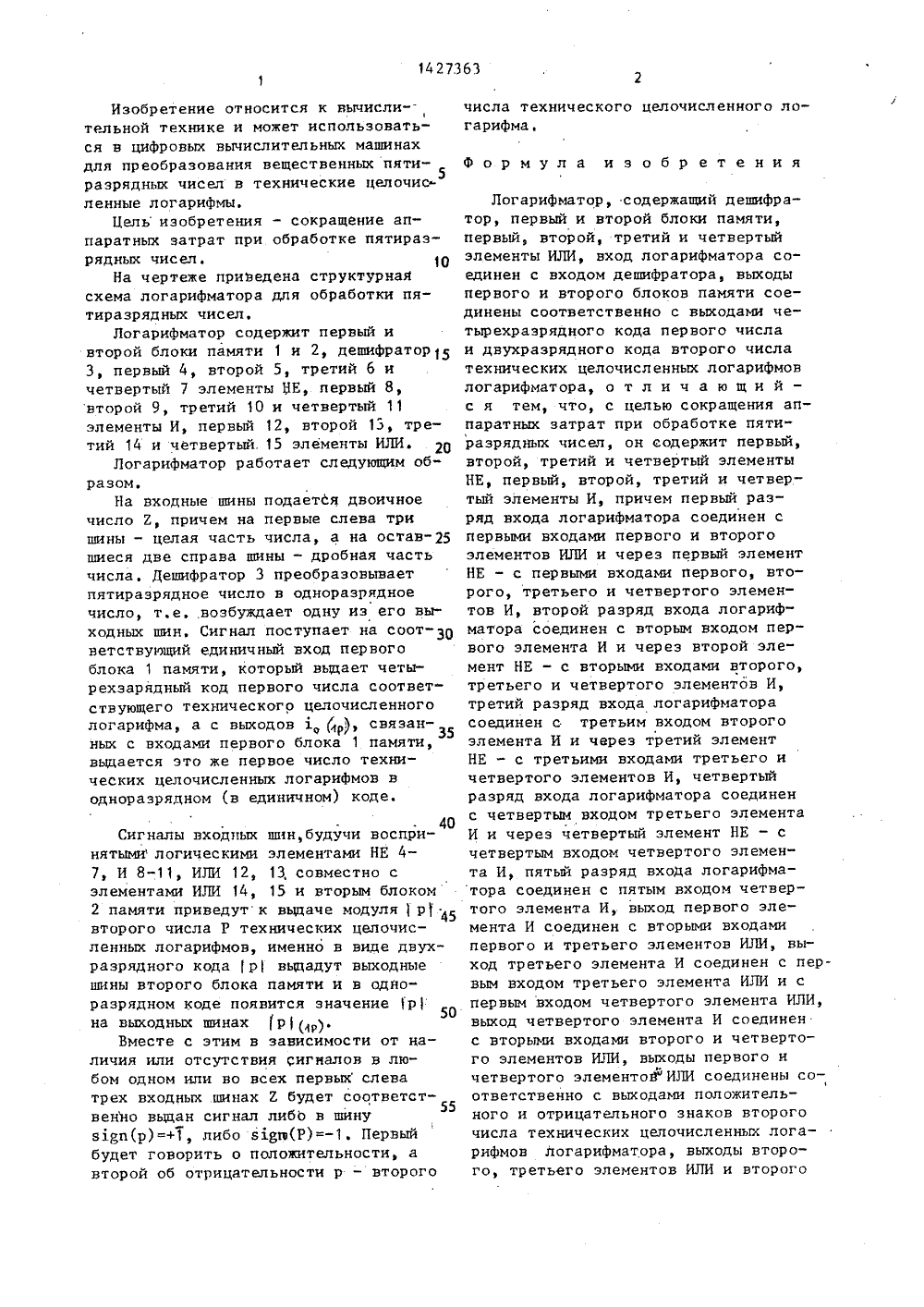

ОЮЗ СОВЕТСКИХ ЦИАЛИСТИЧЕСН СПУБЛИН 36,14 19 51)4 С 06 р 7/556 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ПИСАНИЕ ИЗОБРЕТЕНИЯ ТОРСНОМУ СВИДЕТЕЛЬСТВУ 9054 5/24-24(72) Н.А,Филиппов и (53) 681.325(088,8) тельной технике и может использоватья в цифровых вычислительных машинах ля преобразования вещественных пяти разрядных чисел в технические целочисленные логарифмы, Цель изобретения - сокращение аппаратных затрат скии и.Филиппова то НЕ еме ии и четвертыи элемый, второй, третийенты ИЛИ 12-15. 1 и я к вычисли(56) Авторское У 819732, кл.Авторское с В 1298741, кл, (54) ЛОГАРИФМА (57) Изобретени свидетельство СССР01 К 21/06, 1979.идетельство СССРС 06 Р 7/556, 1985ОРе относитс при обработЛогарифматорой блоки ипервый, в е пятира содержи мяти 1 и ой, трет 4-7, пер рядных чисел,первый и вто 2, дешифратор 3,й и четвертыйьп 1, второй тренты И 8-11, перчетвертый элеИзобретение относится к вычисли тельной технике и может использоваться в цифровых вычислительных машинахдля преобразования вещественных пяти 5разрядных чисел в технические целочисленные логарифмы,Цель изобретения - сокращение аппаратных затрат при обработке пятиразрядных чисел. 1 ОНа чертеже приведена структурнаясхема логарифматора для обработки пятиразрядных чисел.Логарифматор содержит первый ивторой блоки памяти 1 и 2, дешифратор 153, первый 4, второй 5, третий 6 ичетвертый 7 элементы НЕ, первый 8,второй 9, третий 10 и четвертый 11элементы И, первый 12, второй 13, третий 14 и четвертый. 15 элементы ИЛИ.Логарифматор работает следующим образом,На входные шины подается двоичноечисло 2, причем на первые слева тришины - целая часть числа, а на остав шиеся две справа шины - дробная частьчисла. Дешифратор 3 преобразовываетпятиразрядное число в одноразрядноечисло, т.е, возбуждает одну из его выходных шин. Сигнал поступает на соот ветствуищий единичный вход первогоблока 1 памяти, который вьдает четырехзарядный код первого числа соответствующего технического целочисленногологарифма, а с выходов), связанных с входами первого блока 1 памяти,вьдается это же первое число технических целочисленных логарифмов водноразрядном (в единичном) коде.40Сигналы входных шин,будучи воспринятымй логическими элементами НЕ 4- 7, И 8-11, ИЛИ 12, 13, совместно с элементами ИЛИ 14, 15 и вторым блоком 2 памяти приведут к вьдаче модуляр 1 45 второго числа Р технических целочисленных логарифмов, именно в виде двух- разрядного кода р вьдадут выходные шины второго блока памяти и в одноразрядном коде появится значение 1 р 1 на выходных шинах р р).50Вместе с этим в зависимости от наличия или отсутствия сигналов в любом одном или во всех первых слева трех входных шинах 2 будет соответственно вьдан сигнал либЬ в шину55 зЦп(р)=+1, либо я 1 ре(Р)=-1. Первый будет говорить о положительности, а второй об отрицательности р - второго числа технического целочисленного логарифма,Формула изобр етенияЛогарифматор, содержащий дешифратор, первый и второй блоки памяти, первый, второй, третий и четвертый элементы ИЛИ, вход логарифматора соединен с входом дешифратора, выходы первого и второго блоков памяти соединены соответственно с выходами четырехразрядного кода первого числа и двухразрядного кода второго числа технических целочисленных логарифмов логарифматора, о т л и ч а ю щ и й - с я тем, что, с целью сокращения аппаратных затрат при обработке пяти" разрядных чисел, он содержит первый, второй, третий и четвертый элементы НЕ, первый, второй, третий и четвертый элементы И, причем первый разряд входа логарифматора соединен с первыми входами первого и второго элементов ИЛИ и через первый элемент НЕ - с первыми входами первого, второго, третьего и четвертого элементов И, второй разряд входа логарифматора соединен с вторым входом первого элемента И и через второй элемент НЕ - с вторыми входами второго, третьего и четвертого элементов И, третий разряд входа логарифматора соединен с третьим входом второго элемента И и через третий элемент НЕ - с третьими входами третьего и четвертого элементов И, четвертый разряд входа логарифматора соединен с четвертым входом третьего элемента И и через четвертый элемент НЕ - с четвертым входом четвертого элемента И, пятый разряд входа логарифма- тора соединен с пятым входом четвертого элемента И, выход первого элемента И соединен с вторыми входами первого и третьего элементов ИЛИ, выход третьего элемента И соединен с первым входом третьего элемента ИЛИ и с первым входом четвертого элемента ИЛИ, выход четвертого элемента И соединен с вторыми входами второго и четвертого элементов ИЛИ, выходы первого и четвертого элементоУИЛИ соединены соответственно с выходами положительного и отрицательного знаков второго числа технических целочисленных логарифмов логарифматора, выходы второго, третьего элементов ИЛИ и второгоЗаказ 4853/45 Тираж 704 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб д. 4/5 Производственно-полиграфическое предприятие, г. ужгород. ул, Проектная, 4 элемента И соединены соответственно спервым, вторым и третьим входами второго блока памяти и первым, вторым итретьим разрядными. выходами одноразрядного кода второго числа технических целочисленных логарифмов логарифматора, первый, второй, четвертый, .восьмой и шестнадцатый выходы дешифратора соединены с первым входом пер Ового блока, памяти, второй вход которого соединен с семнадцатым выходом дешифратора, третий, шестой, двенадцатыйи двадцать четвертый, выходы которогосоединены с девятым входом первогоблока памяти, третий вход которогосоединен с девятым и восемнадцатымвыходами дешифратора, пятый, десятыйи двадцатый выходы которого соединены с пятым входом первого блока памя Оти, четвертый вход которого соединенс девятнадцатым выходом дешифратора,седьмой, четырнадцатый и двадцатьвосьмой выходы которого соединены стринадцатым входом первого блока па мяти, шестой вход которого соединен сдвадцать первым выходом дешифратора,одиннадцатый и двадцать второй выходыкоторого соединены с седьмым входомпервого блока, памяти, восьмой вход которого соединен с двадцать третьимвыходом дешифратора, тринадцатый идвадцать шестой выходы которого соединены с одиннадцатым входом первогоблока памяти, десятый вход которогосоединен с двадцать пятым выходом де-шифратора, пятнадцатый, тридцатый итридцать первый выходы которого соединены С пятнадцатым входом первого блока памяти, двенадцатый вход которогосоединен с двадцать седьмым выходомдешифратора, двадцать девятый выходкоторого соединен с четырнадцатым входом первого блока памяти, с шестнадцатого по тридцатый выходы дешифраторасоединены соответственно с первого попятнадцатый выходами первого числаодноразрядного кода технических целочисленных логарифмов логарифматора.

СмотретьЗаявка

4090545, 16.07.1986

ФРУНЗЕНСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ФИЛИППОВ НИКОЛАЙ АНДРИАНОВИЧ, ФИЛИППОВА ЛЮДМИЛА НИКОЛАЕВНА

МПК / Метки

МПК: G06F 7/556

Метки: логарифматор

Опубликовано: 30.09.1988

Код ссылки

<a href="https://patents.su/3-1427363-logarifmator.html" target="_blank" rel="follow" title="База патентов СССР">Логарифматор</a>

Предыдущий патент: Устройство для вычисления тригонометрических функций

Следующий патент: Оптоэлектронный сумматор

Случайный патент: Устройство для аварийной защиты ротора осевого компрессора газотурбинного двигателя