Процессорный модуль однородной вычислительной структуры

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1345207

Авторы: Золотовский, Карпенко, Коробков, Степанян

Текст

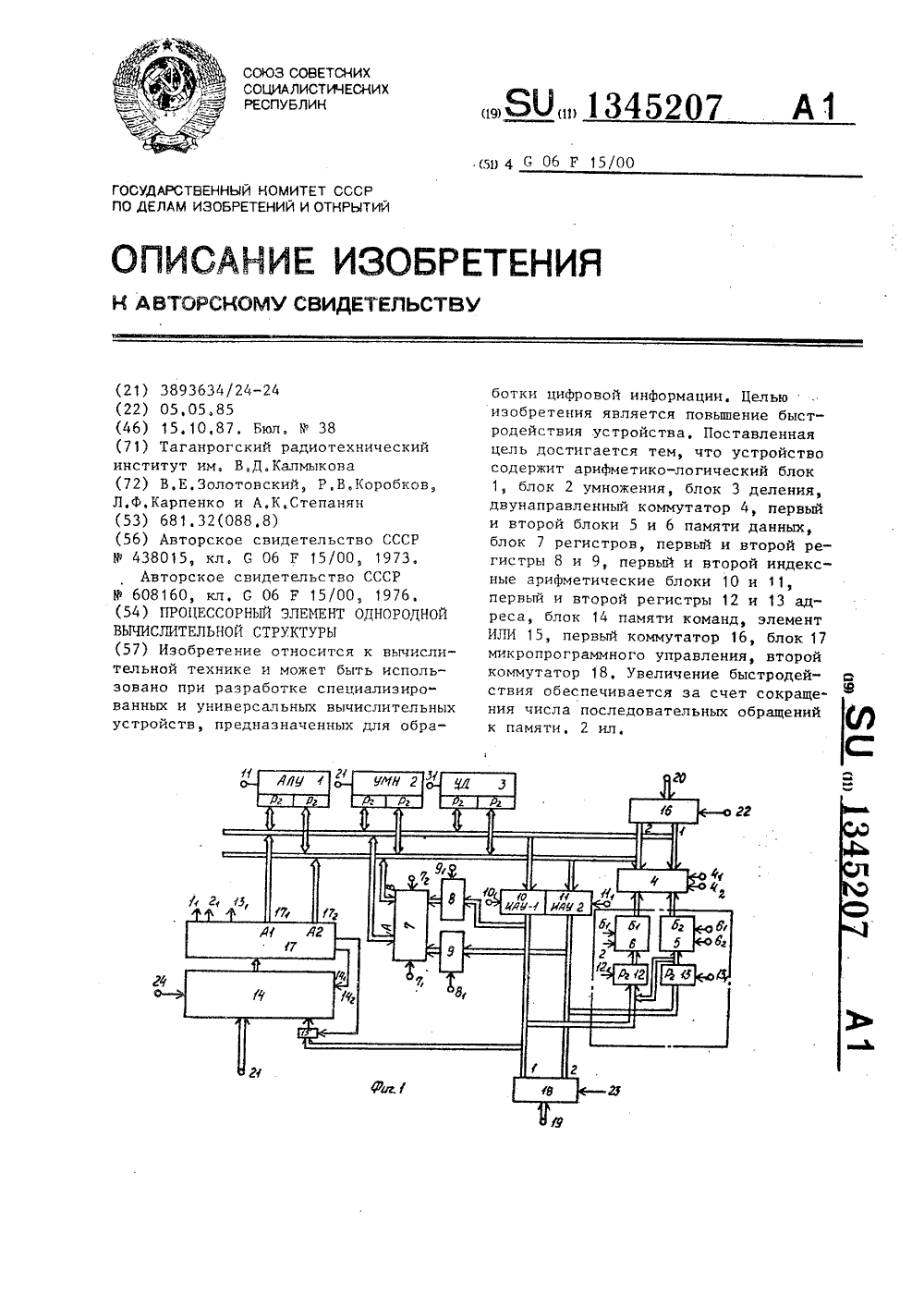

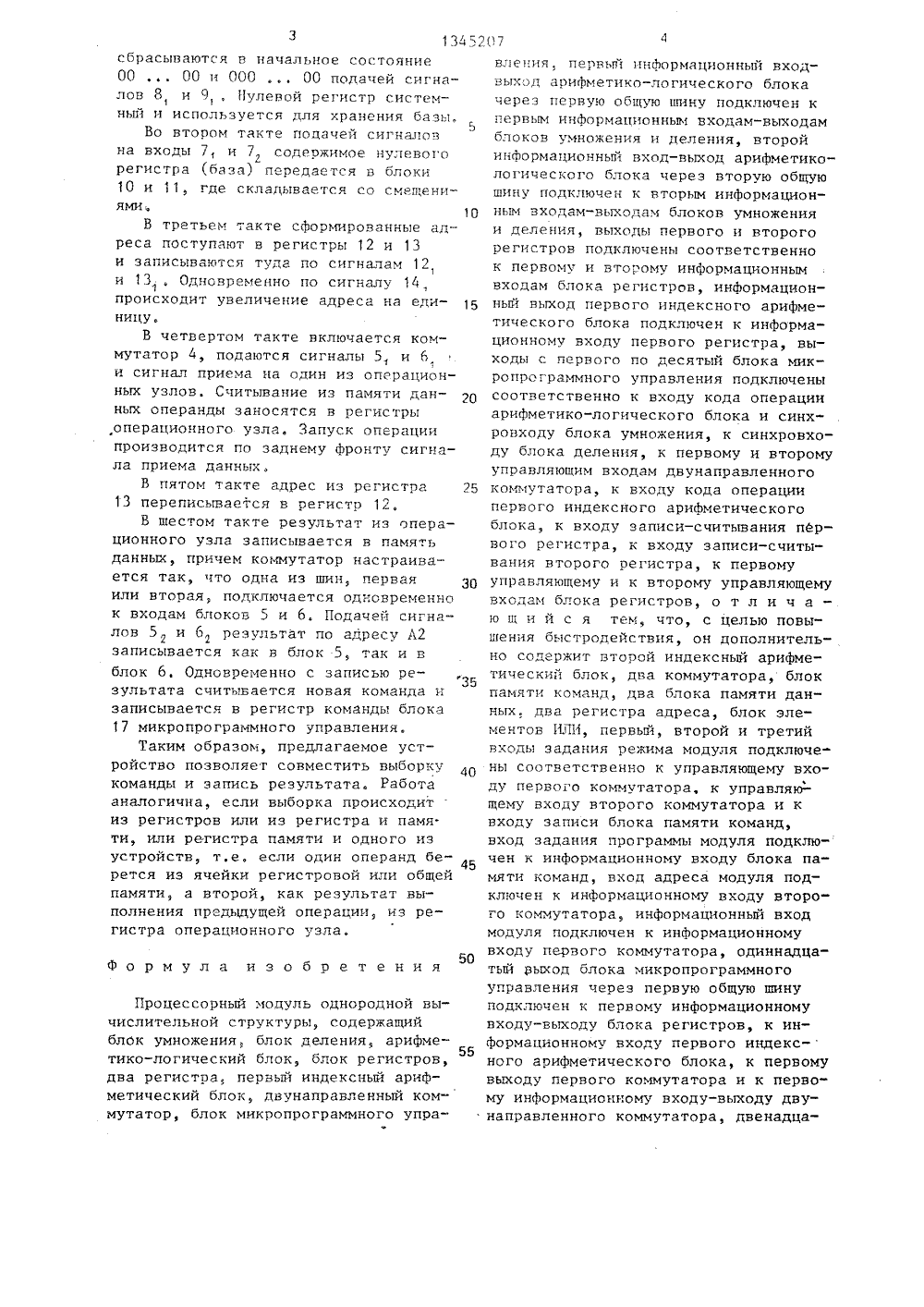

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСКРЕСПУБЛИК А 51)4 С 06 Р 15 ПИСАНИЕ ИЗОБРЕТЕНИЯ С: ОСУДАРСТНЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(71) Таганрогский радиотехническии институт им, В,Д.Калмыкова (72) В,ЕЗолотовский, Р,В,Коробков, Л.Ф,Карпенко и А,К,Степанян (53) 681,32(088,8)(56) Авторское свидетельство СССР У 438015, кл, С 06 Г 15/00, 1973.Авторское свидетельство СССР В 608160, кл, С 06 Р 15/00, 1976, (54) ПРОЦЕССОРНЫЙ ЭЛЕМЕНТ ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ(57) Изобретение относится к вычислительной технике и может быть использовано при разработке специализиро" ванных и универсальных вычислительных устройств, предназначенных для обработки цифровой информации, Цельюизобретения является повьппение быстродействия устройства, Поставленнаяцель достигается тем, что устройствосодержит арифметико-логический блок1, блок 2 умножения, блок 3 деления,двунаправленный коммутатор 4, первыйи второй блоки 5 и 6 памяти данных,блок 7 регистров, первый и второй регистры 8 и 9, первый и второй индексные арифметические блоки 10 и 11,первый и второй регистры 12 и 13 адреса, блок 14 памяти команд, элементИЛИ 15, первый коммутатор 16, блок 17микропрограммного управления, второйкоммутатор 18, Увеличение быстродей"ствия обеспечивается за счет сокращения числа последовательных обращенийк памяти, 2 ил,)Изобретение от;о(.ится к н т;ис 1;- тельной технике и может бь 1 т 1)с)10)1) -зовано при разрабатк: с:тс цн:ализирс)ВаННЫХ И УНИВЕРСЯЛЬ)1 ГХ )3 ЬсС)П.ОПЬ,ГХустройств) паеднЯэна ен ньГ)х д)151 Об;),1 -ботки цифровой штфа )ма ,ии,Цель изобретения ":-;эвьппс ис бьпстродействия устройства,На фиг,1 пведставлена струп(турцЯсхема процессорного элемента; нафиг,2 - структурная хема пат(а управления процессарнэ. о элеме л а,Процессорный элс;ент лпнаэапнлйвычислитечьной структуры содержитарифметика-логический блок 1 блок 2умножения, блок 8 де.ения, даунправленный коммутя.тор -, первьп: и в горойблОки 5 ипамяти данных б 10 к 7регистров, первый и второй -.,: Пистрь:8 и 9, первый и второй индекснь)е1 ариметические блоки 10 и 1)1, тервыйи второй регистры 12 и 18 адреса,блок 1) памяти команд эле:")ент 11 П 13)15, первый камт.утатар 16, алакмикропрограммного угсрс)п)ле 1."5) второйкоммутатор 18, вход 1 адресов устройства, вход 20 даттных;страйства., Вха)с21 программы устройств;., первьпл вход22, Второй Вход 23 трс тий входрежима устройства. Бпа к упа влет ясодержит регистр 2" каяГсь), с г. г;ик26, блок 27 постоянной памя"и р. -гистр 28 микрокоманд, генев; тлр ",тактовых импульсов,Працессорньпл элемент рабс тс(ет .едующим образом.На ПЕРВОМ ЭтаПЕ ПраИСХадит ЗГ)т(1)Ьпрограммы и данных саатвет)ге).нс зпамять команд и память дан ).с (.тяэтого коьптутятар 1 втер(клкч,с)тсясостояние "Прием с н)ины" 11г) 0):31ляс первой шины пастуяет на лак 5 ас второй шины - на блок 6 Г:мяти данных При эгам комму"ат.")р 1 ь ахат)тс )1Б состоянии Включен.сДиузс.5 с)входа 20 одновременна поступет нппервую и вторую ил-ы Г(нных, Синхэонно с этим включаетсн комму;"ар 18.АдРес С входа 19 па(:ту. в ,ает 3 регстры 12 и 13, Тактгс образом,. В бт,ках5 и 6 в опнаимег,ных адресах лказыва.ются записанными 011):.Р)акавь)е )сань(3.После записи Гтаннь(х кс)мутаглр "6Отклн)чает внутренни(3 1)ип 1 лт В)епт ,е)сПРаисхопит запись п 0, Рамл)у В б:)л;14 памяти команд Сигнап )са зхлг;е.коммутатора ) 8 с лхгт 5)ется Гтресппоступают 13 бт)лк 1 ) пс) М 5 т 1) к )т 3.,1-л с -арпслх разрядов - первая шина,1 р)1 гдви;е влево Результат берется(:Ладпт;х ра гядав - вторая тпина 1 в у) зс 11 "- число разряпОВ ) )(а .с,б),(дим) ГП),иьу,ь числО, лм - Попал: ение числа разкстлрае необходима сдвинуть ч;1 нл 1: разсряднаи с(зтк)л) техл;тима сгп.нуть ня 5 разря- О, та г.=5, а если влево,пс;)вам сл 0 РС)Е Е) С Е) Т Л Р:, .:ерелпаг, и опера(Ни нап адресами выпслня;)тся с лгпал ьзованием индексньгх. Ри(ЬЫ)ег)1 еск)лх б:Ок в ., Й и 1 1,Операция выпалня тся следующим оарамКомс)1 да и б:)Ока) ПамяТИ КамНД ПСс:тупает в б:ак у;.разления е регистр 25 ксмалды, Код опери и и признаки аресапли "1;:тупагт на вход счетчика2)с как тася:Н) ь 3 адрес микропрограммы53 ь)ПО 1 НЯ Е; Ь. й ГСЕРа (ИИ СИНХРОНИЗИРУЮПП;Е И)Псу,туСЬ С 1 НЕратаря 2. ПОСТУ:;ют на счетнтй вход счетчика садернимле катарас; п.)с-упает н гтастоянг)е заг:амин)зпп)пее "гстРайствс) 27 как)3;срес ,",о ер; пма Ячейки згтисываетсян регист,) 28 )(тл;(рлт(лма)-д, выходы ко"с;рого фсрми; гт сслтветствуюцие сигПаки адресации Код лтера)си) р).зсбрасываются в начальное состояние 0000 и 00000 подачей сигналов 8, и 9 Нулевой регистр системньп и используется для хранения базы,5Во втором такте подачей сигналов на входы 7, и 7 содержимое нулевого регистра (база) передается в алаки 10 и 11, где складывается со смещениями. 10В третьем такте сформированные адреса поступают в регистры 12 и 13 и записываются туда па сигналам 12, и 13, Одновременно па сигналу 14 происходит увеличение адреса на единиЕуВ четвертом такте включается коммутатор 4, подаются сигналы 5 и б и сигнал приема на один из операционных узлов. Считывание из памяти данных операнды заносятся в регистрыоперационного узла. Запуск операциипроизводится па заднему фронту сигнала приема данньгх,В пятом такте адрес из регистра 2 Б 13 переписывается в регистр 12.В шестом такте результат из апера -ционного узла записывается в память данных, причем коммутатор настраивается так, что одна из шин, первая или вторая, подключается одновременна к входам блоков 5 и б. Подачей сигналов 5, и 6. результат по адресу А 2 записывается как в блок 5, так и в блок 6. Одновременно с записью результата считьвается новая команда и записывается в регистр команды блока 17 микропрограммного управления,Таким образом, предлагаемое устройство позволяет совместить выборку команды и запись результата. Работа аналогична, если выборка происходит из регистров или из регистра и памя.ти, или регистра памяти и одного из устройств, т.е, если один операнд бе рется из ячейки регистровой или общей памяти, а второй, как результат выполнения предыдущей операции, из регистра операционного узла.5 ОФормула изобретенияПроцессорный моцуль однородной вычислительной структуры, содержащий блок умножения, блок деления, арифме 55 тико-логический блок, блок регистров, два регистра, первый индексный арифметический блок, двунаправленный коммутатор, блок микропрограммного управле:.ия, первьпнфармационный входвыхад арифметика-логического блока через первую общую шину подключен к первым информационным входам-вьгходам блоков умножения и деления, второй информационньп вход-выход арифметикологического блока через вторую общую шину подключен к вторым информационным входам-выходам блоков умноженияи деления, выходы первого и второго регистров подключены соответственно к первому и второму информационным входам блока регистров, информационный выход первого индексного арифметического блока подключен к информационному входу первого регистра, выходы с первого по десятый блока микропрограммного управления подключены соответственно к входу кода операции арифметика-логического блока и синхровходу блока умножения, к синхровходу блока деления, к первому и второму управляющим входам двунаправленного коммутатора, к входу кода операции первого индексного арифметического блока, к входу записи-считывания первого регистра, к входу записи-считывания второго регистра, к первому управляющему и к второму управляющему входам блока регистров, о т л и ч а - ю щ и й с я тем, что, с целью повышения быстродействия, он дополнительно содержит второй индексный арифметический блок, два коммутатора, блок памяти команд, два блока памяти данных. два регистра адреса, блок элементов ИЛИ, первый, второй и третий входы задания режима модуля подключены соответственно к управляющему входу первого коммутатора, к управляющему входу второго коммутатора и к входу записи блока памяти команд, вход задания программы модуля подключен к информационному входу блока памяти команд, вход адреса модуля подключен к информационному входу второго коммутатора, информационный вход модуля подключен к информационному входу первого коммутатора, одиннадцатый вьход блока микропрограммного управления через первую общую шину подключен к первому информационному входу-выходу блока регистров, к инФормационному входу первого индекс- ного арифметического блока, к первому выходу первого коммутатора и к первому информационному входу-выходу двунаправленного коммутатора, двенадца:11 Ъ Ь Ь Ф 5 5 В О,. 1 Й УА ф:, д Я. мФи сгь,1 сн Составитель В.,С 1 ирР И,Касарда Техред П,Сердюкова еоп;зе к тор ;е вн ка.з 4922/48 Тираж б 70 ВНИЛГЯ Государственнот о кою, тета по делам изсбретекий и открыти 113035, Москва, Е1 ау:1 ская аб, Нод0 г Р роиз водственно-полиграфическое пр ел пр:.я тие ужг срод ул., :роек т тый выход блока микропрограмм.:ого управления через вторую общую пину подключен к второму информационному входу-вьгходу блока регистров, к информационному входу второго индексного арифметического блока, к второму выходу первого коммутатора и к второму информационному входу-вьгоцу двунаправленного коммутатора, первый выход второго коммутатора объединен с информационным выходом первого индексного арифметического блока и выходом второго регистра адреса и подключен к первому входу блока элементов ИЛИ, к информа 1 ионным входам первого регистра адреса и к адресным входам первого блока памяти данных, . второй выход второго коммутатора объединен с информационным выходом вто рого индексного арифметическсго блска и подключен к информационному входу второго регистра и к информационному входу второго регистра адреса, выход пергого регистра подключен к адресному ,ходу з горо о блока ламятР данных, выходы первого и второго блоков памяти данных подключены соответственно к первому и второму информационным входам двунаправленного коммутатораРвьгходы с тринадцатогс по двадцать первый блока микропрсграммного управ-. б ле:-ия подключены соответственно квходу кода операции второго индексного арифметического блока входу записи. входу чтения первого блока памяти данных, входу записи, входу чтения второго блока памяти данных. входу запуск-считыва.шя первого регистра адреса, входу записи, входу чтения второго 1;егистра адреса, второму входу блока, элементов ИЛИ и х входу б чтения блока памяти команд, выходблока элемента ЧПК подключен к адресному входу блока памяти команд, выход которого лодключенк входукода команды блскамикропрограммного управления.

СмотретьЗаявка

3893634, 05.05.1985

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

ЗОЛОТОВСКИЙ ВИКТОР ЕВДОКИМОВИЧ, КОРОБКОВ РОАЛЬД ВАЛЕНТИНОВИЧ, КАРПЕНКО ЛЕОНИД ФЕДОРОВИЧ, СТЕПАНЯН АЛЕКСАНДР КАРОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: вычислительной, модуль, однородной, процессорный, структуры

Опубликовано: 15.10.1987

Код ссылки

<a href="https://patents.su/4-1345207-processornyjj-modul-odnorodnojj-vychislitelnojj-struktury.html" target="_blank" rel="follow" title="База патентов СССР">Процессорный модуль однородной вычислительной структуры</a>

Предыдущий патент: Устройство для сопряжения двух микроэвм с общим внешним устройством

Следующий патент: Устройство для исследования сетей петри

Случайный патент: Механическая рука робота