Устройство для суммирования последовательно поступающих чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1322262

Автор: Макаров

Текст

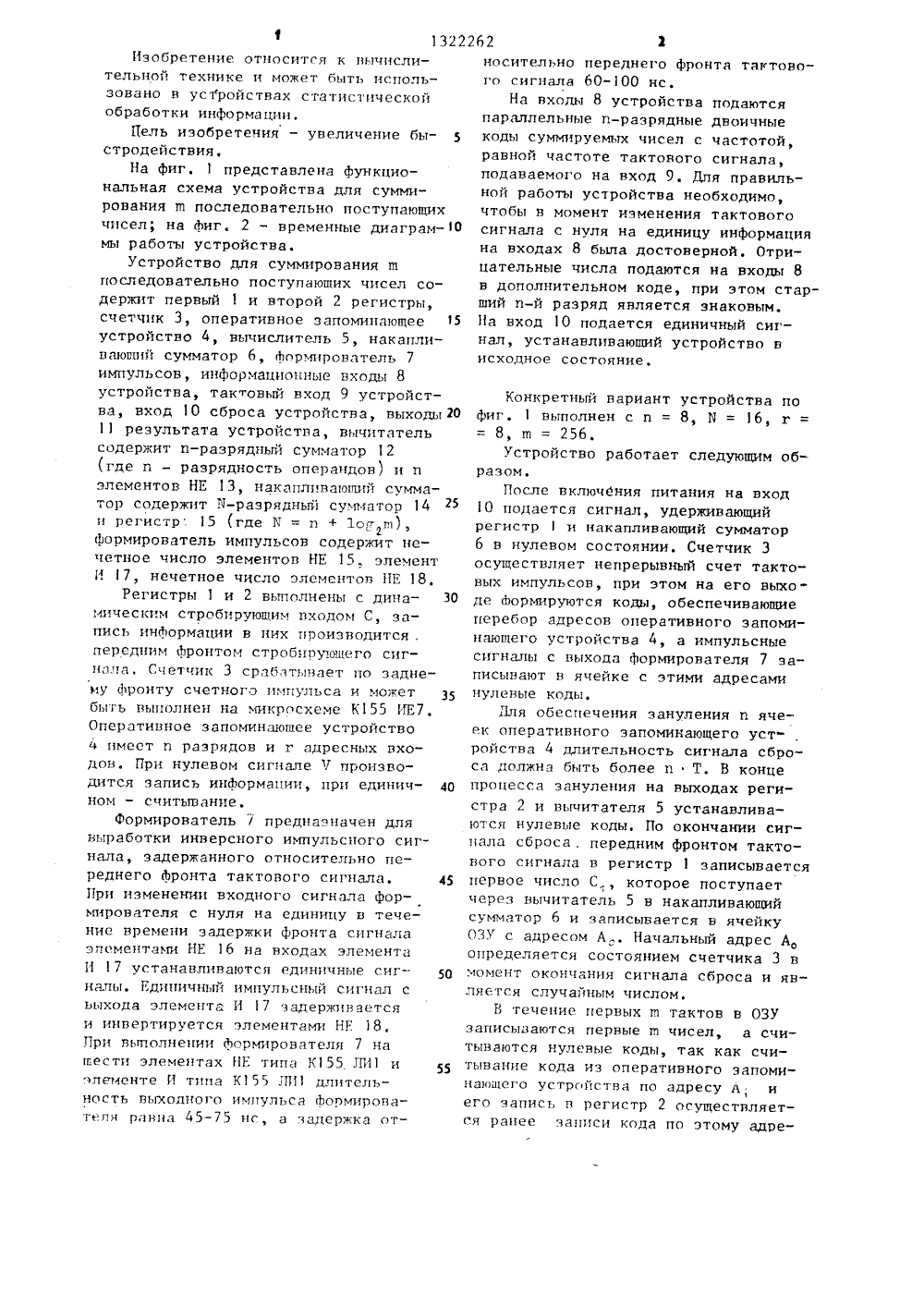

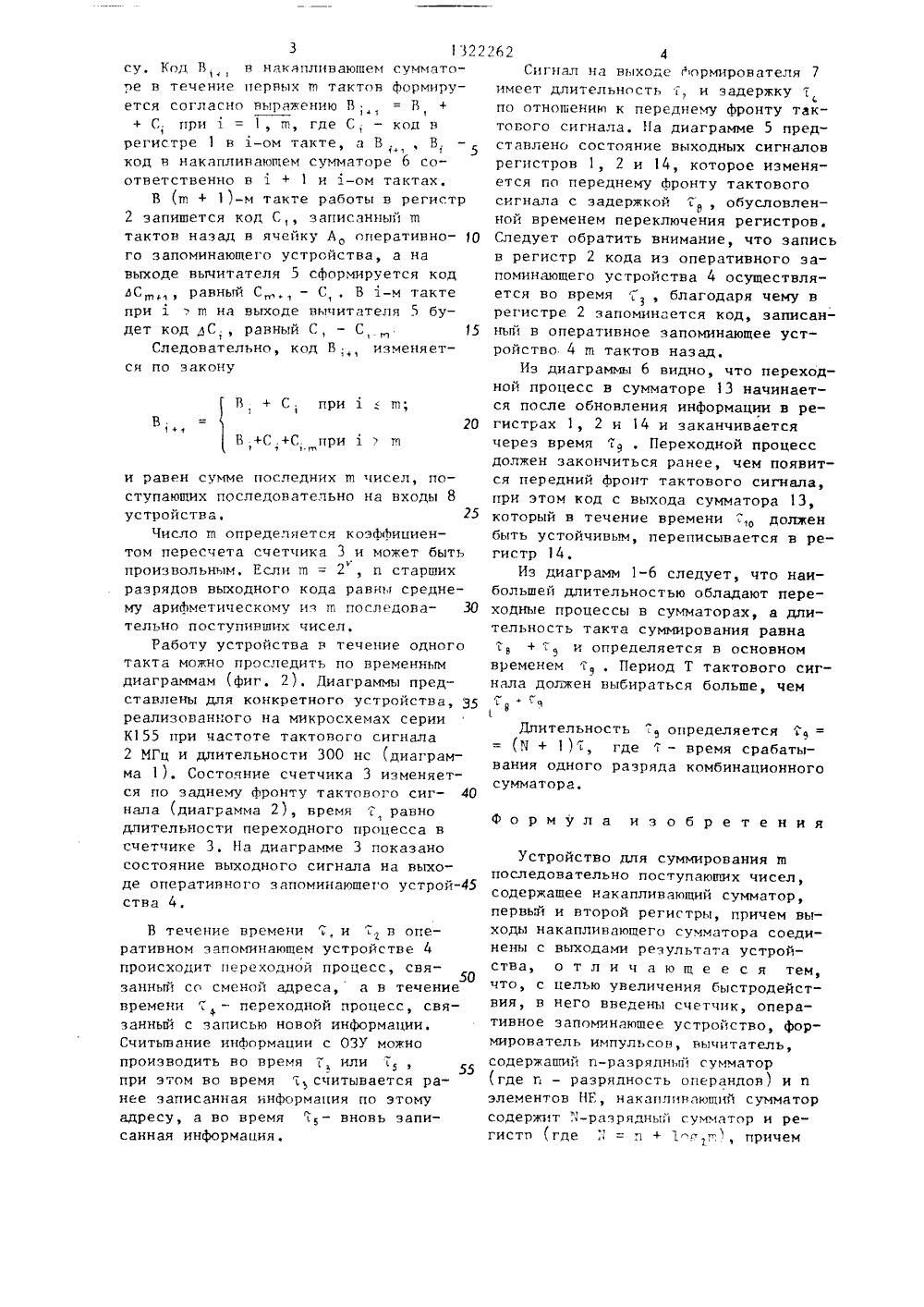

13,вн САНИЕ ИЗОБРЕТЕНИЯ йлио .- д У тель 5, накапливаюрмирователь 7 имонные нход10 сброса ы 8, таквыходыГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ ОРСКОМУ СВИДЕТЕЛ(71) Горьковский исследовательскийфизико-технический институт при Гоконском государстненном университеим, Н, И. Побачевского(56) Авторское снидетельство СССРУ 581470, кл, 0 06 Р 7/50, 975,Авторское снидетельство СССРф 1075260, кл, 0 067150, 1982(54) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ юПОСЛЕДОВАТЕЛЬНО ПОСТУПА 10 ЩИХ ЧИСЕЛ(57) Изобретение относится к нычислительной технике и может быть использовано в устройствам статистической обработки информации, Цель иэобретения - увеличение быстродействия. Устройство для суммирования ш последовательно поступающих чисел содержитпервый и второй регистры 1 и 2, счечик Э, оперативное запоминающее устройство 4, вычитатщий сумматор 6, Фопульсов, информацитовый вход 9, вход11 результата. 2 ил,1322Изобретение относится к вычислительной технике и может быть использовано в устройствах статистической обработки информации.Пель изобретения - увеличение бы стродействия.На фиг, 1 представлена функциональная схема устройства для суммирования щ последовательно поступающих чисел; на Фиг. 2 - временные дидграммы работы устройства.Устройство для суммирования щ последовательно поступающих чисел содержит первый 1 и второй 2 регистры, счетчик 3, оперативное запоминающее 15 устройство 4, вычислитель 5, накапливдющггй сумматор 6, Формирователь 7 импульсов, информационные входы 8 устройства, тактовый вход 9 устройства, вход 1 О сброса устройства, выходы 20 11 результата устройства, вычитдтель содержит и-разрядный сумматор 12 (где и - разрядность операндов) и и элементов НЕ 13, накапливающий сумматор содержит И-разрядцьггг сумматор 14 и регистр. 15 (где И = и + 1 оГ ю), Формирователь импульсов содержит нечетное число элементов НЕ 15 элемент И 17 нечетное число элементов НЕ 18,Регистры 1 и 2 выполнены с дица мическим стробирующим входом С, запись информации в них производится, передним Фронтом стробцрующего сигцлгд. Счетчик 3 срдбдтьвдет по заднему фронту счетного импульса и может бьггь выполнен на микросхеме К 155 ИЕ 7, Оперативное запоминающее устройствоимеет и разрядов и г адресных входон, При нулевом сигнале Ч производится запись информации, при едицичном - считывание,Формирователь 7 предназначен длявыработки инверсного импульсного сигнала, задержанного относительно переднего фронта тактового сигнала. 45При изменении входного сигнала формирователя с нуля на единицу в течение времени задержки фронта сигналаэпемецтдми НЕ 16 на входах элементаИ 17 устанавливаются единичные сигндлы. Единичный импульсный сигцдл сьыхода элемента И 17 задерживаетсяи инвертируется элементами НЕ 18,При выполнении Формирователя 7 цащести элементах НЕ типа К 155 ЛИ 1 и 5элементе И типа К 55 Л 11 длительность выходного импульса Формирователя равна 45-75 цс, а задержка от 262 1носительно переднего фронта тактового сигнала 60-100 нс.На входы 8 устройства подаютсяпараллельные и-разрядные двоичныекоды суммируемых чисел с частотой,равной частоте тактового сигнала,подаваемого на вход 9. Для правильной работы устройства необходимо,чтобы в момент изменения тактовогосигнала с нуля на единицу информацияна входах 8 была достоверной. Отрицательные числа подаются на входы 8в дополнительном коде, при этом старший и-й разряд является знаковым.На вход 1 О подается единичный сигнал, устанавливающий устройство нисходное состояние. Конкретный вариант устройства по Фиг. 1 ныполнен с и = 8, И = 16, г - 8, щ = 256.Устройство работает следующим образом.После включения питания на нход 1 О подается сигнал, удерживающий регистр 1 и накапливающий сумматор 6 в нулевом состоянии. Счетчик 3 осуществляет непрерывный счет тактовых импульсов, при этом на его выходе формируются коды, обеспечивающие перебор адресов оперативного запоминающего устройства 4, а импульсные сигналы с выхода Формирователя 7 записывают в ячейке с этими адресами нулевые коды.Для обеспечения зануления и ячеек оперативного запоминающего уст" ройства 4 длительность сигнала сброса должна быть более и Т. В конце процесса зднулеция на выходах регистра 2 и вычитателя 5 устанавливаются нулевые коды. По окончании сигцала сброса, передним фронтом тактового сигнала в регистр 1 записывается первое число С., которое поступает через нычитатель 5 в накапливающий сумматор 6 и записьгвается в ячейку ОЗУ с адресом А., Начальный адрес Ао определяется состоянием счетчика 3 в момент окончания сигнала сброса и является случайным числом.В течение первых гп тактон в ОЗУ записываются первые и чисел, а считываются нулевые коды, так как считывание кода из оперативного запоминающего устройства по адресу А иего запись в регистр 2 осуществляется ранее записи кода по этому адре 1322262 4В + С, прищ;В +С .+С при .щ1 в п В и равен сумме последних щ чисел, поступающих последовательно на входы 8 устройства, 25Число щ определяется коэффициентом пересчета счетчика 3 и может быть произвольным. Если щ = 2 , п старших разрядов выходного кода равны среднему арифметическому из щ последова тельно поступивших чисел,Работу устройства в течение одного такта можно проследить по временным диаграммам (фиг, 2). Диаграммы представлены для конкретного устройства, у реализованного на микросхемах серии К 155 при частоте тактового сигнала 2 МГц и длительности 300 нс (диаграмма 1). Состояние счетчика 3 изменяется по заднему фронту тактового сиг нала (диаграмма 2), времяравно длительности переходного процесса в счетчике 3, На диаграмме 3 показано состояние выходного сигнала на выходе оперативного запоминающего устройства 4В течение времени 7, и 7 в оперативном запоминающем устройстве 4 происходит переходной процесс, связанный со сменой адреса, а в течение времени 7 - переходной процесс, связанный с записью новой информации. Считывание информации с ОЗУ можно производить во времяилипри этом во времясчитывается ранее записанная информация по этому адресу, а во время , - вновь записанная информация. су, Код В в накяплваюше сумматоре в течение первых щ тактов формируется согласно выражению В = В + + С. при . = 1, щ, где С, - код в1регистре 1 в .-ом такте, а В, , В, код в накапливаюпем сумматоре 6 соответственно в . + 1 и -ом тактах.В (щ + 1)-м такте работы в регистр 2 запишется код С записанный щ тактов назад в ячейку А оперативно О го запоминающего устройства, а на выходе вычитателя 5 сформируется код лС равный С - С, . В -м такте при д , щ на выходе вычитателя 5 будет код дС , равный С, - С, 15Следовательно, код В , изменяется по закону Сигнал на выходе ьормирователя 7имеет длительность , и задеРжкупо отношению к переднему фронту тактогого сигнала, На диаграмме 5 представлено состояние выходных сигналоврегистров 1, 2 и 14, которое изменяется по переднему фронту тактовогосигнала с задержкой, обусловленной временем переключения регистров.Следует обратить внимание, что записьв регистр 2 кода из оперативного запоминающего устройства 4 осуществляется во время в, благодаря чему врегистре 2 запоминается код, записанньп в оперативное запоминающее устройство. 4 щ тактов назад.Из диаграммы 6 видно, что переходной процесс в сумматоре 13 начинается после обновления информации в регистрах 1, 2 и 14 и заканчиваетсячерез время 79, Переходной процессдолжен закончиться ранее, чем появится передний фронт тактового сигнала,при этом код с выхода сумматора 13,который в течение времени ". долженбыть устойчивым, переписывается в регистр 14,Из диаграмм 1-6 следует, что наибольшей длительностью обладают переходные процессы в сумматорах, а длительность такта суммирования равна+ т, и определяется в основномвременем 7 . Период Т тактового сигнала должен выбираться больше, чемРвДлительность 7 в определяется(11 + 1)", где т - время срабатывания одного разряда комбинационногосумматора.Формула изобретенияУстройство для суммирования и последовательно поступаюпих чисел, содержащее накапливающий сумматор, первый и второй регистры, причем выходы накапливающего сумматора соединены с выходами результата устройства, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия, в него введены счетчик, оперативное запоминающее устройство, формирователь импульсов, вычитатель, содержаший и-разрядный сумматор (где г - разрядность операндов) и и элементов НЕ, накапливающий сумматор содержит ,1-разрядны сумматор и регистп (где ,1 = и + 1"г щ), причем1322262 регистра, информационные входы которого соединены соответственно с выходами оперативного запоминающегоустройства, вход переноса и-разрядного сумматора соединен с входом логической единицы устройства, выходыи-разрядного сумматора соединены соответственно с входами с первого пои-й первой группы Г 1-разрядного сумматора, входы первой группы с (п+1)го по Г 1-й которого соединены с выходом п-го разряда п-разрядного сумматора, входы второй группы И-разрядного сумматора соединены соответственно с выходами регистра накапливающего сумматора и соединены соответственно с выходами накапливающегосумматора, вход сброса устройствасоединен с входами установки первогорегистра и регистра накапливающегосумматора, информационные входы которого соединены соответственно свыходами Г 1-разрядного сумматора. Составитель Г 1, ЕсенинаГерепи Техред А,Кравчук Кор Редакт С. Шекмар 44Р 1 1 аказ 286 Тираж 672 П ИГП 1 Госудаоственного к по делам изобретений и 5, Москва, Ь, Раушс писноемитета СССР ткрытя наб 5 роцэно тстнсцц пиграфическое пред ццформациоццые входы первого регистра соединены соответственно с Входами разрядов операндов устройства,тактовый вход устройства соединен свходами синхронизации первого и второго регистра и регистра накапливающего сумматора, счетным входом триггера и входом формирователя импульсов, выход которого соединен с Входом управления записью и считыванием Ооперативного запоминающего устройства, адресные входы которого соединены соответственно с Выходами счетчика, выходы первого регистра соедицены соответственно с информационными 15 входами оперативного запоминающегоустройства и соединены соответственно с информационными входамц первойгруппы и-разрядного сумматора, Входывторой.,группы которого соединены соответственно с выходами элементов НЕвычитателя, входы которых соединенысоответственно с выходами Второго ие, гУжгород, ул, Проектная

СмотретьЗаявка

3974808, 11.11.1985

ГОРЬКОВСКИЙ ИССЛЕДОВАТЕЛЬСКИЙ ФИЗИКО-ТЕХНИЧЕСКИЙ ИНСТИТУТ ПРИ ГОРЬКОВСКОМ ГОСУДАРСТВЕННОМ УНИВЕРСИТЕТЕ ИМ. Н. И. ЛОБАЧЕВСКОГО

МАКАРОВ НИКОЛАЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 7/50

Метки: последовательно, поступающих, суммирования, чисел

Опубликовано: 07.07.1987

Код ссылки

<a href="https://patents.su/4-1322262-ustrojjstvo-dlya-summirovaniya-posledovatelno-postupayushhikh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования последовательно поступающих чисел</a>

Предыдущий патент: Конвейерное вычислительное устройство

Следующий патент: Устройство для определения модуля разности двух чисел

Случайный патент: Трехходовой клапан