Устройство для генерирования цифровых сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1314324

Авторы: Кушнаренко, Лигинов, Чернориз

Текст

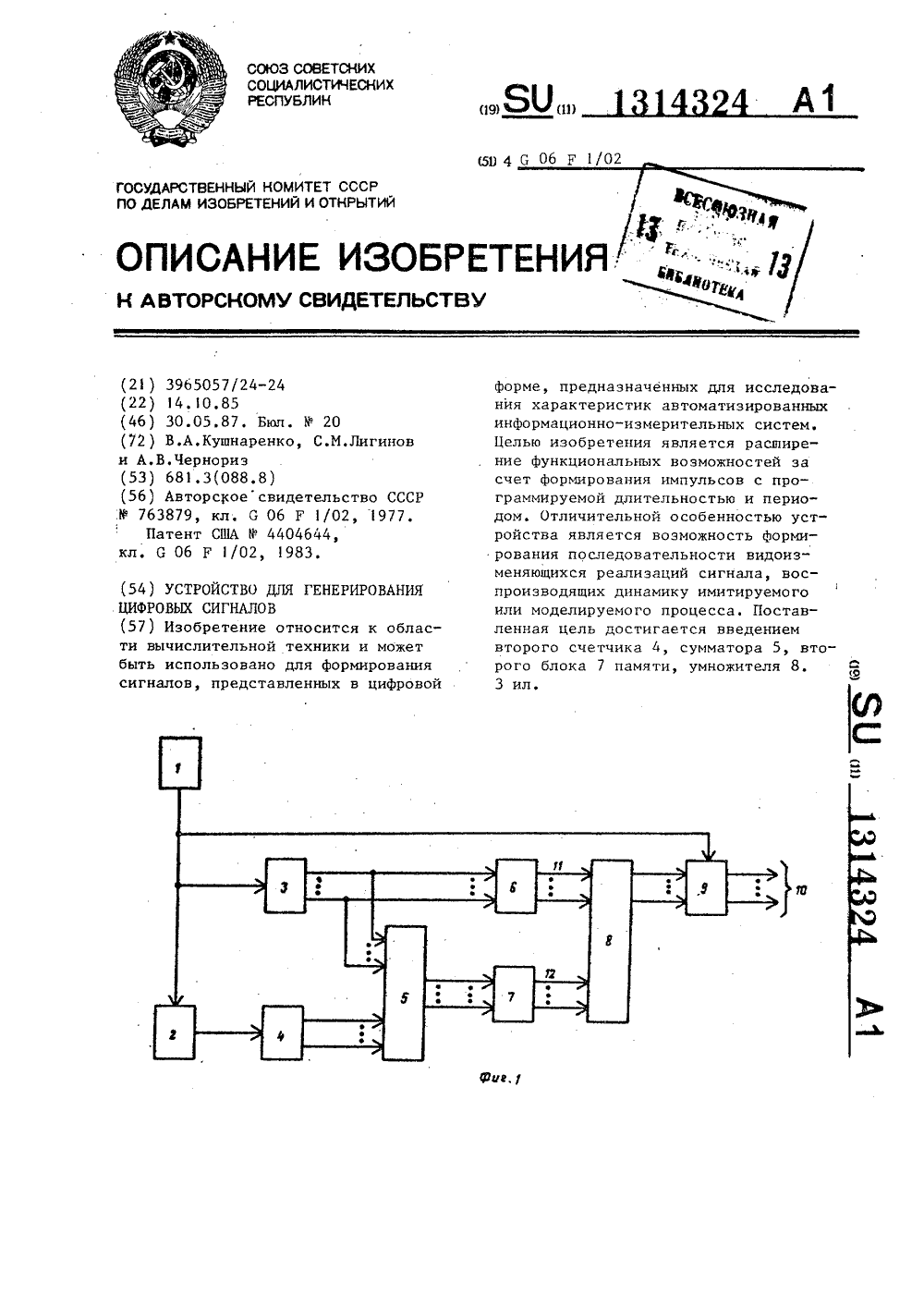

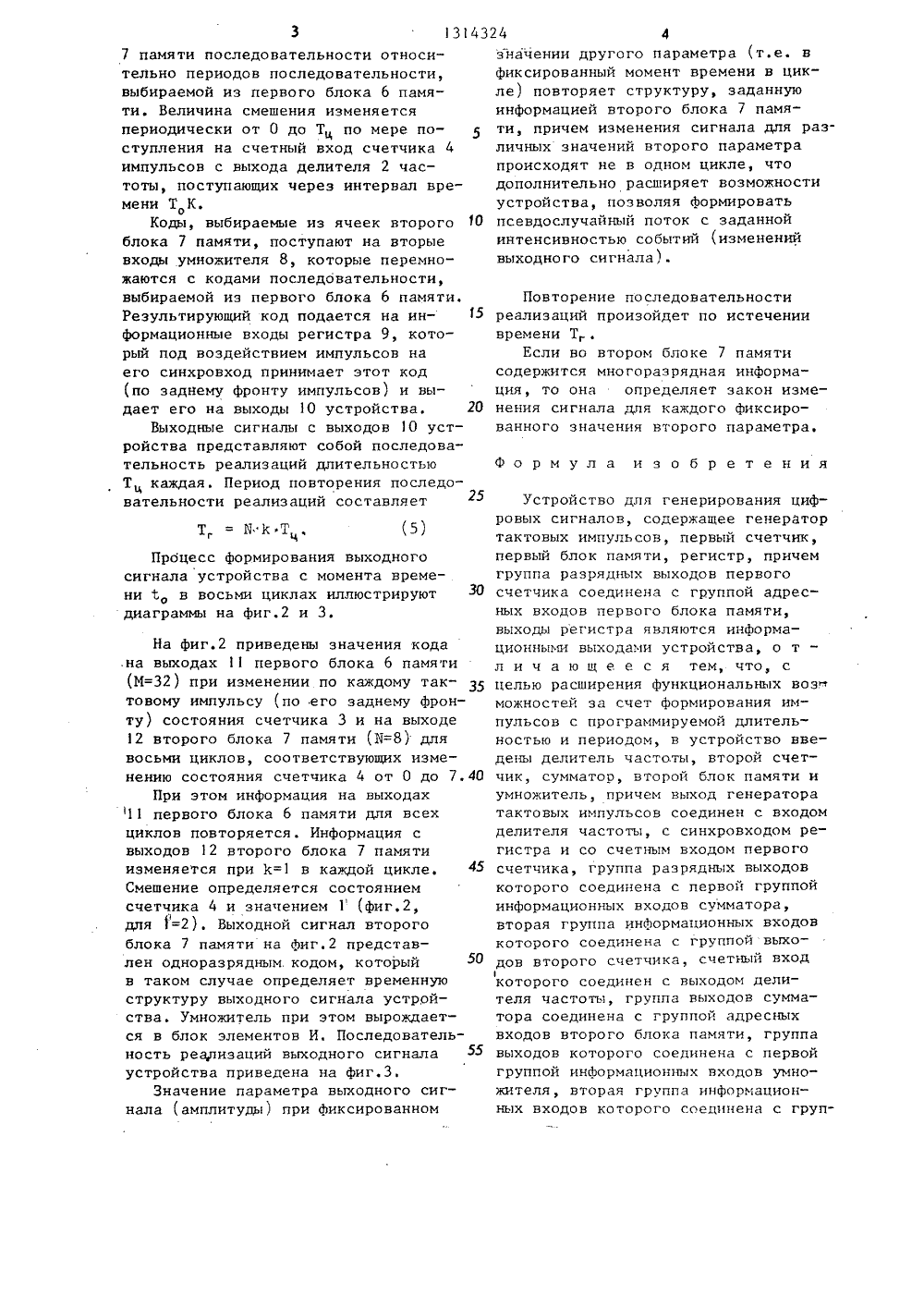

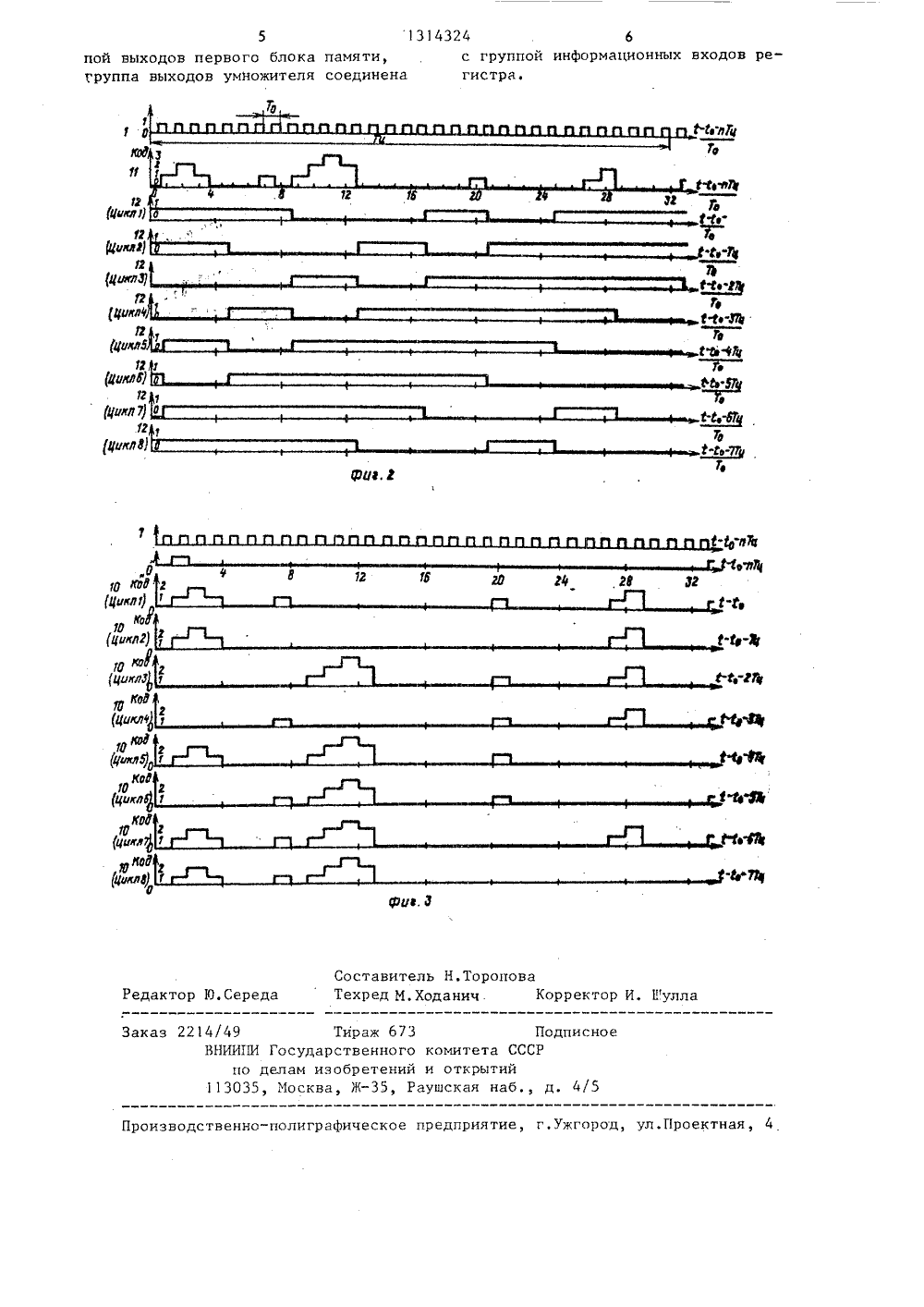

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК А 1 П 9) И 1) РЕТ САНИ Лигино ство СССР2, 1977. ГЕНЕРИРОВАНИЯ к обласможетосит хник вто 8. ть использованоигналов, представ я формиров нных в циф и ГОСУДАРСТВЕННЫЙ НОМИТЕТ ССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫ ВТОРСКОМУ СВИДЕТЕЛЬСТВУ(54) УСТРОЙСТВО ДЛЯЦИФРОВЫХ СИГНАЛОВ(57) Изобретениети вычислительной форме, предназначенных для исследования характеристик автоматизированныхинформационно-измерительных систем.Целью изобретения является расширение функциональных возможностей засчет формирования импульсов с программируемой длительностью и периодом. Отличительной особенностью устройства является воэможность формирования последовательности видоизменяющихся реализаций сигнала, воспроизводящих динамику имитируемогоили моделируемого процесса. Поставленная цель достигается введениемвторого счетчика 4, сумматора 5,рого блока 7 памяти, умножителя3 ил.Изобретение относится к автоматике и вычислительной технике и можетбыть использовано для формированиясигналов, представленных в цифровойформе, предназначенных для отладки,контроля и исследования характеристик автоматизированных информационно-измерительных систем, систем обработки информации и автоматизированных систем контроля,Целью изобретения является расширение функциональных возможностейза счет формирования импульсов с программируемой длительностью и периодом,На фиг.1 изображена структурнаясхема предлагаемого устройства; нафиг.2 - временная диаграмма выходных сигналов первого и второго блоковпамяти в последовательных циклах;на фиг.3 - то же, устройства для информации в блоках памяти.Устройство содержит генератортактовых импульсов, делитель 2 частоты, счетчики 3 и 4, сумматор 5,блоки 6 и 7 памяти, умножитель 8,регистр 9, информационные выходы 10Фустройства, выходы 11 первого блока6 памяти, выходы 12 второго блока 7памяти,Устройство работает следующим образом.В первом блоке 6 памяти, имеющем М ячеек, и во втором блоке 7 памяти, имеющем И ячеек, записаны последовательности цифровых. кодов (характеризующие, например, значения амплитуд сигнала в дискретные моменты времени), которые считываются в процессе работы устройства и используются для формирования реализаций выходного сигнала. Выходной сигнал устройства представлен в цифровой Форме, причем каждое из его значений получается перемножением кода последовательности, выбираемой из первого блока 6 памяти и кода последова - тельности, выбираемой из второго блока 7 памяти.Выбор последовательности из первого блока 6 памяти осуществляет счетчик 3, имеющий модуль пересчета М. По мере поступления на его счетный вход периодической последовательности импульсов, вырабатываемой генератором 1 тактовых импульсов, счетчик 3 формирует адреса ячеек первого блока 6 памяти, содержимое35К=1 сМ,где К = 1 2, 3; т.е. период поступления импульсов на счетный входсчетчика 4 относится к Тц как 1,2, 3,О При выполнении условия (3) длительность цикла опроса И ячеек второгоблока 7 памяти определяется толькопериодом смены кодов на первых входах сумматора 5, который может быть45 увеличен с целью выполнения условия(2) отключением одного или несколькихвыходов, соответствующих младшим разрядам счетчика 3, от входов сумматора 5. Это дает соотношение для выбо 50 ра величин М и 142 )М,Е(4)где е = О, 1, 2, 3- количествоотключенных от входов сумматора 555 выходов счетчика 3.Значение кода на вторых входахсумматора 5 определяет временноесмешение выбираемой из второго блока(3) которых при этом поступает в видепериодической последовательностицифровых кодов на входы умножителя8. Период Т, последовательности(цикл формирования одной реализации)равен длительности цикла опроса Мячеек первого блока 6 памяти(1)где Т - период следования импульсов.Одновременно с выбором последовательности кодов из первого блока 6памяти осуществляется также выборданных из второго блока 7 памяти,длительность Тг, цикла опроса 11 ячеек которого равна Т,Ц 1 )Т = Т , = Т , (2)Адреса ячеек второго блока 7 памяти формируются сумматором 5, осуществляющим сложение по модулю Б кода, поступающего на его первые вхо 25ды с выходов счетчика 3, с значением,поступающим на его вторые входы свыходов счетчика 4, имеющего модульпересчета И.Импульсы, наращнвающие счетчик 4,поступают на его счетный вход от генератора 1 тактовых импульсов через делитель 2 частоты, коэффициентделения К которого удовлетворяетусловию3 131437 памяти последовательности относительно периодов последовательности,выбираемой из первого блока 6 памяти. Величина смешения изменяетсяпериодически от О до Тц по мере поступления на счетный вход счетчика 4импульсов с выхода делителя 2 частоты, поступающих через интервал времени Т К,Коды, выбираемые из ячеек второго 10блока 7 памяти, поступают на вторыевходы умножителя 8, которые перемножаются с кодами последовательности,выбираемой из первого блока 6 памяти.Результирующий код подается на информационные входы регистра 9, который под воздействием импульсов наего синхровход принимает этот код(по заднему фронту импульсов) и выдает его на выходы 10 устройства. 20Выходные сигналы с выходов 10 устройства представляют собой последовательность реализаций длительностьюТ, каждая, Период повторения последовательности реализаций составляет(5)Т= И КПрбцесс формирования выходного сигнала устройства с момента времени 1 в восьми циклах иллюстрируют диаграммы на фиг.2 и 3.На фиг.2 приведены значения кода ,на выходах 11 первого блока 6 памяти (М=32) при изменении по каждому тактовому импульсу (по его заднему фронту) состояния счетчика 3 и на выходе 12 второго блока 7 памяти (И=8) для восьми циклов, соответствующих изменению состояния счетчика 4 от О до 7.40При этом информация на выходах 11 первого блока 6 памяти для всех циклов повторяется. Информация с выходов 12 второго блока 7 памяти изменяется при 1=1 в каждой цикле. 45 Смешение определяется состоянием счетчика 4 и значением 1 (фиг.24для 1=2). Выходной сигнал второго блока 7 памяти на фиг.2 представлен одноразрядным. кодом, который50 в таком случае определяет временную структуру выходного сигнала устройства. Умножитель при этом вырождается в блок элементов И. Последовательность реализаций выходного сигнала 55 устройства приведена на фиг.3.Значение параметра выходного сигнала (амплитуды) при фиксированном 24 4значении другого параметра (т.е. в фиксированный момент времени в цикле) повторяет структуру, заданную информацией второго блока 7 памяти, причем изменения сигнала для различных значений второго параметра происходят не в одном цикле, что дополнительно расширяет возможности устройства, позволяя формировать псевдослучайный поток с заданной интенсивностью событий (изменений выходного сигнала)Повторение последовательностиреализаций произойдет по истечении времени Т.Если во втором блоке 7 памятисодержится многоразрядная информация, то она определяет закон изменения сигнала для каждого фиксированного значения второго параметра.Формула изобретенияУстройство для генерирования цифровых сигналов, содержащее генератор тактовых импульсов, первый счетчик, первый блок памяти, регистр, причем группа разрядных выходов первого счетчика соединена с группой адресных входов первого блока памяти, выходы регистра являются информационными выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных воз можностей за счет формирования импульсов с программируемой длительностью и периодом, в устройство введены делитель частоты, второй счетчик, сумматор, второй блок памяти и умножитель, причем выход генератора тактовых импульсов соединен с входом делителя частоты, с синхровходом регистра и со счетным входом первого счетчика, группа разрядных выходов которого соединена с первой группой информационных входов сумматора, вторая группа информационных входов которого соединена с группой выходов второго счетчика, счетный вход 1которого соединен с выходом делителя частоты, группа выходов сумматора соединена с группой адресных входов второго блока памяти, группа выходов которого соединена с первой группой информационных входов умно- жителя, вторая группа информационных входов которого соединена с груп1314324 6с группой информационных входов регистра. пой выходов первого блока памяти,группа выходов умножителя соединена икр12 ю фвоб фикп 7 то фф 4 икл 7)ко (цикл 4 701 Циюф,ки и лД эфф и 41 О цикл иилкксд 4 Ъа 1 ф Тираж 673 Государственного делам изобретений Москва, Ж, Р

СмотретьЗаявка

3965057, 14.10.1985

ПРЕДПРИЯТИЕ ПЯ Г-4746

КУШНАРЕНКО ВАЛЕРИЙ АНДРЕЕВИЧ, ЛИГИНОВ СЕРГЕЙ МИХАЙЛОВИЧ, ЧЕРНОРИЗ АНАТОЛИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 1/02

Метки: генерирования, сигналов, цифровых

Опубликовано: 30.05.1987

Код ссылки

<a href="https://patents.su/4-1314324-ustrojjstvo-dlya-generirovaniya-cifrovykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для генерирования цифровых сигналов</a>

Предыдущий патент: Устройство для фиксации рычага тумблера

Следующий патент: Функциональный генератор

Случайный патент: Аппарат для выращивания микроорганизмов