Цифровой генератор синусоидальных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1223328

Автор: Шумаев

Текст

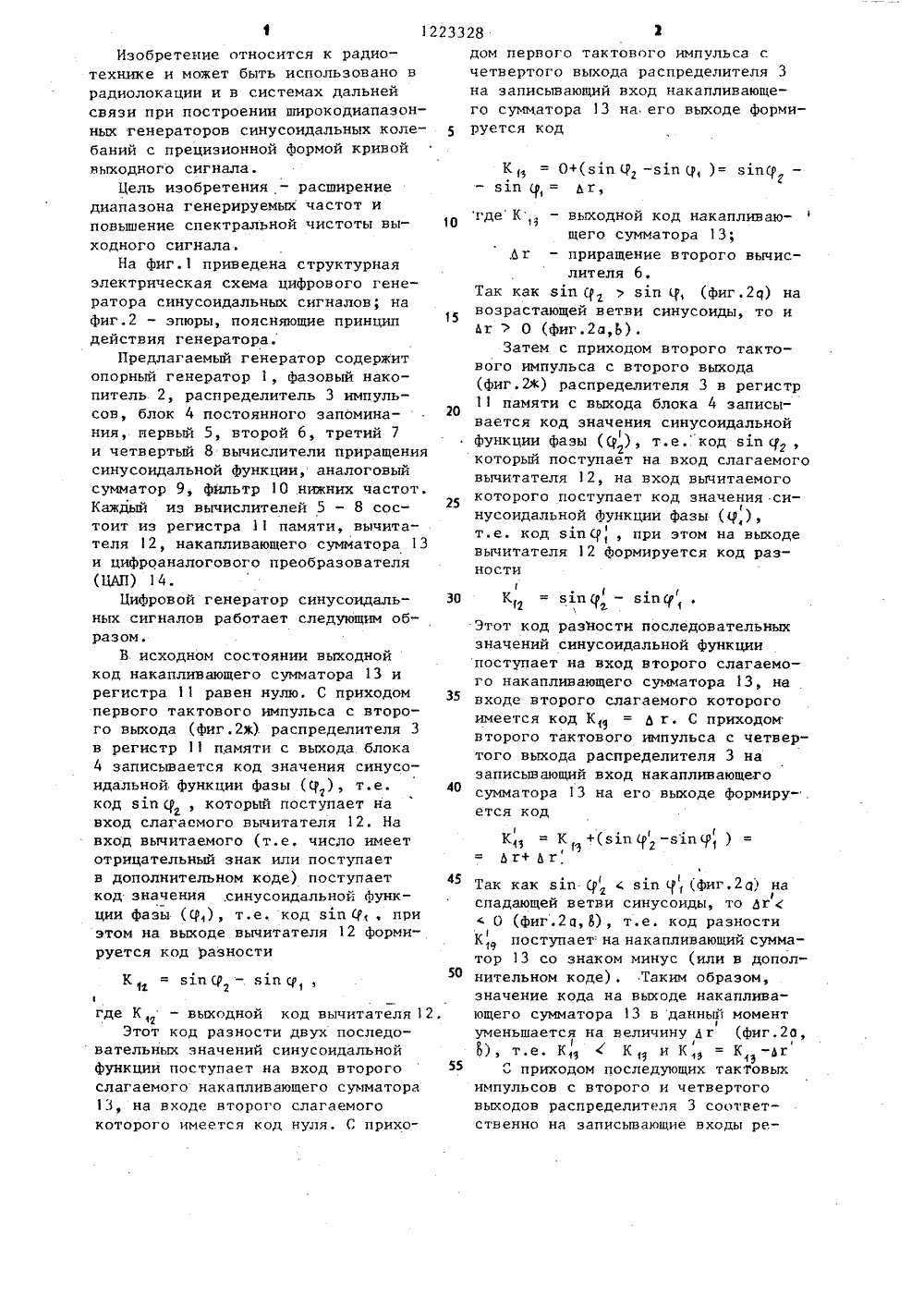

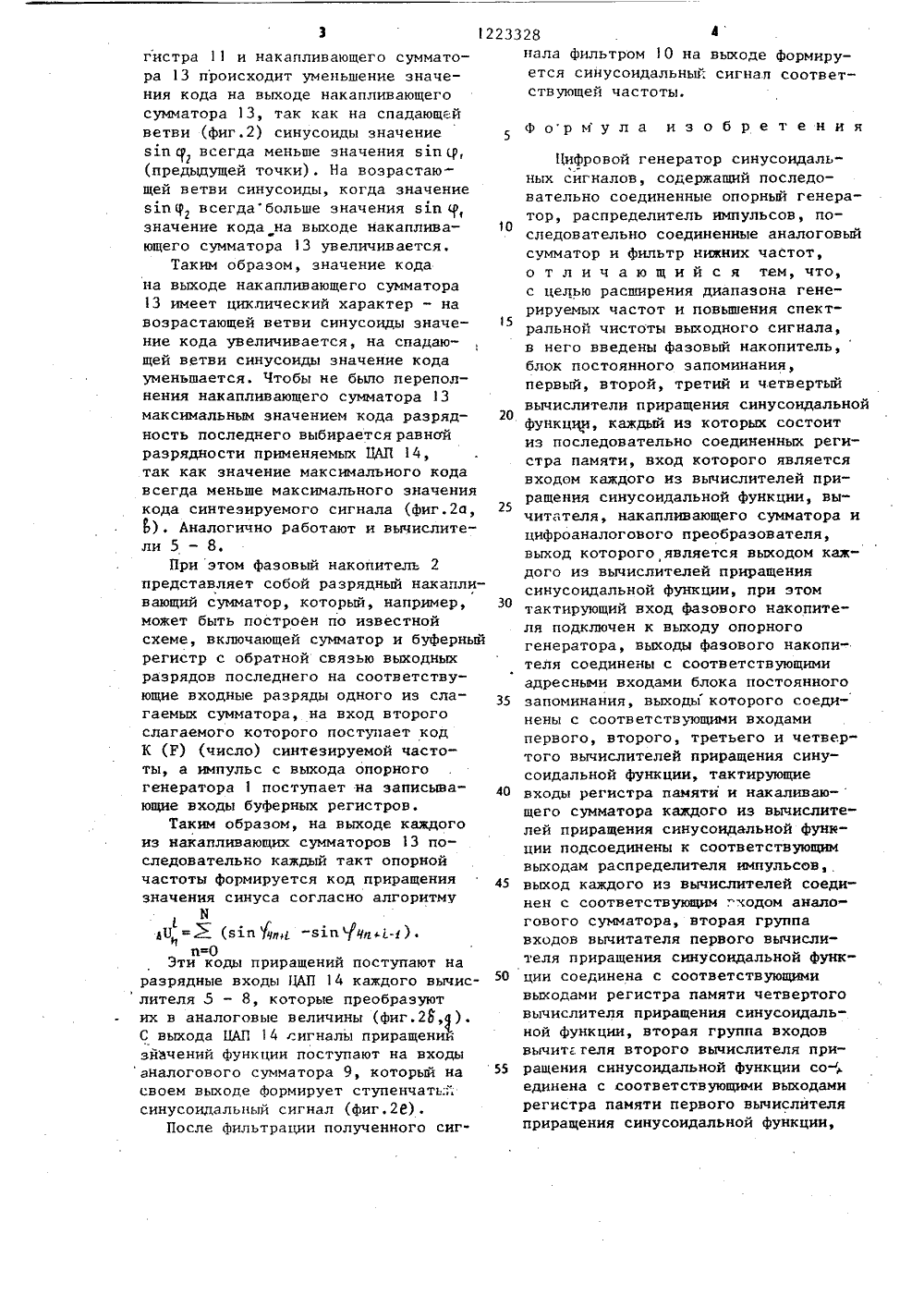

СОЮЗ С 08 ЕТСКИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК УДАРСТ 8 ЕННЫЙ КОМИТЕТ СССРДЕЛАМ ИЗОБРЕТЕНИЙ И ОП.1 РЫТИЙ ПИСАНИЕ ИЭОБРЕТ ТОРСНОМУ СВИДЕТЕЛЬСТВУ аналоговый сумматор 9, фильтр нижнихчастот (ФНЧ) 1 О и четыре вычислителя5,6,7,8 приращения синусоидалънойфункции, каждый из которых состоитиз регистра 11 памяти, вычитателя12, накапливающего сумматора 13 ицифроаналогового преобразователя(ЦАП) 14. Код К (Р) синтезируемойчастоты накапливается в фазовомнакопителе 2, затем запоминается вБПЗ 4 и в регистры 1 памяти записываются коды значения синусоидальной функции фазы. Затем формируемыевычитателями 12 коды разности поступают в накапливающие сумматоры13, имеющие циклический характер.Формируемые ими коды приращениязначения синуса преобразуются вЦАП 14 в аналоговые величины, которые формируются в аналоговом сумматоре 9 в ступенчатый синусоидальныйсигнал, После фильтрации в ФНЧ 1 Она выходе цифрового генератора формируется синусоидальный сигналсоответствующей частоты. 2 ил. ко аев(54) ЦИФРОВОЙ ГЕНЕРАТОР СИНУСОИДАЛЬНЫХ СИГНАЛОВ(57) Изобретение относится к радиотехнике. Расширяется диапазон генерируемых частот и повышается спектральная чистота выходного сигнала.Цифровой генератор содержит опорныйгенератор 1, фазовый накопитель 2,распределитель 3 импульсов, блокпостоянного запоминания (БПЗ) 4,(21) 368696/24-0946. Бюл.Р 13ий ордена Дружбы нароический институт ЯО 1223328 А1 О 20 25 30 35 40 50 Изобретение относится к радиотехнике и может быть использовано в радиолокации и в системах дальней связи при построении широкодиапазонных генераторов синусоидальных колебаний с прецизионной формой кривой выходного сигнала.Цель изобретения - расширение диапазона генерируемых частот и повышение спектральной чистоты выходного сигнала,На фиг. приведена структурная электрическая схема цифрового генератора синусоидальных сигналов; на фиг.2 - эпюры, поясняющие принцип действия генератора.Предлагаемый генератор содержит опорный генератор 1, Фазовый накопитель 2, распределитель 3 импульсов, блок 4 постоянного запоминания, первый 5, второй 6, третий 7 и четвертый 8 вычислители приращения синусоидальной функции, аналоговый сумматор 9, Фильтр 10 нижних частот. Каждый из вычислителей 5 - 8 состоит из регистра 11 памяти, вычитателя 12, накапливающего сумматора 13 и цифроаналогового преобразователя (ЦАП) 14.Цифровой генератор синусоидальных сигналов работает следующим образом.В исходном состоянии выходной код накапливающего сумматора 13 и регистра 11 равен нулю, С приходом первого тактового импульса с второго выхода (Фиг.2 Ж). распределителя 3 в регистр 11 памяти с выхода блока 4 записывается код значения синусоидальной функции Фазы ( ), т,е. код в 1 п, который поступает на вход слагаемого вычитателя 12. На вход вычитаемого (т.е. число имеет отрицательный знак или поступает в дополнительном коде) поступает код значения ,сннусоидальной Функции Фазы ), т.е. код в 1 п 9 при этом на выходе вычитателя 12 формируется код разности К = в 1 п - в 1 п д где К - выходной код вычитателя 12.Этот код разности двух последовательных значений синусоидальной функции поступает на вход второго слагаемого накапливающего сумматора 13, на входе второго слагаемого которого имеется код нуля. С приходом первого тактового импульса счетвертого выхода распределителя 3на записывающий вход накапливающего сумматора 13 на его выходе формируется код К = О+(я 1 п Ц -в 1 п ц, )= я 1 п(в 1.п у, = Ь где К, - выхоДной коД накапливающего сумматора 13;,д г - приращение второго вычислителя 6,Так как в 1 п (в 1 п Ч, (Фиг.2 ц) навозрастающей ветви синусоиды, то идг ) О (Фиг.2 д,5).Затем с приходом второго тактового импульса с второго выхода(фиг.2 ж) распределителя 3 в регистр11 памяти с выхода блока 4 записывается код значения синусоидальнойфУнкции фазы (Щ ), т.е. код в 1 п дг,г фкоторый поступает на вход слагаемоговычитателя 12, на вход вычитаемогокоторого поступает код значения синусоидальной функции Фазы (9),т.е. код в 1 п ( при этом на выходевычитателя 12 Формируется код разностиК я 1 п ( в 1 пЭтот код разности последовательныхзначений синусоидальной функциипоступает на вход второго слагаемого накапливающего сумматора 13, навходе второго слагаемого которогоимеется код К 5 = Ь г. С приходомвторого тактового импульса с четвертого выхода распределителя 3 назаписывающий вход накапливающегосумматора 13 на его выходе Формиру- .ется кодКц К +(в 1 п (г Я 1 п ) Ьг+ дг1Так как в 1 п ф с в 1 п , (фиг,2 а,1 на спадающей ветви синусоиды, то дг ( с О (фиг.2 ц, 3), т.е. код разности К, поступает на накапливающий сумматор 13 со знаком минус (или в дополнительном коде). Таким образом, значение кода на выходе накапливающего сумматора 13 в данный момент уменьшается на величину д г (фиг,2 о, ), т.е. К, С Кц и К = Кц-дг" приходом последующих тактовых импульсов с второго и четвертого выходов распределителя 3 соответственно на записывающие входы ре12233 гистра 11 и накапливающего сумматора 13 происходит уменьшение значения кода на выходе накапливающегосумматора 13, так как на спадающейветви (Фиг.2) синусоиды значениезьпвсегда меньше значения зьп ц),(предыдущей точки). На возрастающей ветви синусоиды, когда значениез 1 пвсегдабольше значения з 1 п ,значение кода на выходе накапливающего сумматора 13 увеличивается,Таким образом, значение кодана выходе накапливающего сумматора13 имеет циклический характер - навозрастающей ветви синусоиды значение кода увеличивается, на спадающей ветви синусоиды значение кодауменьшается. Чтобы не бьцю переполнения накапливающего сумматора 13максимальным значением кода разрядность последнего выбирается равнойразрядности применяемых ЦАП 14,так как значение максимального кодавсегда меньше максимального значениякода синтезируемого сигнала (фиг.2 а, 255). Аналогично работают и вычислители 5 - 8.При этом фазовый накопитель 2представляет собой разрядный накапливающий сумматор, который, например, Зоможет быть построен по известнойсхеме, включающей сумматор и буферныйрегистр с обратной связью выходныхразрядов последнего на соответствующие входные разряды одного из слагаемых сумматора, на вход второгослагаемого которого поступает кодК (Р) (число) синтезируемой частоты, а импульс с выхода опорногогенератора 1 поступает на записывающие входы буферных регистров.Таким образом, на выходе каждогоиз накапливающих сумматоров 13 последовательно каждый такт опорнойчастоты формируется код приращениязначения синуса согласно алгоритмуИУ .: (выл, -эьпЧпа)Ии ОЭти коды приращений поступают наразрядные входы ЦАП 14 каждого вычислителя 5 - 8, которые преобразуютих в аналоговые величины (фиг.23,).С выхода ЦАП 14 сигналы приращениизйЗчений функции поступают на входыаналогового сумматора 9, который насвоем выходе Формирует ступенчать.синусоидальный сигнал (Фиг,20),После фильтрации полученного сиг 28 4нала фильтром 1 О на выходе формируется синусоидальный сигнал соответствующей частоты. Формула изобретения Цифровой генератор синусоидаль"ных сигналов, содержащий последовательно соединенные опорный генератор, распределитель импульсов, последовательно соединенные аналоговыйсумматор и фильтр нижних частот,отличающийся тем, что,с целью расширения диапазона генерируемых частот и повышения спектральной чистоты выходного сигнала,в него введены Фазовый накопитель,блок постоянного запоминания,первый, второй, третий и четвертыйвычислители приращения синусоидальнойФункции, каждый из которых состоитиз последовательно соединенных регистра памяти, вход которого являетсявходом каждого из вычислителей приращения синусоидальной Функции, вычитателя, накапливающего сумматора ицифроаналогового преобразователя,выход которого является выходом каждого из вычислителей приращениясинусоидальной Функции, при этомтактирующий вход Фазового накопите"ля подключен к выходу опорногогенератора, выходы фазового накопителя соединены с соответствующимиадресными входами блока постоянногозапоминания, выходы которого соединены с соответствующими входамипервого, второго, третьего и четвертого вычислителей приращения синусоидальной функции, тактирующиевходы регистра памяти и накаливающего сумматора каждого из вычислителей приращения синусоидальной фунюции подсоединены к соответствующимвыходам распределителя импульсов,выход каждого из вычислителей соединен с соответствующим ".ходом аналогового сумматора, вторая группавходов вычитателя первого вычислителя приращения синусоидальной функции соединена с соответствующимивыходами регистра памяти четвертоговычислителя приращения синусоидальной функции, вторая группа входоввычит геля второго вычислителя приращения синусоидальной функции со-,.единена с соответствующими выходамирегистра памяти первого вычислителяприращения синусоидальной функции,1223328 ЮЮ оставитель В.Рудаехред О,Сопко ек тор 11. Де едактор А.Шишкина аказ 1722 57 130 Пат лиал вторая группа входов вычитателятретьего вычислителя приращения синусоидальной функции соединена ссоответствующими выходами регистрапамяти второго вычислителя приращения синусоидальной функции, втоТираж 816 ВНИИПИ Государст по делам изобр 35, Москва, Жрая группа входов вычитателя четвертого вычислителя приращения синусоидальной функции соединена с соответствующими выходами регистра памяти третьего вычислителя приращениясинусоидальной функции,Подписноеенного комитета СССРтений и открытийРаушская наб д,4/5 г.ужгород, ул,Проектная,

СмотретьЗаявка

3686963, 04.01.1984

МАРИЙСКИЙ ОРДЕНА ДРУЖБЫ НАРОДОВ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. А. М. ГОРЬКОГО

ШУМАЕВ ВЛАДИМИР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: H03B 19/00

Метки: генератор, сигналов, синусоидальных, цифровой

Опубликовано: 07.04.1986

Код ссылки

<a href="https://patents.su/4-1223328-cifrovojj-generator-sinusoidalnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой генератор синусоидальных сигналов</a>