Аналого-цифровой девиометр

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1182428

Автор: Хайкин

Текст

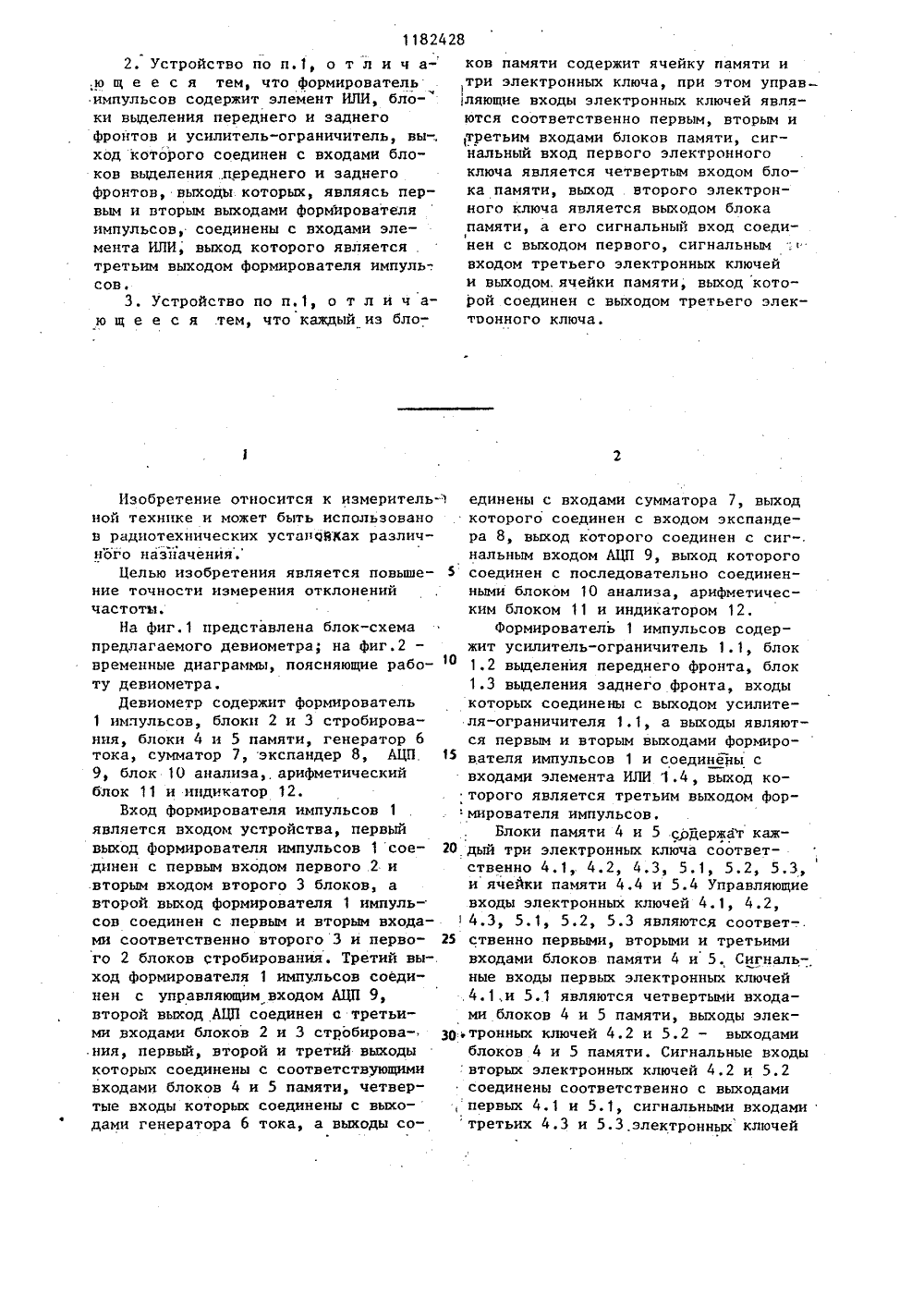

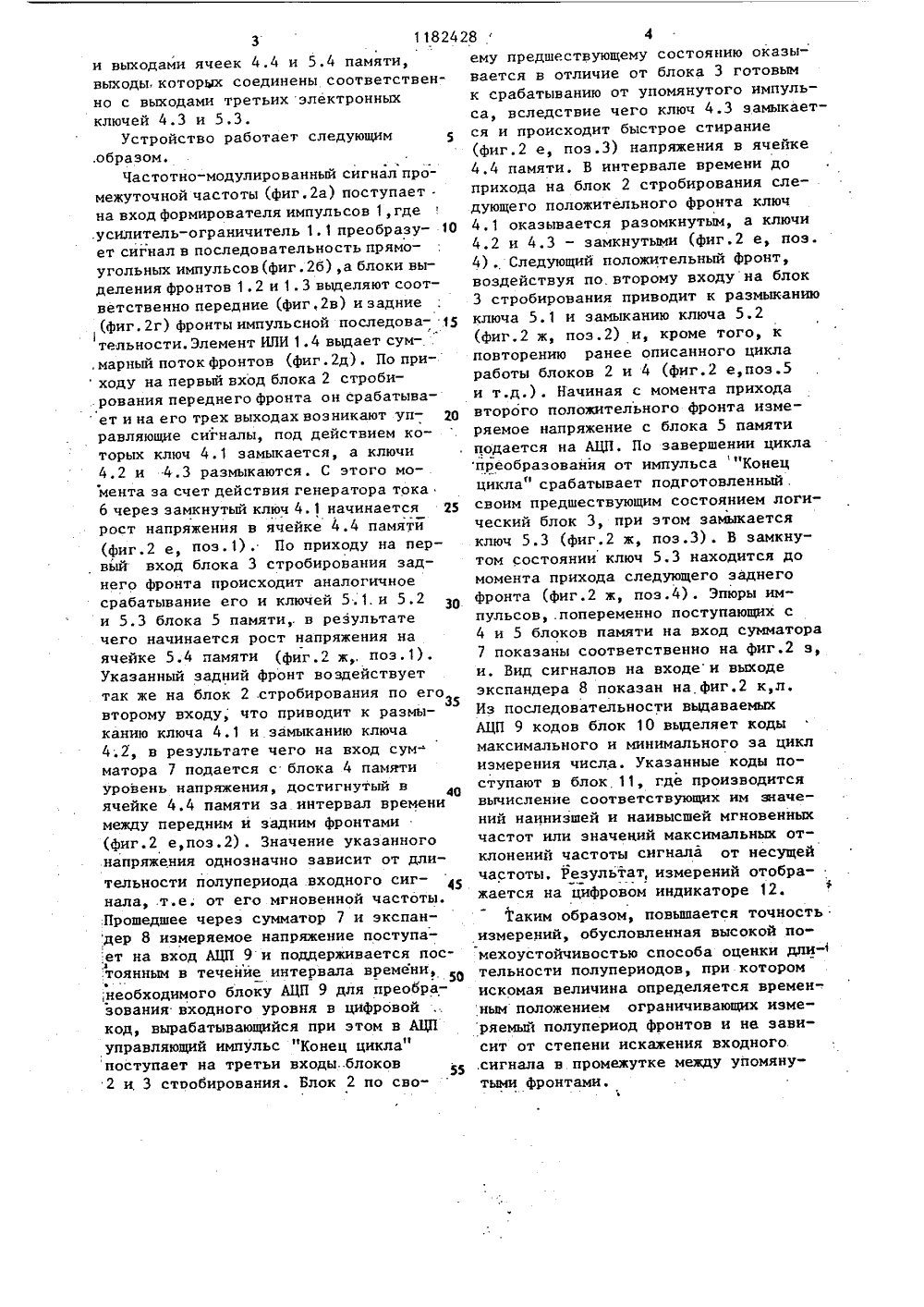

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК ОСУДАРСТВЕННЫИ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ ОПИСАНИЕ ИЗОБРЕТН АВТОРСКОМУ СВИДЕТЕЛЬСТВУ детельство СССР01 В 23/00, 1982(54) (57) 1, АНАЛОГО-ЦИФРОВОЙ МЕТР, содержащий формировател сов, блок .памяти и последоват единенные аналого-цифровой пр ватель (АЦП), блок анализа, а ческий блок и индикатор, о т ю щ и й с я тем, что, с цель щения точности измерения, вдены второй блок памяти, перв второй блоки стробирования, г ДЕВИ ь импульельно со еобразо- рифметил и ч авходами бло ены с соответствующ ков памяти, ч соединены с в а выходы блок ходы котор тверты иодами в памя генератора токи соединены с овыго умматором ого соедин иод ко ндера, нальньп ый с входом эксп соединен с си ороАЦП ыход енерат о(21) 3663878/ (22) 16.11,83 (46) 30.09.85 (72) Е.М.Хайк :(53) 621.317( (56) Гитис Э.Е го-цифровые пр гоиздат, 1981Авторское с898338, кл. Бюл.36и88.8)Пискулов Е.А. Аналоеобразователи. - М. Энертока, сумматор и экспандер, при этомвходом устройства является вход формирователя импульсов, первый выход которого соединен с первым входом первогои вторым входом второго блоков стробирования, второй выход формирователя,импульсов соединен с первымИ вторымвходами соответственно второго и первого блоков стробирования, третий выход формирователя импульсов соединенс управляющим входом АЦП, второй выход которого соединен с третьими входами блоков стробирования, первый,второй и третий выходы которых соедиков памяти содержит ячейку памяти и,три электронных ключа, при этом управляющие входы электронных ключей являются соответственно первым, вторым итретьим входами блоков памяти, сигнальный вход первого электронногоключа является четвертым входом блока памяти, выход второго электронного ключа является выходом блокапамяти, а его сигнальный вход соеди 1нен с выходом первого, сигнальнымвходом третьего электронных ключейи выходом, ячейки памяти, выход которой соединен с выходом третьего электоонного ключа. 11824282. Устройство по п.1, о т л и ч а,ю щ е е с я тем, что формировательимпульсов содержит элемент ИЛИ, блоки выделения переднего и заднегофронтов и усилитель-ограничитель, вы-.,ход которого соединен с входами блоков выделения, переднего и заднегофронтов, выходы которых, являясь первым и вторым выходами формирователяимпульсов, соединены с входами элемента ИЛИ, выход которого является .третьим выходом формирователя импуль".сов,3Устройство по п.1, о т л и ч аю щ е е с я тем, что кажпый из бло5 1 О ся первым и вторым выходами формирователя импульсов 1 и соединены свходами элемента ИЛИ 1.4, выход которого является третьим выходом фор:мирователя импульсов.Блоки памяти 4 и 5 содержат каж дый три электронных ключа соответственно 4.1, 4.2, 4.3, 5.1, 5.2, 5.3,и ячейки памяти 4.4 и 5.4 Управляющиевходы электронных ключей 4.1, 4.2,ЗОьтронных ключей 4.2 и 5.2 - выходами Изобретение относится к измерительной технике и может быть использовано в радиотехнических устанцйХах различного назначения.Целью изобретения является повышение точности измерения отклонений частоты.На фиг.1 представлена блок-схема предлагаемого девиометра; на фиг.2 - временные диаграммы, поясняющие работу девиометра.Девиометр содержит формирователь 1 импульсов, блоки 2 и 3 стробирования, блоки 4 и 5 памяти, генератор 6 тока, сумматор 7, экспандер 8, АЦП.9, блок 10 анализа арифметический блок 11 и индикатор 12.Вход формирователя импульсов 1 является входом устройства, первый выход формирователя импульсов 1 соединен с первым входом первого 2 и .вторым входом второго 3 блоков, а второй выход формирователя 1 импуль-. сов соединен с первым и вторым входами соответственно второго 3 и перво го 2 блоков стробирования. Третий вы-. ход формирователя 1 импульсов соединен с управляющим входом АЦП 9, второй выход АЦП соединен а третьими входами блоков 2 и 3 стробирова.ния, первый, второй и третий выходы которых соединены с соответствующими входами блоков 4 и 5 памяти, четвертые входы которых соединены с выходами генератора 6 тока, а выходы соединены с входами сумматора 7, выход которого соединен с входом экспандера 8, выход которого соединен с сиг-. нальным входом АЦП 9, выход которого соединен с последовательно соединенными блоком 10 анализа, арифметическим блоком 11 и индикатором 12.Формирователь 1 импульсов содержит усилитель-ограничитель 1.1, блок 1.2 выделения переднего фронта, блок 1.3 выделения заднего фронта, входы которых соединены с выходом усилителя-ограничителя 1.1, а выходы являют 4.3, 5.1, 5.2, 5.3 являются соответ-. ственно первыми, вторыми и третьимивходами блоков памяти 4 и 5. Сигнальные входы первых электронных ключей4.1.,и 5.1 являются четвертыми входами блоков 4 и 5 памяти, выходы элекблоков 4 и 5 памяти. Сигнальные входывторых электронных ключей 4.2 и 5.2 соединены соответственно с выходами118243и выходами ячеек 4.4 и 5.4 памяти, выходы:которых соединены соответственно с выходами третьих электронных ключей 4.3 и 5,3.Устройство работает следующим 5 ,образом.Частотно-модулированный сигнал промежуточной частоты (фиг. 2 а) поступает . на вход формирователя импульсов 1, где .усилитель-ограничитель 1, 1 преобразу О ет сигнал в последовательность прямоугольных импульсов (Фиг. 2 б),а блоки выделения фронтов 1. 2 и 1. 3 выделяют соответственно передние (фиг.2 в) и задние (Фиг. 2 г) фронты импульсной последова тельности. Элемент ИЛИ 1.4 выдает сум- , марный поток фронтов (фиг. 2 д) . По при ходу на первый вход блока 2 строби. рования переднего фронта он срабатыва ет и на его трех выходах возникают уп равляющие сигналы, под действием которых ключ 4.1 замыкается, а ключи 4,2 и 4.3 размыкаются. С этого момента за счет действия генератора тока 6 через замкнутый ключ 4.1 начинается 25 рост напряжения в ячейке 4.4 памятй (фиг.2 е, поз. 1) . По приходу на первьй вход блока 3 стробирования заднего фронта происходит аналогичное срабатывание его и ключей 5,1. и 5.2 и 5.3 блока 5 памяти,. в результате чего начинается рост напряжения на ячейке 5.4 памяти (фиг.2 ж поз.1). Указанный задний фронт воздействует так же на блок 2 .стробирования по его второму входу, что приводит к размыканию ключа 4.1 и замыканию ключа 4.2, в результате чего на вход сум" матора 7 подается с блока 4 памяти уровень напряжения, достигнутый в 4 О ячейке 4.4 памяти за.интервал времени между передним и задним фронтами (фиг.2 е,поэ.2) . Значение указанного напряжения однозначно зависит от длительности полупериода входного сиг нала, .т.е. от его мгновенной частоты. ,Прошедшее через сумматор 7 и экспандер 8 измеряемое напряжение поступа- ;ет на вход АЦП 9 и поддерживается пос- ,Ятоянным в течение интервала времени, ;необходимого блоку АЦП 9 для преобразования входного уровня в цифровой код, вырабатывающийся при этом в АЦП управляющий импульс "Конец цикла" поступает на третьи входыблоков2 и 3 стообирования. Блок 2 по сво 28 4ему предшествующему состоянию оказывается в отличие от блока 3 готовым к срабатыванию от упомянутого импульса, вследствие чего ключ 43 замыкается и происходит быстрое стирание (фиг.2 е, поэ.З) напряжения в ячейке 4.4 памяти. В интервале времени до прихода на блок 2 стробирования следующего положительного фронта ключ 4.1 оказывается разомкнутым, а ключи 4.2 и 4.3 - замкнутыми (фиг.2 е, поэ.4) . Следующий положительный фронт, воздействуя по. второму входу на блок 3 стробирования приводит к размыканию ключа 5.1 и замыканию ключа 5.2 (фиг.2 ж, поэ.2) и, кроме того, к повторению ранее описанного цикла работы блоков 2 и 4 (фиг.2 е,поз.5 и т.д.). Начиная с момента прихода второго положительного фронта измеряемое напряжение с блока 5 памяти подается на АЦП. По завершении цикла преобразования от импульса "Конец цикла" срабатывает подготовленный. своим предшествующим состоянием логический блок 3, при этом замыкается ключ 5.3 (фиг.2 ж, поз,З) . В замкнутом состоянии ключ 5.3 находится до момента прихода следующего заднего фронта (фиг.2 ж, поз.4). Эпюры импульсов,.попеременно поступающих с 4 и 5 блоков памяти на вход сумматора 7 показаны соответственно на фиг.2 э, и. Вид сигналов на входе и выходе экспандера 8 показан на фиг.2 к,л, Из последовательности выдаваемых АЦП 9 кодов блок 10 выделяет коды максимального и минимального эа цикл измерения числа. Указанные коды поступают в блок 11, где производится вычисление соответствующих им значений наинизшей и наивысшей мгновенных частот или значений максимальных отклонений частоты сигнала от несущей частоты. Результат, измерений отобраФ жается на цифровом индикаторе 12.таким образом, повышается точность измерений, обусловленная высокой помехоустойчивостью способа оценки длительности полупериодов, при котором искомая величина определяется временным положением ограничивающих измеряемый полупериод фронтов и не зависит от степени искажения входного. ,сигнала в промежутке между упомянутыми Фронтами.1182428 едактор Л .Пчел а а писное 113035 к ПП "Патент", г,ужгород, ул.Проектн фил 6100/43ВНИИПИ Госпо дела Составитель С.ЛебедевТехред Л.Микеш Корректор Л.Бескид Тираж 747рственного комитета СССэобретений и открытийЖ, Раушская наб.,

СмотретьЗаявка

3663878, 16.11.1983

ПРЕДПРИЯТИЕ ПЯ Г-4492

ХАЙКИН ЕВСЕЙ МАРКОВИЧ

МПК / Метки

МПК: G01R 23/00

Метки: аналого-цифровой, девиометр

Опубликовано: 30.09.1985

Код ссылки

<a href="https://patents.su/4-1182428-analogo-cifrovojj-deviometr.html" target="_blank" rel="follow" title="База патентов СССР">Аналого-цифровой девиометр</a>

Предыдущий патент: Устройство для измерения относительной разности частот, отношения частот и частоты

Следующий патент: Цифровой частотомер

Случайный патент: Способ определения игристых свойств напитков