Устройство для исправления одиночных и обнаружения многократных ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

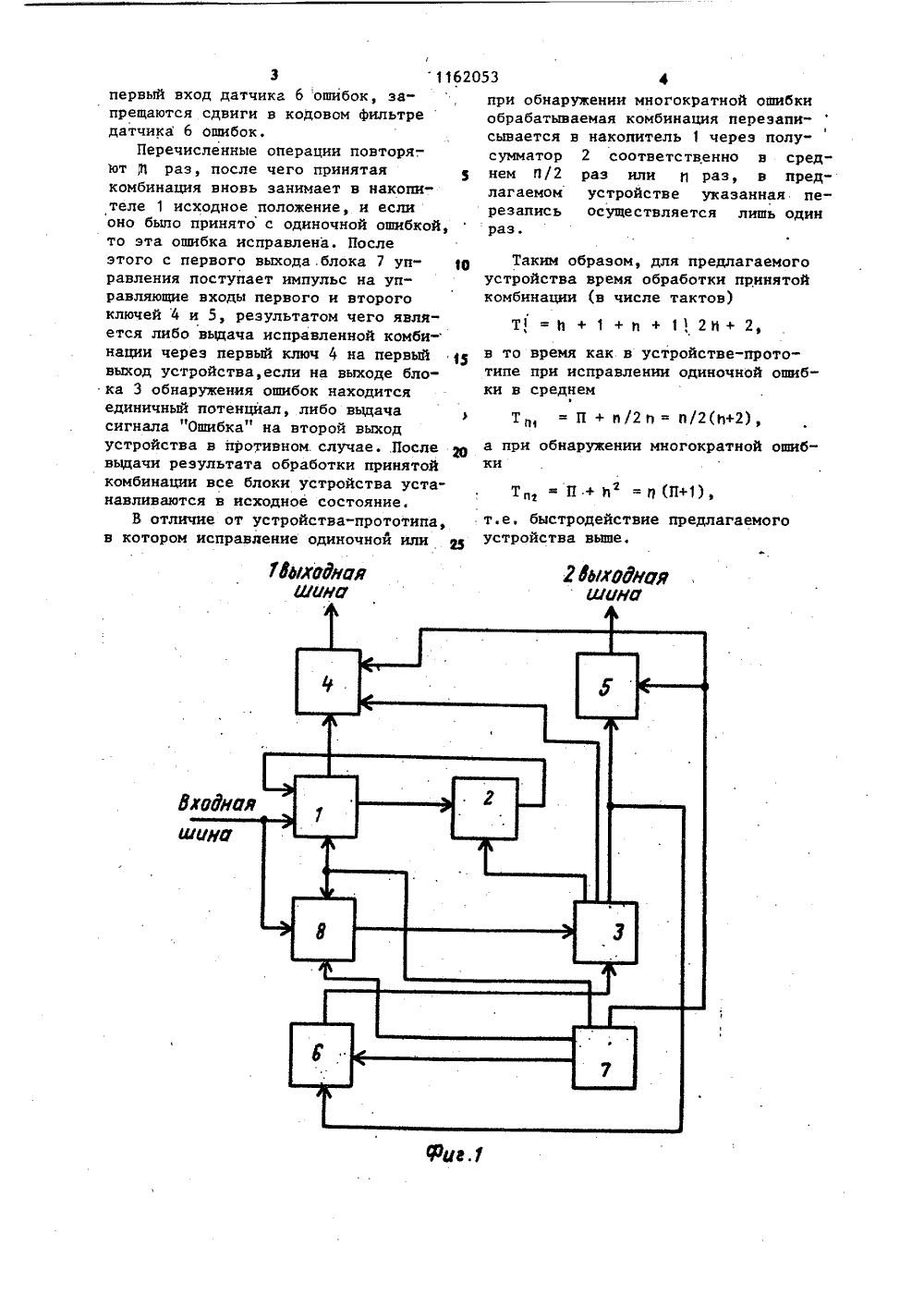

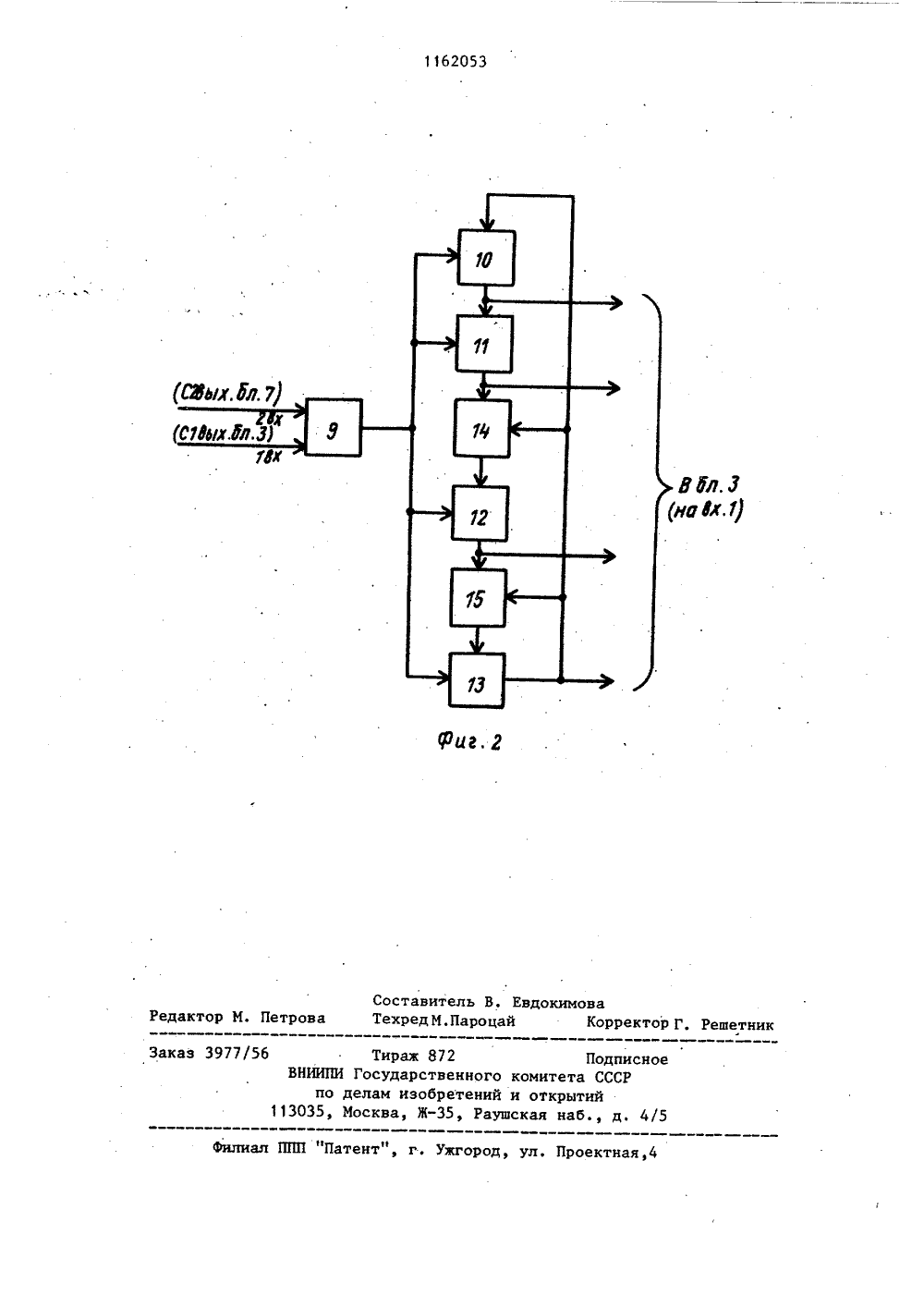

(22 (46 (72 ключенужениярогоок, аобнаругому ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ Н АВТОРСКОМУ СВИДЕТЕЛЬСТ) Г.С. Евсеев и Е.А. Крук (71) Ленинградский институт авиационного приборостроения(54)(57) 1. УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОДИНОЧНЫХ И ОБНАРУЖЕНИЯ МНОГОКРАТНЫХ ОШИБОК, содержащее последовательно соединенные накопитель, первый информационный вход которого является входом устройства, и полу- сумматор, выход которого подключен к второму информационному входу накопителя, второй выход которого подключен к информационному входу первого ключа, к первому управляюще. му входу которого подключен первый выход блока обнаружения ошибок,второй выход которого подключен к первому входу датчика ошибок и к инфор" мационному входу второго ключа, управляющий вход которого объединен с вторым управляющим входом первого ключа и соединен с первым выходом блока управления, второй и третий выходы которого подключены соответственно к управляющему входу накопителя и к второму входу датчика ошибок, причем выходы первого и втоЯО 1 2053 о ключей являются выходами уст роиства, о т л и ч а ю щ е е с ятем, что, с целью сокращения времени обнаружения ошибок, в него введен вычислитель синдрома, при этоминформационный вход вычислителясиндрома объединен с первым информационным входом накопителя, кпервому и второму управляющим входам вычислителя синдрома подключены соответственно второй и четвертый выходы блока управления, а выход вычислителя синдрома по к первому входу блока обнар ошибок, к второму входу кот подключен выход датчика оши дополнительный выход блока жения ошибок подключен к др входу полусумматора. 2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что датчик ошибок содержит входной ключ и последовательно соединенные первый и второй триггеры, первый полу- сумматор, третий триггер, второй полусумматор и четвертый триггер, прямой выход которого подключен к информационному входу первого триггера и к вторым входам первого и второго полусумматоров, выход входного ключа подключен к управляющим входам первого, второго, третьего и четвертого триггеров, в ходы которых являются выходами дат чика ошибок.1 11620Изобретение относится к технике связи, а именно к устройствам для обнаружения и/или предотвращения ошибок в принятой, информации, а также может быть отнесено к импульс ной технике, а именно к устройствам для коррекции ошибок.Цель изобретения - сокращение времени обнаружения ошйбок.На фиг,1 представлена структурная 10 электрическая схема устройства для исправления одиночных и обнаружения многократных ошибок, на фиг.2 - вариант реализации датчика ошибок.Устройство содержит накопитель 1, .15 полусумматор 2, блок 3 обнаружения ошибок, первый и второй ключи 4 и 5, датчик 6 ошибок, блок 7 управления и вычислитель 8 синдрома, причем датчик 6 ошибок содержит входной ключ Я 20 первый, второй, третий и четвертый триггеры 10, 11, 12 и 13 и первый и второй полусумматоры 14 и 15.,в том символе, который находится в Устройство работает следующим об 25 разом,Прием комбинации осуществляется путем подачи и импульсов сдвига с второго выхода блока 7 управления на управляющий вход накопителя 1, в результате чего через 1 тактов при-З 0 нятая комбинация записана в накопитель 1, Одновременно И импульсов сдвига с второго выхода блока 7 уп- равления поступают,на первый управляющий вход вычислителя 8 синдрома, 35 на втором управляющем входе которого присутствует разрешающий сигнал с четвертого выхода блока 7 управления, а на информационный выход вычислителя 8 синдрома последовательно 40 поступают символы принимаемой комбинации. В результате через И тактов в вычислителе 8 синдрома будет записан синдром принятой комбинации. 45Если ошибки в принятой комбинации отсутствуют,то на,первом выходе блока обнаружения ошибок формируется разрешающий сигнал, который поступает на первый управляющий вход первого 50 ключа 4, а на втором выходе - запрещающий сигнал, который поступает на информационный вход второго ключа 5 и на первый вход датчика 6 ошибок, запрещающий осуществление в нем .55 сдвигов. При подаче на второй управляющий вход первого ключа 4 разрешающего сигнала с первого выхода блока 7 управления информация из накопителя 1 выдается получателю.Если в принятой комбинации обнаружены ошибки, то исправление однократной ошибки происходит за 11 тактов работы, причем на каждом такте осуществляются следующие опера. ции.С выходов датчика 6 ошибок и вычислителя 8 синдрома записанные в них п-разрядные числа (щ - число проверочных символов в используемом коде) параллельным кодом поступают на входы блока 3 обнаружения ошибок, где вычисляется их поразрядная сумма по модулю два.Если комбинации, записанные в датчике 6 ошибок и в вычислителе 8 синдрома, совпадают, то формируется единичный сигнал, который поступает на второй вход полусумматора 2. В противном случае на второй вход полусумматора 2 поступает нулевой сигнал, который не изменяет значение сигнала на его первом входе.С второго выхода блока .7 управления на управляющий вход накопителя 1 ина первый управляющий вход вычислителя 8 синдрома подается импульс сдвига. Чтобы при этом в вычислителе 8 синдрома сдвиг не происходил, на его второй управляющий вход с четвертого выхода блока 7 управления подается запрещающий сигнал. При этом в накопи- теле 1 происходит сдвиг принятой комбинации и очередной ее символ переписывается из последней ячейкинакопителя 1 в первую ячейку беэ изменения, если на втором входе полусумматора 2 нулевой сигнал, и инвертируется при переписывании в противном случае.С. третьего выхода блока 7 управления поступает на второй вход датчика 6 ошибок импульс сдвига, Если одиночная ошибка еще не исправлена, то в датчике 6 ошибок. происходит сдвиг, в результате чего в первый, второй. третий и четвертый триггеры 10,11,12 и 13 записывается синдром одиночной ошибки последней (в направлении сдвига)ячейке накопителя 1. Если же одиночная ошибка уже исправлена, тосигналом с второго выхода блока 3обнаружения ошибок, поступающим на1162053 4при обнаружении многократной ошибки обрабатываемая комбинация перезапи 1сынается в накопитель 1 через полу" сумматор 2 соответственно в сред" нем П/2 раз или 11 раз, в предлагаемом устройстве указанная перезапись осуществляется лишь один й,раз. П + 1 = Ц (П+1),зпервый вход датчика 6 ошибок, запрещаются сдвиги в кодовом фильтредатчика 6 ошибок,Перечисленные операции повторя-.ют я раз, после чего принятаякомбинация вновь занимает в накопителе 1 исходное положение, и еслионо было принято с одиночной ошибкото эта ошибка исправлена. Послеэтого с первого выхода .блока 7 уп правления поступает импульс на управляющие входы первого и второгоключей 4 и 5, результатом чего является либо выдача исправленной комби-нации через первый ключ 4 на первый цвыход устройства, если на выходе блока 3 обнаружения ошибок находитсяединичный потенциал, либо выдачасигнала "Ошибка" на второй выходустройства в противном. случаеПосле 2 Овыдачи результата обработки принятойкомбинации все блоки устройства устанавливаются в исходное состояниеВ отличие от устройства-прототипа,в котором исправление одиночной или Таким образом, для предлагаемогоустройства время обработки принятойкомбинации (в числе тактов) Т =И + 1+в + 1120+ 2,в то время как в устройстве-прототипе при исправлении одиночной ошибки в среднемТц, = П + п/2 и = и/2(И+2), а при обнаружении многократной ошиб- ки т.е, быстродействие предлагаемогоустройства выше."Пате г. Ужгород, ул, Проектная,Редактор М. Петров Тираж 872 Государственного елам изобретений осква, Ж, Рауш ектор Г, Решетник

СмотретьЗаявка

3582438, 22.04.1983

ЛЕНИНГРАДСКИЙ ИНСТИТУТ АВИАЦИОННОГО ПРИБОРОСТРОЕНИЯ

ЕВСЕЕВ ГРИГОРИЙ СЕРГЕЕВИЧ, КРУК ЕВГЕНИЙ АВРАМОВИЧ

МПК / Метки

МПК: H03M 13/39

Метки: исправления, многократных, обнаружения, одиночных, ошибок

Опубликовано: 15.06.1985

Код ссылки

<a href="https://patents.su/4-1162053-ustrojjstvo-dlya-ispravleniya-odinochnykh-i-obnaruzheniya-mnogokratnykh-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления одиночных и обнаружения многократных ошибок</a>

Предыдущий патент: Преобразователь кода во временной интервал

Следующий патент: Устройство для селективного контроля телеметрических параметров

Случайный патент: Нейтрализатор отработавших газов двигателя внутреннего сгорания