Сумматор по модулю три

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

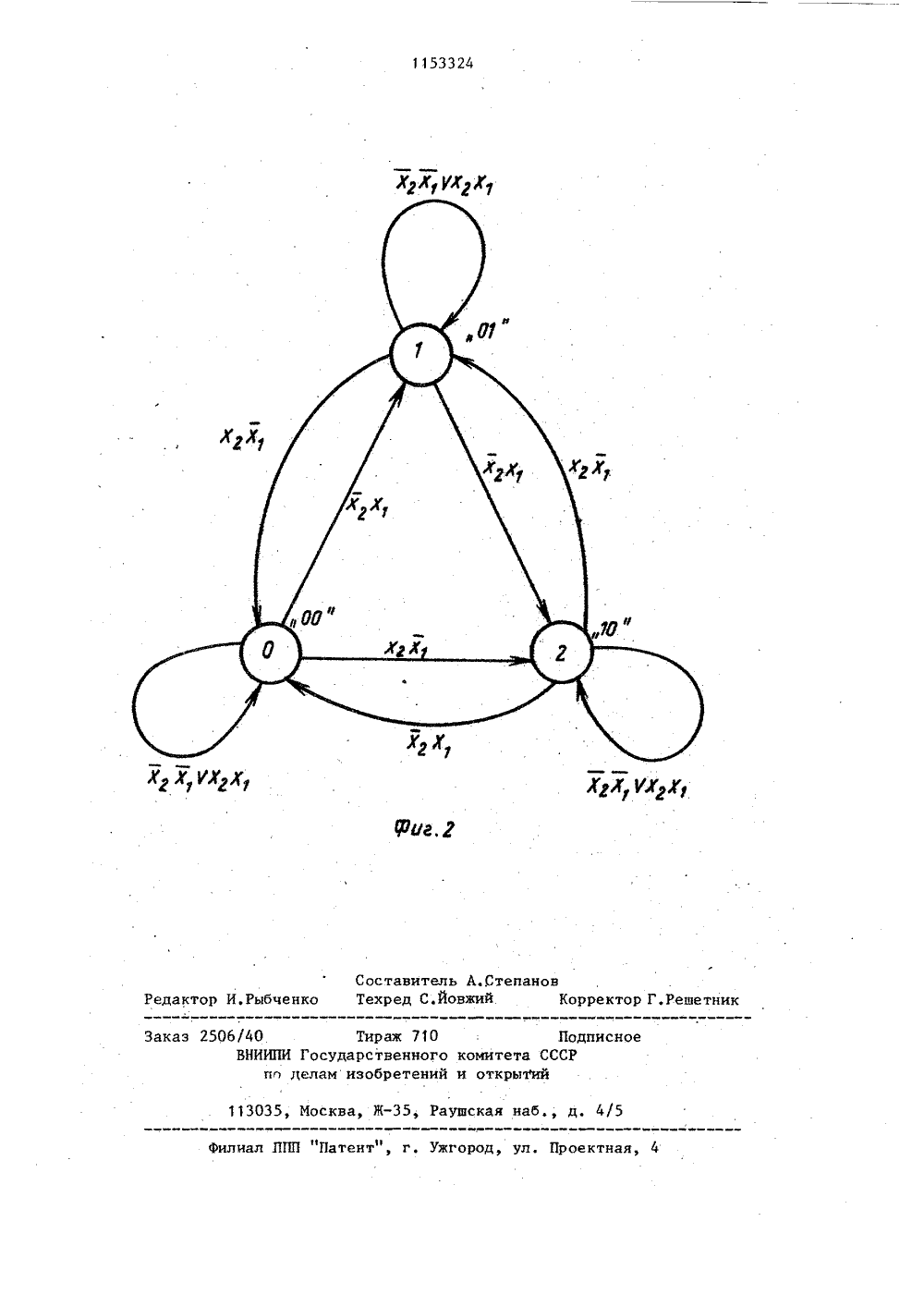

,1153324 9) ц Г Об Р 7/ ОПИСАНИЕ ИЗОБРЕТК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Я ГОсудАРстВенный номитет сссРпо делАм изоыРетжний и отнРытЮ(56) 1. Авторское свидетельство СГСРф 541175, кл. Г Об Р 11/00, 1976.2, Авторское свидетельство СССРР 890393, кл. 6 06 Р 7/72, 1980(54)(5) СУММАТОР ПО МОДУЛИ ТРИ, содержащий первый и второй триггеры,прямые выходы которых соединены с сответствующими выходами сумматора,о т л и ч а ю щ и й с я тем, что,,с целью повышения быстродействия,сумматор содержит первый, второй итретий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ,причем К-входы и тактовые входы первого и второго триггеров соединеныс выходом первого элемента ИСКЛЮЧА 10 ЩЕЕ ИЛИ, Э -входы первого и второготриггеров соединены с выходами соответственно второго и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый входпервого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом сумматораи с первым входом третьего элементаИСКЛЮЧАЮЩЕЕ ИПИ, второй вход которо- .го соединен с прямым выходом первоготриггера, второй вход первого эле-мента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом сумматора и с первым входом второго элемента ИСКЛЮЧАЮЩЕЕИЛИ, второй вход которого соединенс прямым выходом второго триггера.Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах контроля.Известен сумматор по модулю три, содержащий схемы совпадения два триггера и два элемента ИЛИ, выходами подключенные к входам триггеров, первый вход первой схемы совпадения совместно с первым входом второй схемы совпадения, а второй вход совместно с первым входом третьей схемы совпадения являются входами сумматора по модулю три, вторые входы второй и третьей схемы совпадения подключены к входу первой схемы совпадения 1.11 Недостатком такого сумматора помодулю три является низкое быстродействие,Наиболее близким по техническойсущности к предлагаемому являетсясумматор по модулю три, содержащийпервый и второй триггеры, прямыевыходы которых соединены с соответствующими выходами сумматора, первый и второй элементы ИЛИ, первый,второй, третий, четвертый, пятый,шестой, седьмой, восьмой и девятыйэлементы И, первый вход сумматорасоединен с первыми входами первогои второго элементов И, второй входсумматора соединен с первым входомтретьего элемента И и вторым входом первого элемента И, инверсныйвыход которого соединен с вторымивходами второго и третьего элементов И, выходы. первого и второго зле"ментов ИЛИ соединены соответственно со счетными входами первого ивторого триггеров прямой выход первого триггера соединен с первымивходами четвертого и пятого элементов И, выходы которых соединены соответственно с первыми входами второго и первого элементов ИЛИ, выходтретьего элемента И соединен с первыми входами шестого и седьмого элементов И и с вторым входом четвертого элемента И, выход второго элемента И соединен с первыми входамивосьмого и девятого элементов И ивторыми входами пятого элемента И,инверсный выход первого триггера соединен с вторыми входами шестого,восьмого и девятого элементов И, выход последнего соединен с вторымвходом второго элемента ИЛИ, инверсный выход второго триггера соединен с третьими входами четвертого,и пятого элементов И и вторым входомседьмого элемента И, выход которогосоединен с вторым входом первого элемента ИЛИ, прямой выход второго триггера соединен с третьими входамишестого элемента И и восьмого эле Омента И, выход которого соединен стретьим входом элемента И, выходшестого элемента И соединен с третьим входом второго элемента ИЛИ 2 3.Недостатком известного сумматорапо модулю три также является низкое 15быс тродейс твиеБыстродействие известного сумматора определяется временим последовательного срабатывания элементовсамой длинной цепочки, состоящей из 20первого, третьего, шестого элементов И, второго элемента ИЛИ, второготриггера, пятого элемента И, первого элемента ИЛИ и первого триггера, и равно Т=бТ +2 Т , где Т - время срабатывания одного логическогоэлемента; Т- время переключениятриггера из одного состояния в другое.Целью изобретения является повы- ЗО щенное быстродействие сумматора помодулю три.Поставленная цель достигаетсятем, что сумматор по модулю три, содержащий первый и второй триггеры, 35 прямые выходы которых соединены ссоответствующими выходами сумматора,содержит первый, второй и третийэлементы ИСКЛЮЧАЮЩЕЕ ИЛИ, причем Квходы и тактовые входы первого и вто "О рого триггеров соединены с выходомпервого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,3-входы первого и второго триггеровсоединены с выходами соответственновторого и третьего элементов ИСКЛ 2- 45 ЧАЮЩЕЕ ИЛИ, первый вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом сумматора и с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕИЛИ, второй вход которого соединен с 50 прямым выходом первого триггера,второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторью.входомсумматора и с первым входом второгоэлемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй55 вход которого соединен с прямым выходом второго триггера.На джг,1 приведена структурная схема предлагаемого сумматора по1153324 3модулю три, на Фиг,2 - граФ переходов сумматора по модулю триСумматор по модулю три содержитпервый 1,и второй 2 триггеры, элементы ИСКЛЮЧАЭ)ЩЕЕ ИЛИ 3-5, первый6 и второй 7 входы, первый 8 и второй 9 выходы.Работа сумматора по модулю трииллюстрируется грабом переходов,приведенным на Фиг.2. На графе номера вершин 0,1,2 соответствует значениям суммы по модулю три. Дугамипоказаны направления переходов припоступлении на входы сумматора помодулю три входной комбинации Х Х ,которая может принимать значения"ОО" "01" "10" "11" (Х - старЭ й Э гший с весом 2, а Х, - младщий с весом 1 разряды комбинации), Сумма помодулю три кодируется состояниямивторого и первого триггеров следующим образом: 0-"00", 1-"01", 2"10", Состояния триггеров обозначены соответственно символами аа(а - старший с весом 2, а - младший с весом 1 разряды суммы),В каждом такте работы триггерынаходятся в определенном текущемсостоянии аа , соответствующемсумме по модулю три всех поступивших ранее входных комбинаций ХХ.Затем на первый 6 и, второй 7 входыпоступают срответственно значениястаршего Х и младшего Х разрядов входной комбинации ХХ,. Поддействием этих сигналов триггеры переходят в очередное состояние, которое определяет сумму по модулю тривсех входных комбинаций, в том числе и поступивших в данном такте. 4Из графа переходов вилно, чтопри поступлении на входы комбинацииХХ 1, значения разрядов в которойсовпадают ("00 ф или "11") сумма помодулю грн не изменяется и триггерыне изменяют своих состоянВ, В этомслучае тактовый сигнал на С-входахобоих триггеров равен нулю. В остальных случаях тактовый сигнал на С-вхо О дах триггеров равен 1 и триггеры могут изменять свои состояния при поступлении входных комбинаций.Для устойчивой работы сумматорапо модулю три необходимо, чтобы длиц тельность сигналов входных комбинаций не превышала суммы времен срабатывания одного триггера и одногоэлемента ИСКЛЮЧАЮЩЕЕ ИЛИ.Условимся считать, что время задержки сигнала в одном элементе Ии одном элементе ИЛИ примерноодинаково и равно Т , а время срабатывания триггера равно 2 Т . Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ реализует функ цию К=ХХчХХ, и может быть реализован на двух элементах И и одномэлементе ИЛИ, При этом время задержки сигнала в элементе ИСКЛЮЧАЮЩЕЕИЛИ равно 2 Т , Быстродействие даннога сумматора по модулю три определяется временем задержки сигнала водном элементе ИСКЛЮЧАКЩЕЕ ИЛИ и временем срабатывания триггера и равноТ=2 Тэ+2 Т=4 Тэ. Как определено ранее, время срабатывания известногосумматора по модулю три равно Т==6 Тд +2 Ттг 10 Т. Тогда быстродействие предлагаемого сумматора по модулю три по сравнению с прототипомувеличивается в 2,5 раза.1153324 Составитель А.Степано Техред С.йовжий Редактор И,Рцбченко Коррек орректешетн аказ 250 бДО Тираж 710 Подпис ВНИИПИ ГосУдарственного комитета СССР п делам изобретений и открытийкая наб., д. 4/113035, Москва, Ж, Раушфилиал ЛПП "Патент", г. Ужгород, ул. Проектная,

СмотретьЗаявка

3659088, 03.11.1983

ВОЕННАЯ ИНЖЕНЕРНАЯ РАДИОТЕХНИЧЕСКАЯ ОРДЕНА ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ И ОРДЕНА ОТЕЧЕСТВЕННОЙ ВОЙНЫ АКАДЕМИЯ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА ГОВОРОВА Л. А

РЯБУХА НИКОЛАЙ ДЕМИДОВИЧ, КОМИСАРУК ВИКТОР СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 7/49

Опубликовано: 30.04.1985

Код ссылки

<a href="https://patents.su/4-1153324-summator-po-modulyu-tri.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор по модулю три</a>

Предыдущий патент: Преобразователь двоичного кода в двоично-десятичный код

Следующий патент: Устройство для умножения

Случайный патент: Двигатель с катящимся ротором