Устройство для вычисления функции =

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1034033

Автор: Мельник

Текст

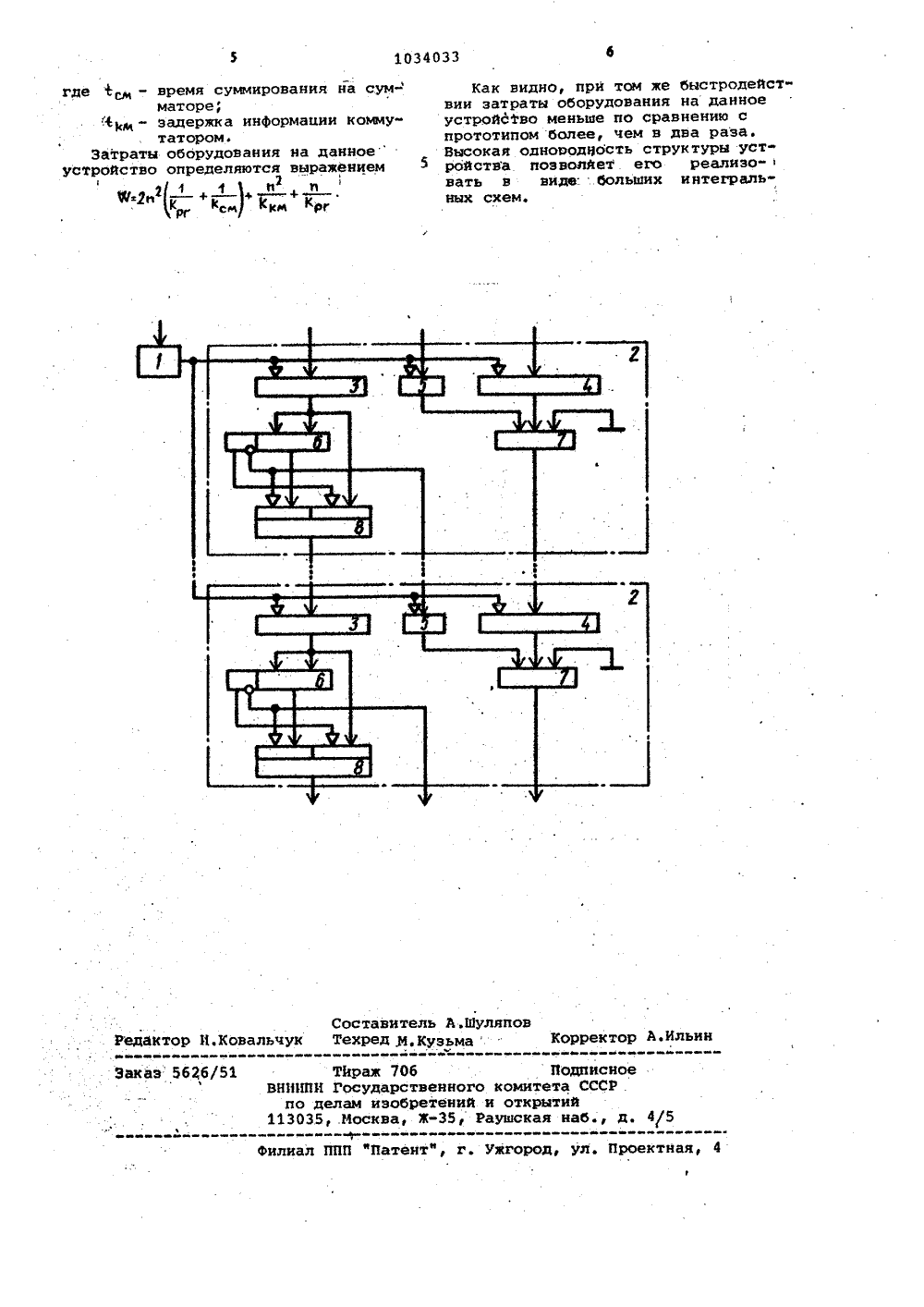

ОЮ (И) СОЮЗ ООВЕТСНИХСОЦИАЛИСТИЧЕСКИХЩОПИЬЛИй ЩВ Ь 06 1 7 556 ПО ДЮ)АМ ИЗ 09%ТЕНИИ И ОТНЯТИЙОПИСАНИЕ ИЗОБРЕТЕНИЯ(56) 1. Авторское свидетельство СССРМ 590733, кл. С 06 Г 7/38, 1978.2. Авторское свидетельство СССРпо заявке Р 3255903,кл. Ф 06 Р 7/556, 1981 -прототип(54) (57) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ а=Оп Х, содержащее .генератор тактовых импульсов и и бло" ков вычисления итерации, каждый нэкоторых состоит из первого и второго регистров, первого и второго сумматоров, коммутатора и триггера, причем выходы первого и второго регистров соединены соответственно с первыми входами первого и второго сумматоров, выход первого регистра подключен к первому информационному входу, коммутатора, выход второго .сумматора ,:1-го блока вычисления итерации (где 1 = 1 Фп)соединен с информационным входом второго регистра (1+1)-го блока вычисления итерации, выход генератора тактовых импульсов подключен к управляющим входам всех регистров блоков вычисления итерации, о т л и ч а ю/ щ е е с я тем, что, с целью сокращения объема оборудования,. в каждом 1-м блоке вычисления итерации выход первого регистра соединен с вторым входом первого сумматора со сдвигом на ) разрядов вправо (где =0,1 ,п -1), выход дробной части операнда первого сумматора под-. кпючен к второму информационному входу коммутатора, первый и второй управляющие входы которого соединены соответственно с прямком и инверсным выходами разряда целой части операнда первого сумматора,. выход триггера подключен к второму входу сумматора, третий вход которого соединен с входом. константы, инверс, ный выход разряда целой части опе-. ранда первого сумматора и выход коммутатора -го блока вычисления итерации подключены соответственно к информационным входам триггера и первого регистра (1 +Ц -го блока вычисления итерации, выход генера.тора тактовых импульсов соединен с управляющими входами триггеров блоков вычисления итерации, вход и. выход устройства подключены соответственно к информационным входам первого регистра и второго сумматора первого и п -го блоков вычисления итерации+1= 1 О,Есяи ъ;+1,регистры, триггер 5, первый б, второй 7 сумматоры, коммутатор 8.Вычисление Функции =9 пх в устройстве производится на основе .метода цифра за цифрой" со знакопостоянными приращениями, который описывается следующими итерационными Формулами: 4ции выполняется вторая итерациянад первым операндом, и на выходекоммутатора 8 появляется значениеХ 2, а на. выходе сумматора 7 - значение К . Сдвиг значения Х,1 на саинразряд вправо осуществляется путемсоединения выхода регистра 3 с одним из входов сумматора б со сдви- гом на разряд т.е. выход -горазряда регистра соединяется с вхо 0 дом (+1) -го разряда сумматора3=1, 2,я, )., Константа Рд 1+2 ")фиксируется на входе сумматоре 7путем подачи в те разряды суваиатора,где разряд константы имеет значение 15 единицы сигнала с выхода триггера5, а в те разряды, где разряд константы равен нулю - нулей, путем ихзаземления. тогда, если =1, навыходе сумматора 7 сформируется значение данной константы, а если1 = О, то на выходе сумматора 7будет нуль.В третьем такте результаты вычислений, полученные.во втором блоке 2, записываются а третий блок,а результаты. первого во второй,.Врегистр 3 первого блока 2 вычисления итерации поступает третий операнд, В каждом блоке выполняетсясоответствующая итерация над поступившим в него операндом, причем втретьем блоке 2 вычисления итерациипромежуточный результат иэ регистра3 поступает на один иэ входов сумматора 8 со сдвигом на два разряда 35 вправо, а на сумьиторе 7 производится сложение содержимого регистра 4с константой 6 п 1+2 2, если значе-.ние триггера 5 равно 1, или с нулем,если значение триггера 5 равно нулю.40 В дальнейшем результаты предыдущих блоков поступают в. последующиеблоки, а в регистр 3 первого блокапоступает новый операнд и т.д., причем в каждом последующем блоке промежуточные результаты из регистра 3поступают на один из входов сумматора б. со сдвигом на один разряд.вправо большим, чем в предыдущем блоке, а в выражениях логарифмов, Фор мируемых монтажным способом на входах суьаааторов 7, степень двойкивозрастает на единицу.В и -м такте на выходе сумматора7 последнего блока 2 вычисления итерации получается первый результат;а в дальнейшем в каждом такте на:выходе будет появляться новый результат.Предлагаемое устройство работает. но конвейерному принципу. Его быст-: 60 родействие определяется длительностью одного такта, доторая равназадержке в одной ступени устройстван определяется выражением1 ОЗ 4 ОЗЗ Сост витель А.Шул д Ю.КузьмаЮ706 арственного зобретений и ва, Ж, Ра ов Корректор А.Иль РЕдаКтор И.КовальчуквйвЗаказ 5636/51 Подписноемитета СССР .крытийкая наб., д. 4,/5 ТйражВНИИПИ Госудпо делам и113035,.Иоск илиал ППП фПатентф, г. Ужгород, ул. Проектная, 4 где 1 с, - время суммирования на сум-маторе,д, - задержка информации коммутатором.Затраты оборудования на данноеустройство определяются выражением2 1,1 п 2Э 2 ь + + +"см "км "рг Как видно, при том же быстродействии затраты оборудования на данное устройство меньше по сравнению с прототипом более, чем в два раза. Высокая однородность структуры устройства позволяет его реализо"вать в виде больших интегральных схем.

СмотретьЗаявка

3412768, 29.03.1982

ПРЕДПРИЯТИЕ ПЯ В-8751

МЕЛЬНИК АНАТОЛИЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 7/556

Метки: вычисления, функции

Опубликовано: 07.08.1983

Код ссылки

<a href="https://patents.su/4-1034033-ustrojjstvo-dlya-vychisleniya-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции =</a>

Предыдущий патент: Матричное вычислительное устройство

Следующий патент: Датчик случайных равновероятных временных интервалов

Случайный патент: Устройство для измерения виброскорости вращающихся деталей