Запоминающее устройство с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

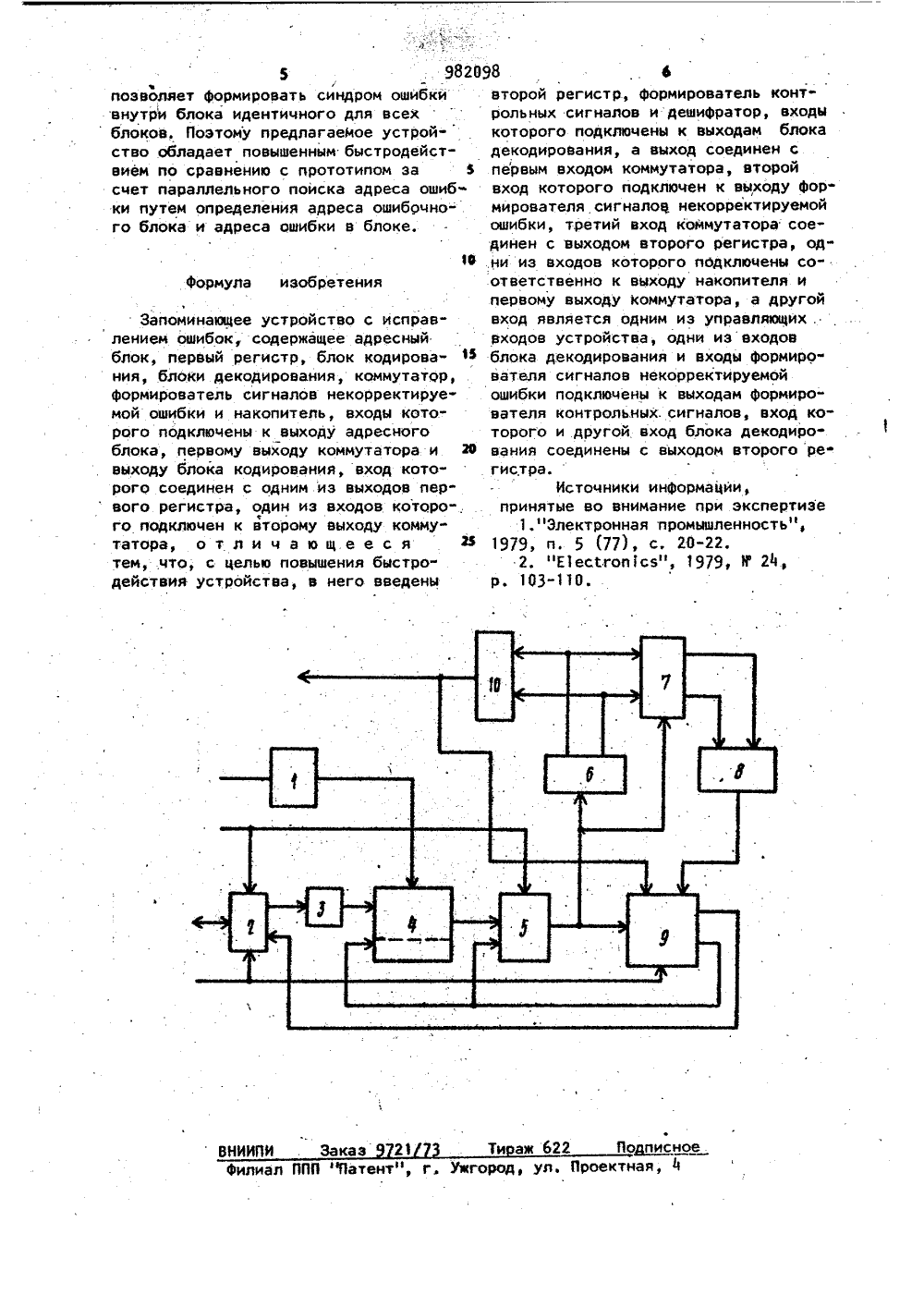

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ 0 юсйМю сиДлсвУ(51)М. Кл. С 11 С 29/ОО с присоединением заявки,%(23)Приоритет Вв 3 щараваай аеитет СССР в аве взебреваВ в ОтМР 3 пиз(ЗУ) с исправлением ошибок, котороесодержит основной накопитель, дополнительный накопитель, необходимыйдля хранения контрольных соотношений,кодирующие и декодирующие устройства,функционйруецие соответственно призаписи и при считывании 11,Однако в этом ЗУ с ростом размераинформационного слова ухудшается быстродействие, Это определяется необходимостью увеличения числа йеременных,используемых для формирования проверочных соотношений, которые, как правило, реализуются на сумматорах помодулю два, быстродействие которыхзависит от числа входов, т.е. числаинформационных разрядов и структурыкода. Например, при использовании кодов Хемминга для исправления одиночных и обнаружения двойных ошибок чис 2ло входов сумматоров по модулю два кодирующего и декодирующего устройств увеличивается с трех (для инФормацион. наго слова размером четыре бита) до восемнадцати (для слова размером тридцать два бита). Известно, что данный класс кодов с этой точки зрения является оптимальным, а другие классы обладают более худшими характеристиками. Таким образом, недостаткои этого ЭУ является сложность обеспечения быстрого кодирования и декодирования двоичной информации на многоуровневых сумматорах по модулю два, т.е. существенное снижение быстродействия,Наиболее близким техническим решением к изобретению является запоиинаю" щее устройство с исправлением ошибок, содержащее накопитель, адресный блок, блоки кодирования и декодирования, коммутатор, формирователи сигналов. Принцип работы этого устройства основан на поразрядном сравнении контроль 3 98209 ных соотношений, формировании синдрома ошибки, определении адреса ошибки и инвертировании информационного содержания ячейки, определяемой данным. адресом. Формирование контрольных соотношений осуществляется с помощью многоуровневого сумматора по модулю два. В режиме считывания упомянутые многоуровневые сумматоры с последовательно подсоединенным блоком двухвхо довых сумматоров по модулю два исполь" зуются для формирования синдрома ошибки 2.Недостатком данного устройства является невысокое быстродействие, опре 15 деляемое задержками прохождения двоичного сигнала в многоуровневых логических схемах кодирующего и декодирующего устройств.Цель изобретения - повышение быст О родействия устройства.Поставленная цель достигается тем, что в запоминающее устройство с исправлением ошибок, содержащее адресный блок, первый регистр, блок коди рования,коммутатор, Формирователь сигналов некорректируемой ошибки и накопитель, входы которого подключе ны к выходу адресного блока, первому выходу коммутатора и выходу блока ко- ЗО дирования, вход которого соединен с одним из выходов первого регистра, один из входов которого подключен к второму выходу коммутатора, введены второй. регистр; Формирователь контрольных сигналов и дешифратор, входы которого подключены к выходам блока декодирования, а выход соединен с первым входом коммутатора, второй вход которого подключен к выходу Формирователя сигналов некорректируемой ошибки третий вход коммутатора соединен с выходом второго регистра, одни из входов которого подключены соответственно к выходу накопителя и45 первому выходу коммутатора, а другой вход является одним из управляющих входов устройства, одни из входов блока декодирования и входы Формирователя сигналов некорректируемой ошибки подключены к выходам формирователя50 контрольных сигналов, вход которого и другой вход блока декодирования соединены с выходом второго регистра.На чертеже изображена Функциональная схема запомйнающего устройства с исправлением ошибок.Устройство содержит адресный блок 11 первый регистр 2, служащий для 8 4хранения входной информации, блок 3кодирования, накопитель 4, второй регистр 5, служащий для коррекции инФормации, формирователь б контрольныхсигналов, выполненный в виде двухуров.невого генератора синдрома ошибки,блок 7 декодирования, дешиФратор 8,служащий для определейия адреса ошибки и выполненный в аиде двухуровневого блока, коммутатор 9 и Формирователь 10 сигналов некорректируемойошибки.Запись информации в ЗУ происходитследующим образом,Информационное слово заносится врегистр 2 Преобразованное слово изблока 3 записывается в накопитель 4по адресу, определяемому. блоком .На этом цикл записи заканчивается,В режиме считывания информации кодовое слово из накопителя 1 заносится в регистр 5, в котором происходитисправлением однократных ошибок, возникающих в ЗУ в процессе записи илихранения. В блоках 6 и 7 происходитформирование синдрома ошибки, адрескоторой определяется дешифратором 8.формирование синдрома происходит путем разбиения информационного слована блоки с последующим параллельнымопределением адреса ошибочного блокаи адреса ошибочного разряда в блоке,Передача кода адреса ошибки на ре"гистр 5 осуществляется через коммутатор 9. Данный коммутатор используется также для передачи исправленныхвыходных данных в регистр 2. Управле.ние передачей данных через коммутатор 9 осуществляется Формирователем10 при наличии внешнего. управляющегосигнала (не доказан),Преобразованием информационногослова в блоках 6 и 7 производися всоответствии с модифицированным кодом Хемминга, представленным в матричной Форме в таблице для информа"ционного слова размером 6 бит,О 00 О 1 0100 О 1 10000,0ООО О 1 0 ОО а ОООО ООООО 1 ОООО ОООО О1111 0000 0000 1111 00001 0 111 1111 . 111 111 11111 1Структура кода, реализуемого в предлагаемом устройстве, такова, что%9820Ъпозволяет формировать синдром ошибки внутри блока идентичного для всех блоков. Поэтому предлагаемое устрой-ство .обладает повышенным быстродействием по сравнению с прототипом за 5 счет параллельного поиска адреса ошибки путем определения адреса ошибочного блока и адреса ошибки в блоке,формула изобретения Запоминающее устройство с исправлением ошибок, содержащее адресный блок, первый регистр, блок кодирова ния, блоки декодирования, коммутатор, формирователь сигналов некорректируемой ошибки и накопитель, входы кото" рого подключены к выходу адресного блока, первому выходу коммутатора и Зв выходу блока кодирования, вход которого соединен с одним из выходов первого регистра, один из входов которо" го подключен к второму выходу коммутатора, о т л и ч а ю щ е е с я И тем, .что, с целью повышения быстродействия устройства, в него введены 98 авторой регистр, формирователь контрольных сигналов и-дешифратор, входыкоторого подключены к выходам блокадекодирования, а выход соединен спервым входом коммутатора, второйвход которого подключен к выходу формирователя сигналов некорректируемойошибки, третий вход коммутатора соединен с выходом второго регистра, од".ни из входов которого подключены соответственно к выходу накопителя ипервому выходу коммутатора, а другойвход является одним из управляющих .входов устройства, одни из входовблока декодирования и входы формиро"вателя сигналов некорректируемойошибки подключены к выходам формирователя контрольных. сигналов, вход которого и другой вход блока декодирования соединены с выходом второго ре. гистра.Источники информации,принятые во внимание при экспертизе1,"Электронная промышленность",1979, и, 5 (77), с, 20-22.2, "Е 1 есйгопсз", 1979 у 0 2"юр, 103-110.

СмотретьЗаявка

3251780, 25.02.1981

ПРЕДПРИЯТИЕ ПЯ Г-4515

БОРИСОВ ВИКТОР СТЕПАНОВИЧ, КУЗНЕЦОВ АЛЕКСАНДР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, ошибок

Опубликовано: 15.12.1982

Код ссылки

<a href="https://patents.su/3-982098-zapominayushhee-ustrojjstvo-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением ошибок</a>

Предыдущий патент: Устройство для контроля постоянных блоков памяти

Следующий патент: Запоминающее устройство с контролем цепей коррекции ошибок

Случайный патент: Подовый кирпич