Устройство для суммирования чисел, представленных в системе счисления в остаточных классах

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 883903

Авторы: Гварамия, Себуа, Хацкевич, Чачанашвили

Текст

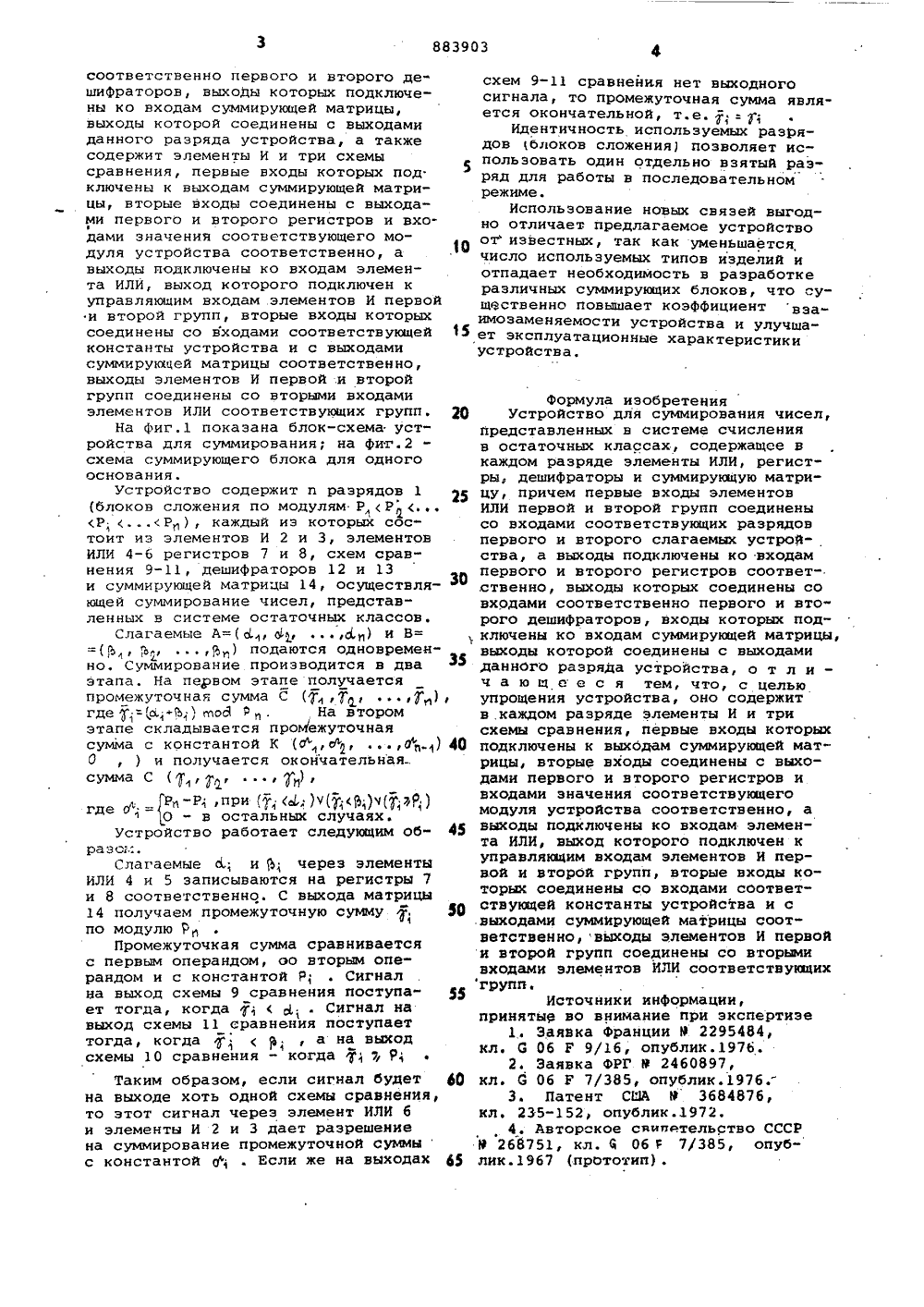

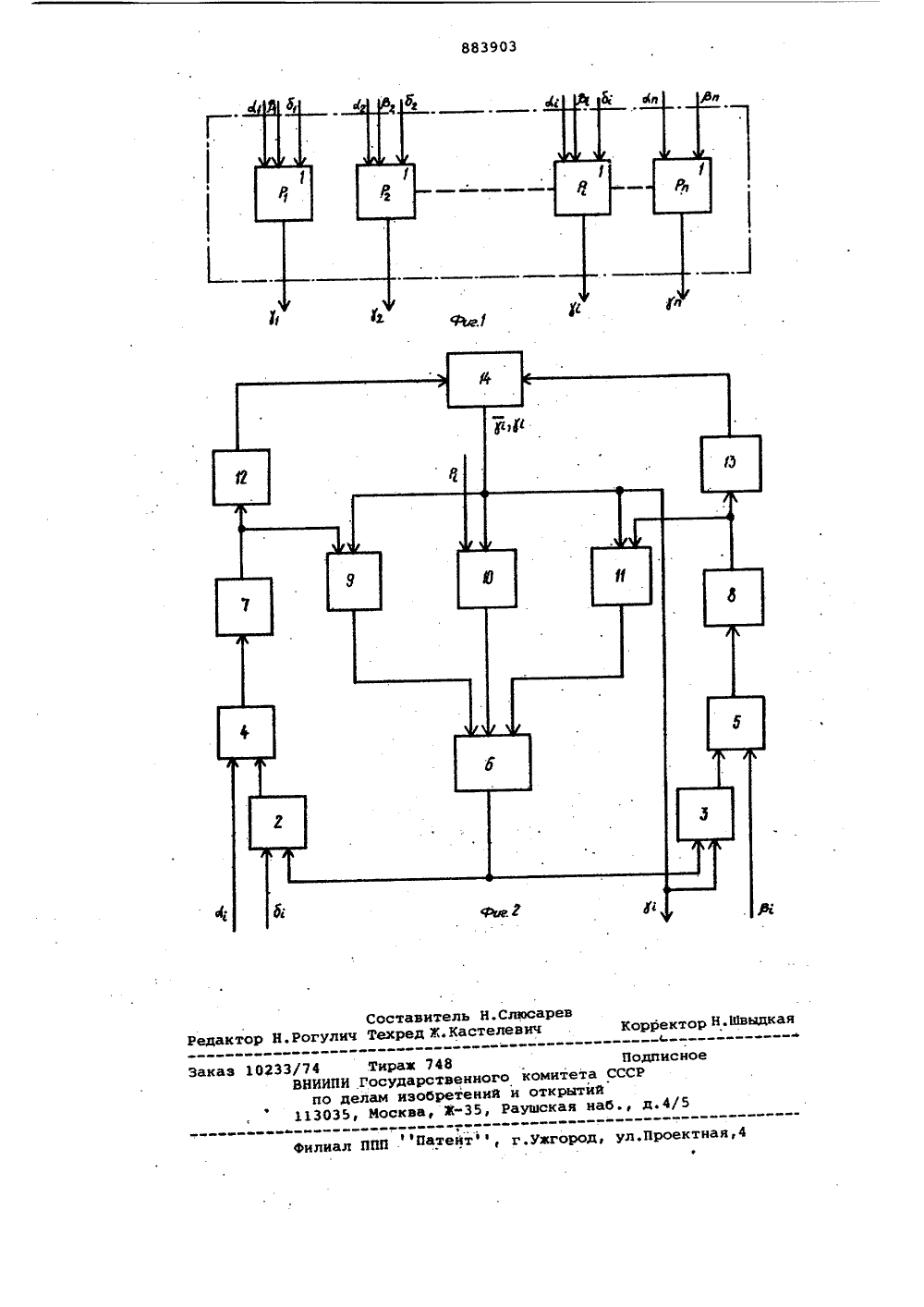

Сфюз Советских Социалистических РеслубеаОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ 883903(51) М. Кл. с присоединением заявки Мт -6 Об Р 7/72 Гасуяарстаениый коиктет СССР 60 Асааи изОбрфтйияя и открытий(54) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ ЧИСЕЛ, ПРЕДСТАВЛЕННЫХ В СИСТЕМЕ СЧИСЛЕНИЯ В ОСТАТОЧНЫХ КЛАССАХ Изобретение относится к вычислительной технике и может бытьиспользовано в вычислительных устройствах,; работающих в системе остаточных классов (СОК) .Известно суммирующее устройство для чисел, представленных в системе счисления в остаточных классах,.содержащее сумкатор, блок переноса и блоки коррекции (1).Известны также суммирукхаие уст-, ройства, содержащие сумматор, блок передачи, блок коррекции, инвертор и суммирующее устройство, содержащее регистры, сумматоры, блок управления и,избирательный блок (23 и 13.Недостатком этих устройств. явля-. ется усложненность схем, что отрицательно влияет на взаимозаменяемость, технологичность и удобство эксплуатации. Наиболее близким к предлагаемому по технической сущности является устройство для .суммирования чисел, 25 представленных в системе счисления в . остаточных классах, каждый из п разрядов которого (и - число оснований СОК) содержит анализатор, блок схемы совпадения, комбинационную логическую 36 схему и многоразрядный комбинационный двоичный сумматор, выход которого . подключен к комбинационной логической схеме и к выходу устройства через блок схем совпадения, другой выход комбинационного сумматора подключен ко входу анализатора, выход которого подключен к первому входу блока схем совпадения, выход комбинационной логической схемы соединен со вто-. рьи входом блока схем совпадения (4.Недостатком известного устройства также является его сложность.Цель изобретения - упрощение устройства.Поставленная цель достигается тем, что вместо и (по числу оснований СОК) различных по конструкции разрядов (блоков сложения) используется и одинаковых разрядов (блоков сложения), каждый из которых содержит элементы ИЛИ, регистры, дешифра.торы и суммирующую матрицу, причем Первые входы элементов ИЛИ первой, и второй групп соединены со входами соответствующих разрядов первого и второго слагаемых устройства, а выходы подключены ко входам первого и второго регистров соответственно, выходы которых соединены со входамисхем 9-11 сравнения нет выходногосигнала, то промежуточная сумма является окончательной, т.е., : р1Идентичность используемых разрядов (блоков сложения) позволяет использовать один отдельно взятый разряд для работы в последовательномрежиме.Использонание новых снязей выгодно отличает предлагаемое устройство о от известных, так как уменьшается,число используемых типов изделий иотпадает необходимость в разработкеразличных суммирующих блоков, что сущЕственно повышает коэффициент 15имозаменяемости устройства и улучшает эксплуатационные характеристикиустройства. 25 30 соответственно первого и второго дешифраторов, выходы которых подключены ко входам суммирующей матрицы,выходы которой соединены с выходамиданного разряда устройства, а такжесодержит элементы И и три схемысравнения, первые нходы которых подключены к выходам суммирующей матрицы, вторые входы соединены с выходами первого и второго регистров и входами значения соответствующего модуля устройства соответственно, авыходы подключены ко входам элемента ИЛИ, выход которого подключен куправляющим входам элементов И первойи второй групп, вторые входы которыхсоединены со входами соответствующейконстанты устройства и с выходамисуммирующей матрицы соответственно,выходы элементов И первой и второйгрупп соединены со вторыми входамиэлементов ИЛИ соответствующих групп.На фиг.1 показана блок-схема уст"ройства для суммирования; на фиг.2схема суммирующего блока для одногооснования,Устройство содержит п разрядов 1(блоков сложения по модулям Р РРР), каждый из которых состоит из элементов И 2 и 3, элементовИЛИ 4-6 регистров 7 и 8, схем сравнения 9-11, дешифраторов 12 и 13и суммирующей матрицы 14, осуществляющей суммирование чисел, представленных в системе остаточных классов.Слагаемые А=(с(, 01 . .Ы,и) и В==(Ъ, ( ,) подаются одновремен"но. Суммиронанйе производится в дваэтапа. На первом этапе получаетсяпромежуточная сумма С (7 7 "7)где ф=а, Ъ) од Р. На второмэтапе складывается промежуточнаясумма с константой К (О,Ф, ,О" )0 , ) и получается окончательнаясумма С (, у5)(Р-Р,при , (е(,; )Ч(Ц)ч 3)о - в остальных случаях.Устройство работает следующим об"разора"Слагаемые 1; и ( через элементыИЛИ 4 и 5 записываются на регистры 7и 8 соответственно. С выхода матрицы14 получаем промежуточную сумму у,по модулю РПромежуточкая сумма сравниваетсяс первым операндом, оо вторым операндом и с константой Р; . Сигнална выход схемы 9 сравнения поступает тогда, когда 471, Сигнал навыход схемы 11 сравнения поступаеттогда, когда "р. , а на выходсхемы 10 сравнения - когда ф 7, Р,Таким образом, если сигнал будетна выходе хоть одной схемы сравнения,то этот сигнал через элемент ИЛИ 6и элементы И 2 и 3 дает разрешениена суммирование промежуточной суммыс константой о"; . Если же на выходах 35 Р 40 45 50 55 40 45 формула изобретенияУстройство для суммирования чисел, представленных в системе счисления в остаточных классах, содержащее в каждом разряде элементы ИЛИ, регистры, дешифраторы и суммирующую матрицу, причем первые входы элементов ИЛИ первой и второй групп соединены со нходами соответствующих разрядон первого и второго слагаемых устройства, а выкоды подключены ко входам первого и второго регистров соответ" стненно, выходы которых соединены со входами соответственно первого и вто" рого дешифраторон, входы которых подключены ко входам суммирующей матрицы,выходы которой соединены с выходамиданного разряда устройства, о т л и -ч а ю щ ее с я тем, что, с цельюупрощения устройства, оно содержитв .каждом разряде элементы И и трисхемы сравнения, первые входы которыкподключены к выхбдам суммирующей матрицы, вторыр нходы соединены с выходами первого и второго регистров ивходами значения соответствующегомодуля устройства соответственно, авыходы подключены ко входам элемента ИЛИ, выход которого подключен куправляющим входам элементов И первой и второй групп, вторые входы которых соединены со входами соответствующей константы устройства и свыходами суммирующей матрицы соответственно, выходы элементов И первойи второй групп соединены со вторымивходами элементов ИЛИ соответствующихгрупп.Источники информации,принятые во внимание при экспертизе1. Заявка франции 9 2295484,кл. О 06 Р 9/16, опублик. 1976.2. Заявка ФРГ 9 2460897,кл. О 06 Р 7/385, опублик,1976.- 3. Патент С(й 9 3684876,кл. 235-152, опублик.1972.4. Авторское сяипетельство СССРМ 268751, кл. Я 06 Р 7/385, опуб"лик.1967 (прототип) .883903 сное каз 10233/74 Тираж 748 По ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., филиал ППП Патейтф, г.ужгород, ул,Проектна Составитель Н.Слюсарев актор Н.Рогулич Техред Ж.Кастелевич Корректор Н. Швыдкая и

СмотретьЗаявка

2759219, 03.04.1979

Заявитель

ЧАЧАНАШВИЛИ АМИРАН РАФАЭЛОВИЧ, ХАЦКЕВИЧ ВИЛЬЯМ ХАРИТОНОВИЧ, ГВАРАМИЯ АНЗОР АЛЕКСАНДРОВИЧ, СЕБУА ДЖАМБАКУР МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 7/72

Метки: классах, остаточных, представленных, системе, суммирования, счисления, чисел

Опубликовано: 23.11.1981

Код ссылки

<a href="https://patents.su/3-883903-ustrojjstvo-dlya-summirovaniya-chisel-predstavlennykh-v-sisteme-schisleniya-v-ostatochnykh-klassakh.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования чисел, представленных в системе счисления в остаточных классах</a>

Предыдущий патент: Устройство для деления частотно-импульсных сигналов

Следующий патент: Устройство управления последовательностью команд

Случайный патент: Измеритель параметров волноводных у-циркуляторов