Устройство для логической обработки и вычитания двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 855655

Авторы: Аспидов, Козюминский, Мищенко, Семашко

Текст

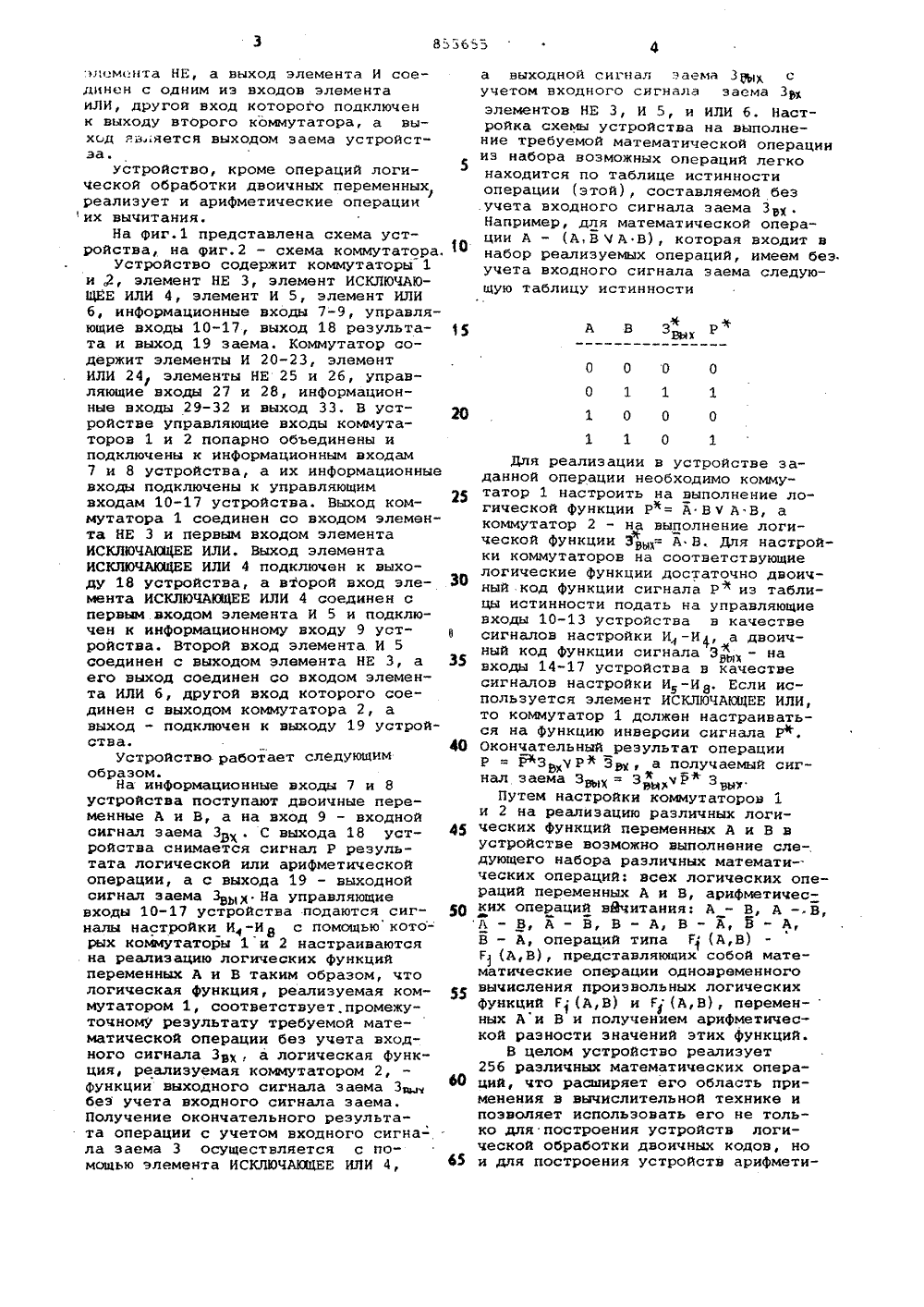

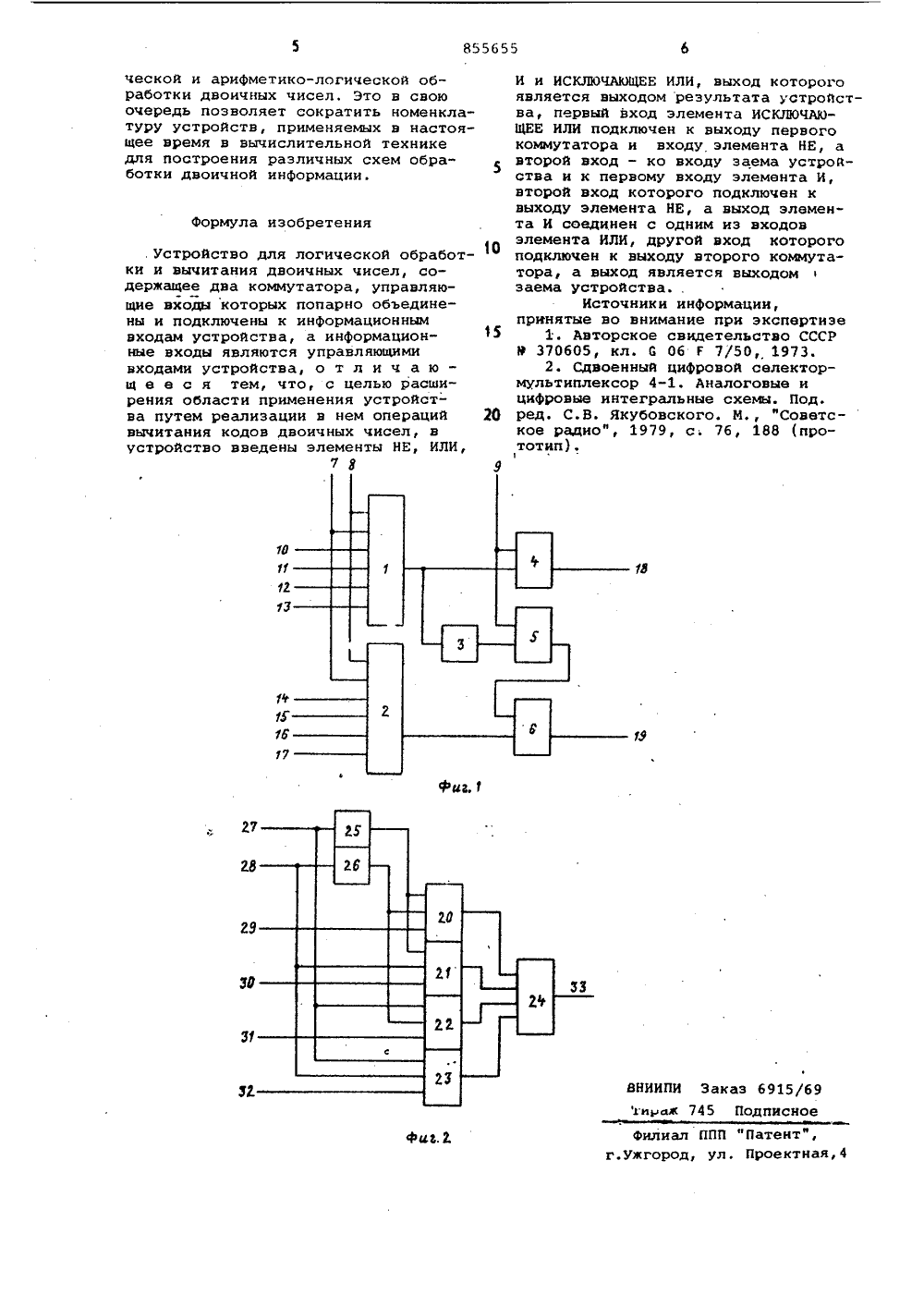

ОПИСАНИЕ ИЗОБРЕТЕНИЯ Союз Советских Социалистических Республик(22) Заявлено 061279 (21) 2847381/18-24 (5) М Кл с присоединением заявки Мо(23) Приоритет С 06 Г 7/38 Государственный комитет СССР ио делам изобретений и открытий(5 РОЙСТВО ДЛЯ ЛОГИЧЕСКОЙ ОБРАБОТКИИ ВЫЧИТАНИЯ ДВОИЧНЫХ ЧИСЕЛ огические Р 1. данногото оно не операцийания А-Вбласть пр операции тем 15 выход вый в подклю тора вход перво вход Изобретение оносится к вычислительной технике и может использоваться при конструировании устройств обработки цифровой информации.5Известно устройство для вычитания двоичных чисел, содержащее два сумматора, элемент задержки, ключ, элементы И, ИЛИ, информационные входы, вход заема, выход результата и выход заема 1.Недостатком данного устройства является то, что оно выполняет только одну арифметическую операцию - вычитание. Реализация только одной Операции ограничивает область Применения устройства.Наиболее близким к предлагаемому является устройство, содержащее два коммутатора, выходы которых являют ся выходами устройства, управляющие входы коммутаторов попарно объединены и подключены ко входам устройства, инФормационные входы ком- мутаторов являются входами устройст ва. устройство при подаче на его управляющие входы двоичных сигналов А и В, а. на его информационные входы сигналов 0 и 1, образующих соответствующие коды настройки, реа О лизует любые л переменных А и Внедостатком устройства является то, ч реализует аРиФметических например операции вычит или В-А, что ограничивает о именения устройства.Цель изобретения - расширение области применения устройства пу реализации в нем операций вычитания кодов двоичных чисел.Поставленнаяцель достигается тем, что в устройство для логической обработки и вычитания двоичных чисел, содержащее два коммутатора, управляющие входы кбторых попарно объединены и подключены к информационным входам устройства, а информационные входы являются управляющими входами устройства, в устройство введены элементы нБ, ИЛЙ, И н ИСюЛВЧАЮЩЕЕ ИЛИ, выход которого являетсяом результата устройства, перход элемента ИСКЛЮЧАЮЩЕЕ ИЛИчен к выходу первого коммутаи входу элемента НЕ, а второйко входу заема устройства и кму входу элемента И, второйкоторого подключен к выходуюсмента НЕ, а выход элемента И соединен с одним из входов элемента иЛИ, другой вход которого подключен к выходу второго коммутатора, а выход яв"яется выходом заема устройстэа.устройство, кроме операций логической обработки двоичных переменных реализует и арифметические операции их вычитания.На фиг.1 представлена схема устройства, на фиг.2 - схема коммутатора. 10Устройство содержит коммутаторы 1 и 2, элемент НЕ 3, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, элемент И 5, элемент ИЛИ 6, информационные входы 7-9, управляющие входы 10-17, выход 18 результа та и выход 19 заема, Коммутатор содержит элементы И 20-23, элемент ИЛИ 24 элементы НЕ 25 и 26, управляющие входы 27 и 28, информационные входы 29-32 и выход 33, В устройстве управляющие входы коммутаторов 1 и 2 попарно объединены и подключены к информационным входам 7 и 8 устройства, а их информационные входы подключены к управляющим входам 10-17 устройства. Выход коммутатора 1 соединен со входом элемента НЕ 3 и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 подключен к выходу 18 устройства, а второй вход эле мента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 соединен с первым. входом элемента И 5 и подключен к информационному входу 9 устройства. Второй вход элемента И 5 соединен с выходом элемента НЕ 3, а 35 его выход соединен со входом элемента ИЛИ 6, другой вход которого соединен с выходом коммутатора 2, а выход - подключен к выходу 19 устройства. 46Устройство работает следующим образом.На информационные входы 7 и 8 устройства поступают двоичные переменные А и В, а на вход 9 - входной сигнал заема ЗВ . С выхода 18 уст ройства снимается сигнал Р результата логической или арифметической операции, а с выхода 19 - выходнойсигнал заема ЗВЫ На управляющие входы 10-17 устройства подаются сиг налы настройки И-И 8 с помощью кото- рых коммутаторы 1 и 2 настраиваются на реализацию логических функций переменных А и В таким образом, что логическая функция, реализуемая коммутатором 1, соответствует,промежуточному результату требуемой математической операции без учета входного сигнала Зщ, а логическая Функция, реализуемая коммутатором 2, функции выходного сигнала заема 3 беэ учета входного сигнала заема. Получение окончательного результата операции с учетом входного сигнала заема 3 осуществляется с помощью элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4, ф а выходной сигнал з аема 3 ц с учетом входного сигнала заема Зр элементов НЕ 3, И 5, и ИЛИ 6. Настройка схемы устройства на выполнение требуемой математической операции из набора возможных операций легко находится по таблице истинности операции (этой), составляемой без учета входного сигнала заема Зв .Например, для математической операции А - (А, В Ч А В), которая входит в набор реализуемых операций, имеем без учета входного сигнала заема следующую таблицу истинностиА В 3 , РО 0 О 00 1 1 11 0 О 01 1 0 1Для реализации в устройстве заданной операции необходимо коммутатор 1 настроить на выполнение логической функции Р = А В Ч АВ, а коммутатор 2 - на выполнение логической функции Э = А Э. Для настройки коммутаторов на соответствующие логические функции достаточно двоичный код функции сигнала Р из таблицы истинности подать ыа управляющие входы 10-13 устройства в качестве сигналов настройки И -И а двоичный код функции сигнала 3 и - на входы 14-17 устройства в качестве сигналов настройки И-И 8, Если используется элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, то коммутатор 1 должен настраиваться на функцию инверсии сигнала Рф. Окончательный результат операции Р = РЗВЧР Зв, а получаемый сигнал заема Зщ = З,ц,чР 3Путем настройки коммутаторов 1 и 2 на реализацию различных логических Функций переменных А и В вустройстве возможно выполнвние сле-, дующего набора различных математи-.ческих операций: всех логических операций переменных А и В, арифметических операций вйЧитания: А - В, А в . В,В А - В, В - А, В - А, В - Аг В - А, операций типа Е 1 (А,В) Е (А,В), представляющих собой математические операции одновременного вычисления произвольных логических функций Е 1(А,В) и Е(А,В), перемен-ных А и В и получением арифметической разности значений этих Функций.В целом устройство реализует 256 различных математических операций, что расширяет его область применения в вычислительной технике и позволяет использовать его не только для построения устройств логической обработки двоичных кодов, но и для построения устройств арифмети855655 формула изобретения 10 11 12 13 фиг ВНИИПИ Заказ 6915/69 5 Подписное фиг. ческой и арифметико-логической обработки двоичных чисел. Это в своюочередь позволяет сократить номенклатуру устройств, применяемых в настоящее время в вычислительной техникедля построения различных схем обработки двоичной информации.. Устройство для логической обработки и вычитания двоичных чисел, содержащее два коммутатора, управляющие входы которых попарно объединены и подключены к информационным входам устройства, а информационные входы являются управляющими входами устройства, о т л и ч а ю - щ е е с я тем, что, с целью расширения области применения устройства путем реализации в нем операций 20 вычитания кодов двоичных чисел, в устройство введены элементы НЕ, ИЛИ,7 9 И и ИСКЗПОЧАЮЩБЕ ИЛИ, выход которогоявляется выходом результата устройства, первый вход элемента ИСКЛЮЧИОЩЕЕ ИЛИ подключен к выходу первогокоммутатора и входу элемента НЕ, авторой вход - ко входу заема устройства и к первому входу элемента И,второй вход которого подключен квыходу элемента НЕ, а выход элемента И соединен с одним из входовэлемента ИЛИ, другой вход которогоподключен к выходу второго коммутатора, а выход является выходомзаема устройстваИсточники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР9 370605, кл. С 06 Г 7/50, 1973.2. Сдвоенный цифровой селектормультиплексор 4-1. Аналоговые ицифровые интегральные схемы. Под.ред. С.В. Якубовского. И., "Советское радио", 1979, с. 76, 188 (прототип),1 филиал ППП "Патент",Ужгород, ул, Проектная,4

СмотретьЗаявка

2847381, 06.12.1979

МИНСКОЕ ВЫСШЕЕ ИЖЕНЕРНОЕ ЗЕНИТНОЕ РАКЕТНОЕ УЧИЛИЩЕ ПВО

АСПИДОВ АЛЕКСАНДР ИВАНОВИЧ, КОЗЮМИНСКИЙ ВАЛЕРИЙ ДМИТРИЕВИЧ, МИЩЕНКО ВАЛЕНТИН АЛЕКСАНДРОВИЧ, СЕМАШКО АЛЕКСАНДР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 7/38

Метки: вычитания, двоичных, логической, чисел

Опубликовано: 15.08.1981

Код ссылки

<a href="https://patents.su/3-855655-ustrojjstvo-dlya-logicheskojj-obrabotki-i-vychitaniya-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для логической обработки и вычитания двоичных чисел</a>

Предыдущий патент: Управляемый арифметический модуль

Следующий патент: Цифрочастотное вычислительное устройство

Случайный патент: Способ передачи и приема дальновидения