Преобразователь двоично-десятичных чисел в двоичные

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 717754

Авторы: Выхованец, Гончаров, Онищенко, Сухомлинов

Текст

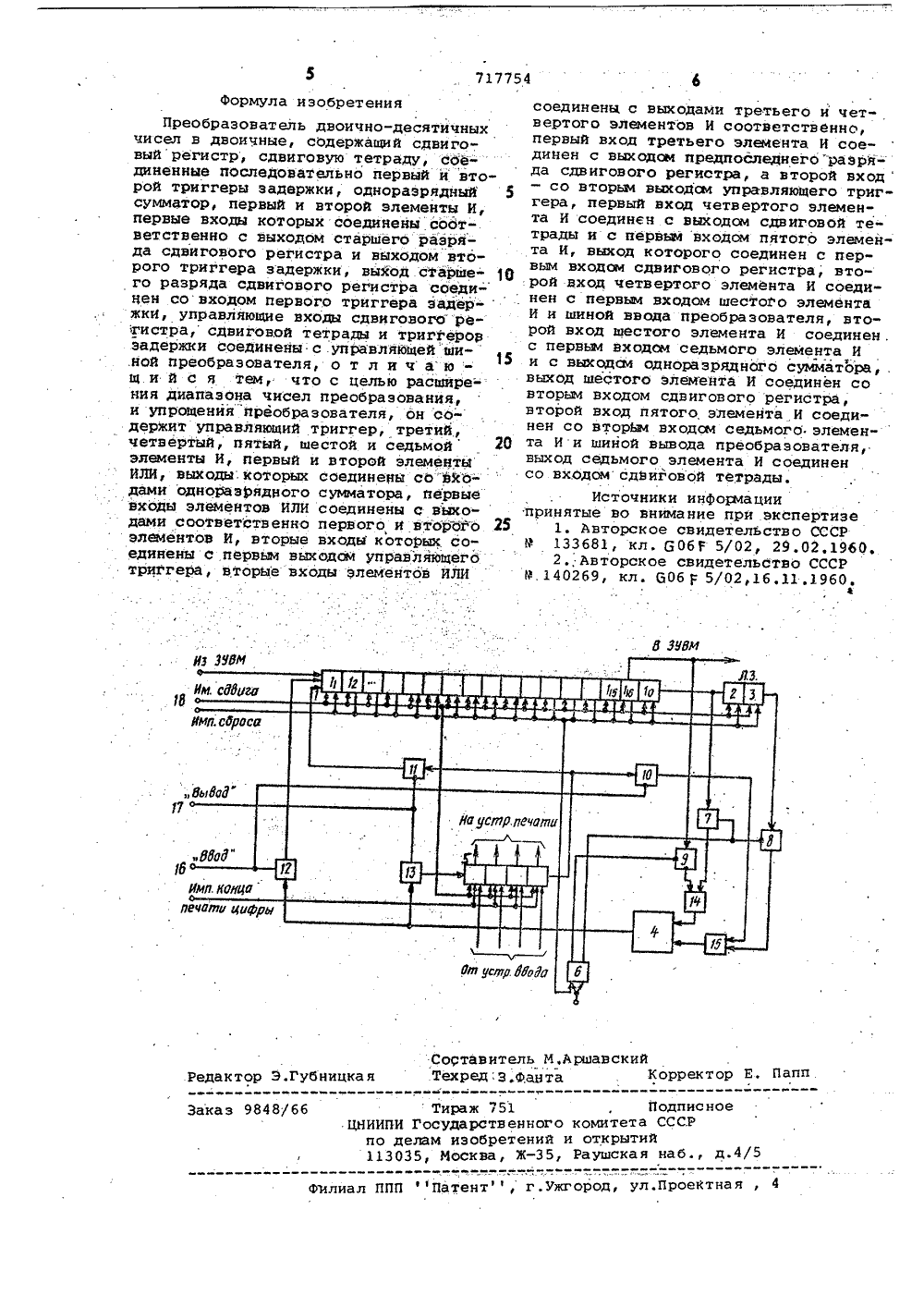

Союз Советскик Социалистических Республик) Допо нительное к авт. свид-вуеио 13,0862 (21) 79078 б/18-24 неиИем заявки М -Заяв исоед Г сударствеииый комите СССР делам изобретений и открытий(7 ) Заявитель 4) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧ ЧИСЕЛ В ДВОИЧНЬЖ ЯТИЧ выход старшего разряда сдвиговогорегистра соединен со входом первоготриггера задержки, управляющиевходысдвигового регистра, сдвиговойтетради и триггеров задержки со-,единены с управляющей шиной преобразователя.Кроме того, известный преобразователь содержит второй сумматор, наборное поле, дешифратор наборного ипереключатель режимов, генераторчек импульсов,Недостатком этого устройства является его сложность и невозможностьпреобразования дробных двоичных чиселв десятичные.Целью изобретения является расзиирение Функциональных возможностей,заключающееся в преобразовании какцелых двоично-десятичных чисел в дво/ичные, так и дробных двоичных чиселв двоично-десятичные и упрощениепреобразователя,Это достигается тем, что он соцержит управляющий триггер, третий, четвертый, пятый, шестой и седьмой элементы И, первый и второй элементыИЛИ, выходы которых соединены со вдами одноразрядного сумматора, пер оля, пахо- вые М.И. Сухомлинов,В.И. 1Изобретение относится к областиавтоматики и цифровой вычнслительной техники и может быть использовано при построении блоков преобразования двоично-десятичных чисел в двоичньре - и двоичных чисел в двойчно-десятичные.Известен преобразователь двоичнодесятичных чисел в двоичные 1), содержащий сдвиговый регистр, сдвиго вую тетраду, два триггера задержки и два одноразрядных сумматора.Недостатком известного устройства является сравнительно большой обьем аппаратуры и невозможность преобразования дробных двоичных чисел в двоично-десятичные.Наиболее близким по технической сущности и конструктивному решению является преобразователь 2) двоичнодесятичних чисел в двоичные, содер" жащий сдвиговый регистр, сдвиговую тетраду, соединенные последовательно первый и второй триггеры задержки, одноразрядный сумматор, первый и второй элементы И, первые входы которых соединены с выходом старшего разряда сдвигового регистра и выходом второ- го регистра задержки соответственйб;30 анец, А.С,Гончаров и Э.Л,Онищенвходы элементов ИЛИ соединены с выходами соответственно первого и второго элементов И, вторые входы которых соединены с первым выходом управляющего триггера, вторые входы элементов ИЛИ соединены с выходами третьего -и четвертого элементов И соответственно, первый вход третьего элемента Исоединен с выходом предпоследнего раз- .ряда сдвигового регистра, а второйвход - со вторым выходом управляющего трйггера, первый вход четвертого и)элемента И сбединен с выходом сдвиговой тетрады и с первым входомпятого элемента И, выход которого соединен с первым входом сдвиговогорегистра, второй вход четвертого элемента И соединен- с первым входом шестого элемента И и шиной ввода преобразователя, второй вход шестогоэлемента И соединен с первым входомседьмого элемента И и с выходом одноразрядного сумматора, выход шесто-го элемента И соединен со вторым входом сдвигового регистра, второй входпятого элемента И соединен со вторымвходом седьмого элемента И и шиной двывбда преобразователя, выход седьмого элемента И соединен со входомсдвиговой тетрады.Блок-схема предлагаемого устройа"тва представлена на чертеже со сладу" Зоющими позициями.Сдвиговый регистр 1, триггеры задержки 2,3, одноразрядный сумматор 4,сдвиговая тетрада 5, управляющий триггер 6, элементы И 7 - 13, элементыИЛИ 14 - 15, шина ввод - 16, шина фвывод в . 17, шина импульсовсдвига - 18.Первый выход сдвигового регистра1 соединен со входом первого триггера задержки 2 и входом первого эле О"мента И 7. Выход второго триггеразадержки соединен со входом второго." элемента И 8. Второй выход сдвигового регистра 1 соединен со входомтретьего элемента И 9, Первые"Входы . 4четвертого и пятого элементов И 1011 соединены с выходом сдвиговой тетрадыВходы шестого и седьмого эле-ментов И 12 - 13 соединены с выходом. одноразрядного сумматора 4, входы у)которого соединены с выходами перво"го и второго элемейтов ИЛИ 14 -15.Перевод целых десятичных чисел вдвоичные производится согласно сле:дующего выражения. К (4"(010+се)404 о+.+ ц "01 офОгде И двоичное число, а д.(- цифра-го разряда двоично-десятичногочисла, и. - номер разряда,Предлагаемое устройство работает 60следуЮщим образом.Сигналом по шине .ввод 16 открйваются элементы И 4,12. При помощиустройства ввода (на чертеже не показано) в сдвиговую тетраду 5 зано сится значениЕ старшего разряда двоично-десятичного числа.Посредством импульсов сдвига число из сдвиговой тетрады 5 через элемент И 10 и элемент ИЛИ 15 подается на вход однЬразрядного сумматора 4.На второй вход сумматора через элемент И 9, открытый потенциалом с выхода триггера б, и элемент ИЛИ 14, подается содержимое сдвигового регистра (регистр перед началом преобразования обнуляется) . С выхода сумматора число поступает через элемент И 12 на вход сдвигового регистра 1. В следующем цйкле производится умножение занесенного в регистр 1 числа на 1010. Для этого управляющий триггер 6 переводится в состояние нуля и открывает элементы И 7,8, через которые число из регистра подается в .сумматор по двум цепям со сдвигом на один и три разряда. Сложение в сумматоре 4 сдвинутых таким, образом чисел равносильчо умножению на 1010, Далее ойисанный процесс повторяется для последующих Цифр числа. После ввода последней цифры числа происходит блокировка умножения на 1010 (цепи блокировки на чертеже не показаны) .преобразование двоичной дроби в двоично-десятичную происходит при поступлении сигнала выводф по шине 17, который отКрывает элеМенты И 11, 13, Сначала двоичная дробь заносится в сдвиговый регистр 1, Затем при помощи импульсов сдвига она поступает в одноразрядный сумматор 1, при этом, производится умножение на 1010. Получаемый результат с выхода сумматора 4 через элемент И 13 поступает в сдвигающую тетрадуи"через элемент И 11 с выхода тетрады на входрегистра.После окончания сдвига в тетраде фиксируется эквивалент первой десятичной цифры.Процесс преобразованйя продолжается до получения нужного чйсла разрядов, Пиклический процесс перевода чисел позволяет использоватьдля построения преобразователей наряду со статическими так же и динамические регистры. В этом случае осуществляется непрерывное циркулирование преобразуемого"кода по цепи регистр, триггеры задержки, сумматор при выработке импульсов выбора тетрад и импульсов сдвига тетрад.Таким образом, предложенное устройство позволяет производить как перевод двоично-десятичных чисел в двоичные, так и обратное преобразование двоичной дроби в двоично-десятичную форму.Предлагаемоеустройство позволяет также сократить объем аппаратуры двоично-десятйчных преобразователей, поскольку исключает один из сумматоров известных устройств.Подпиоомитета СССРоткрытийаушская наб Раж 751 арств еннизобретен осква, Ж 48/ббЦНИИПИ Госпо делам113035,Зака о д,4/5 род, ул.Проектная , 4Ужг т Илиал ПП Преобразователь двоично-десятичных чисел в двоичные, содержащий сдвиговый регистр, сдвиговую тетраду, сое=диненные последовательно первый и второй триггеры задержки, одноразрядный 5 сумматор, первый и второй элементы И, первые входы которых соединены соответственно с выходом старшего разряда сдвигового регистра и выходом второго триггера задержки, выход старше О го разряда сдвигового регистра соеди- нен совходом первого триггера задер-жки, управляюцие входы сдвигового регистра, сдвиговой тетрады и триггеров задержки соединейы:с .Управляюцей ши.ной преобразователя, о т л и ч аю щ и й с я тем, что с пелью расшйре- ния диапазона чисел преобразования, и упроцення преобразователя, он содержит управляюций триггер, третий, четвертый, пятый, шестой и седьмой И элементы Й, первый и второй элементы ИЛИ, выходы;которых соединеий со "вхо дами одно 1 аэрядного сумматора, первые входы элементов или соединены с выходами соответственно первого и второго 25 элементов И, вторые входы которых соединены с первым выходом управляюцего триггера, вторые входы элементов ИЛИ соединены с выходами третьего и четвертого элементов И соответственно, первый вход третьего элемента И соединен с выходам предпоследнегоразря да сдвигового регистра, а второй вход- со вторьм выходсм управляюцего триггера, первый вход четвертого элемента И соедннеч с выходом сдвиговой тетрады и с первый входом пятого элемента И, выход которого соединен с первым входси сдвигового регистра, второй вход четвертого элемента И соединен с первым входом шестого элемента И и шиной ввода преобразователя, второй вход шестого элемента И соединен, с первым входом седьмого элемента И и с выходсм одноразрядного сумматора, . выход шестого элемента И соединен со вторым входом сдвигового регистра, второй вход пятого элемента И соединен со вторЬм входом седьмого элемента И и шиной вывода преобразователя, выход седьмого элемента И соединен со входом сдвиговой тетрады.Источники информации принятые во внимание при экспертизе1. Авторское свидетельство СССР У 133681, кл. 5 06 Г 5/02, 29. 02. 1960.2, Авторское свидетельство СССР Р. 140269, кл, 6065/02,16,11.1960.

СмотретьЗаявка

0790786, 13.08.1962

СУХОМЛИНОВ МАКСИМ МАКСИМОВИЧ, ВЫХОВАНЕЦ ВИТАЛИЙ ИВАНОВИЧ, ГОНЧАРОВ АЛЕКСАНДР САУЛОВИЧ, ОНИЩЕНКО ЭРНЕСТ ЛЕОНИДОВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: двоично-десятичных, двоичные, чисел

Опубликовано: 25.02.1980

Код ссылки

<a href="https://patents.su/3-717754-preobrazovatel-dvoichno-desyatichnykh-chisel-v-dvoichnye.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоично-десятичных чисел в двоичные</a>

Предыдущий патент: Устройство для дешифрирования кодов

Следующий патент: Устройство для преобразования двоичного кода в десятичный и обратно для чисел с плавающей запятой

Случайный патент: Способ и долото для отбора ориентированного керна из бурящихся скважин