Устройство для контроля микроэлектронных логических схем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

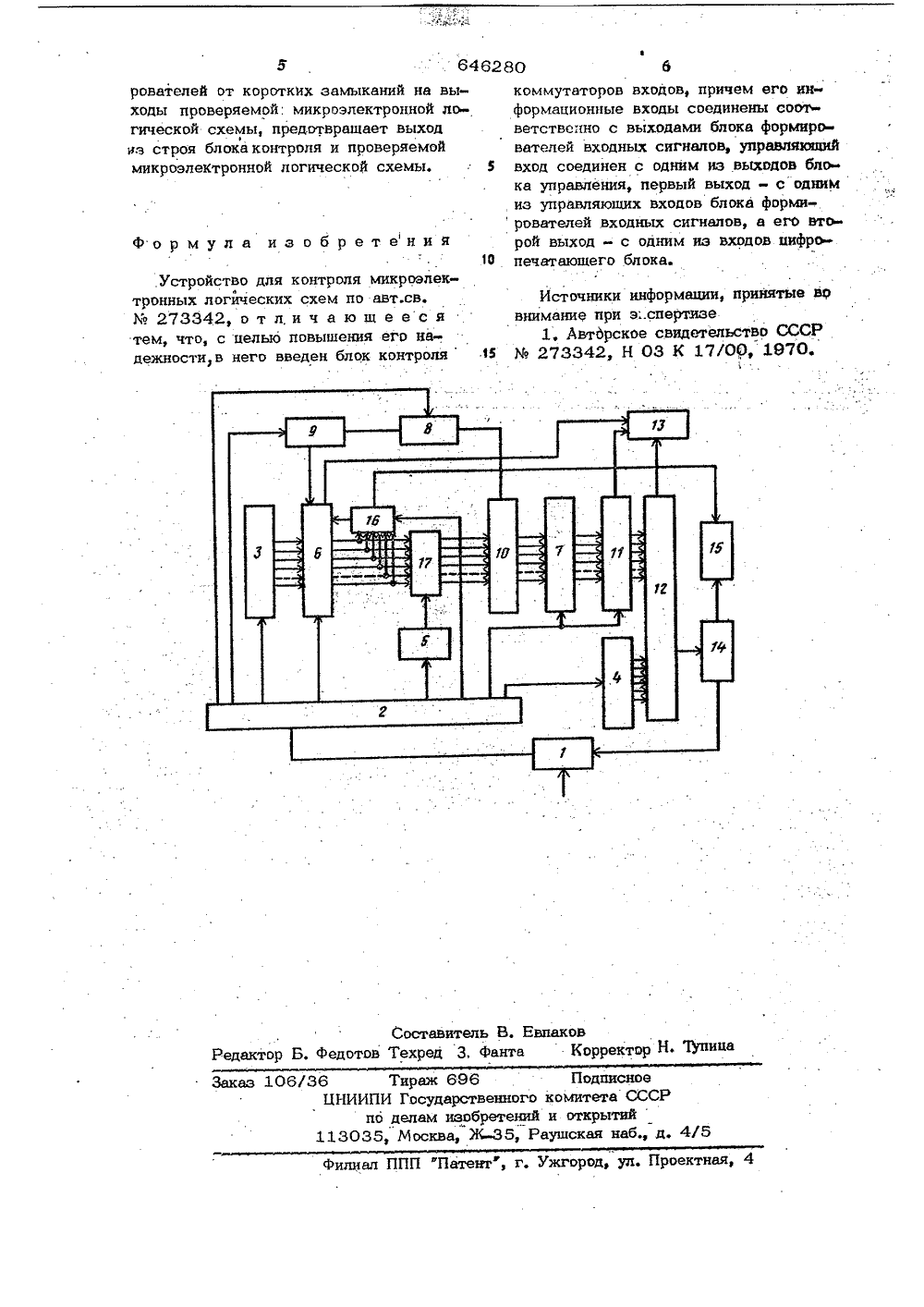

Мйь., ффффМееэ; оюз Советсиин цналистицеских РеспубликДополнител 2) Заявлено 14 присоеринение ое к авт. свид-вухо 27334 4,77 (21) 2474411/18-21 г 51) М. Кл6 01 И 31/28 Н 03 К 17/О аявки ударстееннаа кеинтет СССР не делам нзобрвтен н еткритнй) Заявите ТРОЛЯ МИХ СХЕМ ЛЕКТРОННЫХ ТРОЙСТВО ДЛЯ КО ЛОГИ ЧЕС(5 т блок ввода 1одной регистр. 3,рограммируемыйформирователей ство содержи авления 2, вх регистр 4, и ания 5, блок 1Изобретение относится к контрольноизмерительной технике, в частности к технике программируемых тес новых испытаний микроэлектронных логических схем, может быть использовано для регулировки, контроля правильности функционирования и контроля электрических параметров микроэлектронных логических схем вычислительной техники.Известно устройство для контроля микроэлектронных логических схем, содержащее блок управления, входной, выходной и запоминающий регистры, программируемый блок питания, амплитудный селектор, цифровой блок сравнения, формирователь входных сигналов, блок запуска, блок индикации, цифропечатающий блок, блок ввода и вывода, временной селектор, управляемый элемент задержки 1Недостатком этого устройства являеъся возможность выхода его из строя или повреждения проверяемой микроэлектронной логической схемы в случае, если к 2выходам формирователей входных сигналов устройства подключаются выходыпроверяемой схемы.С целью повышения надежности, в известное устройство для контроля микроэлектронных логических схем по авт.св. Мо 273342 введен блок контроля;коммутаторов входов, причем его информационные входы соответственно соединены с выходами блока формирователейвходных сигналов. управляющий вход соединен с одним из выходов блока управления,первый выход - с одним из управляющих входов блока формирователейвходных сигналов, а его второй выходс одним из входов цифропечатающегоблока.На чертеже приведена структурнаяэлектрическая схема предлагаемого устройства.Устройблок упрвыходнойблок питвходных сигналов 6, амплитудный селектор 7 управляемый элемент звдержки 8, блок запуска 9, временной селектор 10, запоминающий регистр 11, цифровой блок сравнения 12, блок индикации13, выводной блок 14, цифропечатаюшийблок 15, блок контроля коммутатороввходов 16Работает устройство следующим образом. После включения напряжения питания сигнал из блока управления 2 зайре 1 цает появление сигналов на выходахблока формирователей входных сигналов6, а блок контроля коммутаторов входов 16 по сигналу из блока управления2 определяет, являются ли подключенные Ф выходам блока формирователейвходных сигналов 6 выводы МЛС ее вхо-.дами еОтличить вход микроэлектронной логической схемы 17 от выхода можно йо ве-личине напряженйя на выводе, тока, отдаваемого внагрузку, входному сопротивлению и т,п.,Пусть, напрймер, проверяемаямикроэлектронны логическая схема 17 состо-ит из ийтегральных микросхем, В функцйюблока контроля коммутаторов входов 16входит измерение напряжения на "выводах схемы 17. Если это напряжение хотя бы на одном Выводе превышает напряжение на входах интегральйых микросхем или. меньше, чем это напряжение,это значит, что ко входу блокаформирователей входных сигналов 6 ошибочноподключен не вход схемы 17,я поэтомублок контроля коммутаторов входов 16запрещает формирование сигнапов "навы-ходах блока формирователей входных сиг-налов 6; а на блоке индикации 13 индицируются номера выводов микроэлектронных логических схем, напряженйена которых не соотвеФсчвует- входномунапряжению интегральных микросхем.Если напряженйе на выводах схемы17 соответатвует напряжений," нормальному для взводов схемы 17 блок контроля коммутаторов входов 16 разрешаетпоступление сигналов с выходов блокаформирователей входных сигналов 6 навходы йроверяемой" схемы 17.Таким образом, блок контроля-комму.таторов входов 16 предотвращает короткое замыкание выходов блока формирователей входных сигналов 6 на выходыпроверяемой схемы 17,Далее в устройство вводится тестовая программа проверки данной схемы 17, 1 О 15 Эта программа с помощью блока ввода 1 и блока управления 2 записывает во входной 3 и выходной 4 регистры информацию, которую необходимо податьна входы схемы 17 и которая должнабыть на выходах исправной МЛС.Эта же программа устанавливает на программируемом блоке питания 5 требуемое напряжение питания схемы 17;на амплитудном селекторе 7 - допустимые уровни логического ",0" и "1" выходных сигналов, на управляемом элементе задержки 8 - пределы временной селекции выходных сигналов.На блоке формирователей входных сигналов 6 - уровни логического "0" и "1" сигналов, подаваемых на входыМЛС 17.После этого из блока управления 2 в блок запуска 9 поступает сигнал, разрешающий считывание информации со входного регистра 3 в блок формирователей входных сигналов 6. С блока запуска 9 науправляемый элемент задержки 8 поступает сигнап начала отсчетавремени,совпадающйй по времени с из- .менением сигналов на выходах блокаформирователей входных сигналов 6, ко- ЗОторый с элемента задержки 8 в качестве запрещающего сигнала поступает навсе входы многоканального временногоселектора 10.Сигналы на выходах проверяемой схемы 17 появляются с некоторой задержкой, зависящей от схемы 17. Через временной селектор 10 в амплитудный селектор 7 проходят только те сигналы сосхемы 17, которые появляются раньше .прихода запрещающего сигнала с элемен.та задержки 8 на временной селектор 10.Сигйалы,прошедшие через временной селектор, подвергаются амплитудному контролю в амплйтудном селекторе 7.Сигналы, удовлетворяющие требованиям по амплитуде и времени, записываются в запоминающий регистр 11,Информация,зайисанная в запоминающем регистре. 11, вводится в цифровой:блок сравнения 12, где сравнивается с 50требуемой реакцией для задайного теста. Результаты сравнения выводятся наблок индикации 13 ина выводной блок14 и далее - на цифропечатаюший блок15.55Таким образом, введеный в схему блок контроля коммутаторов входов обеспечивает защиту выходов блока формиРедактор Б,Заказ 106/3 Корректор Н. Ъпица 6 Тираж 696 ПодписноеЦНИИПИ Государственного комитета СССРпо делам изобретений и открытий13035, Москва, Ж, Раушская наб., д. 4/5 4 ПП Патенг, г, Ужгород, ул. Прое рователей от коротких замыканий на выходы проверяемой, микроэлектронной логической схемы, предотвращает выход из строя блокаконтроля и проверяемой микроэлектронной логической схемы,ф о р м у л а изобретения.Устройство для контроля микроэлектронных логйческих схем по авт.св. Мо 273342, от л,и ч а ю щ е е с я тем, что, с целью повышения его надежности,в него введен блок контроля коммутаторов входов, причем его ии формационные входы соединены соот ветствепно с выходами блока формирователей входных сигналов, управляющий вход соединен с одним из выходов блока управления, первый выход - с одним из управляющих входов блока форми рователей входных сигналов, а его второй выход - с одним из входов цифропечатающего блока. Источники информации, принятые вовнимание при э;.спертизе1, Авторское свидетельство СССР15 Мф 273342, Н 03 К 17/ОО, 1970.

СмотретьЗаявка

2474411, 14.04.1977

ПРЕДПРИЯТИЕ ПЯ А-3517

ЯЩУК БОРИС АНДРЕЕВИЧ, ПОДДУБНЫЙ НИКОЛАЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G01R 31/3177

Метки: логических, микроэлектронных, схем

Опубликовано: 05.02.1979

Код ссылки

<a href="https://patents.su/3-646280-ustrojjstvo-dlya-kontrolya-mikroehlektronnykh-logicheskikh-skhem.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для контроля микроэлектронных логических схем</a>

Предыдущий патент: Устройство контроля контактирования интегральных схем

Следующий патент: Устройство для измерения магнитных параметров объемных экранов

Случайный патент: Установка для очистки изделий