Преобразователь цифрового кода в аналоговый эквивалент

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 636792

Авторы: Белоцерковский, Ольхович, Ярема

Текст

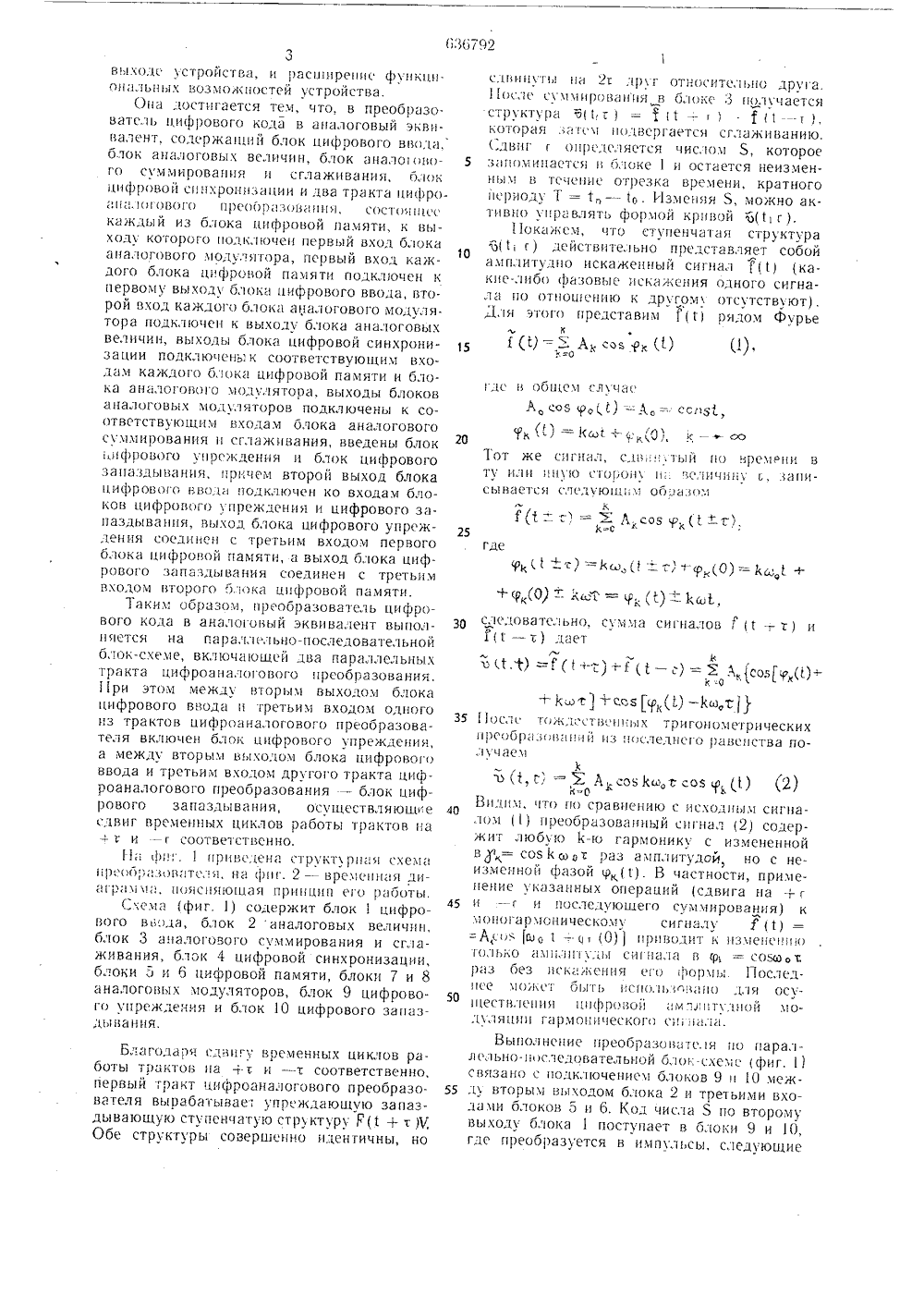

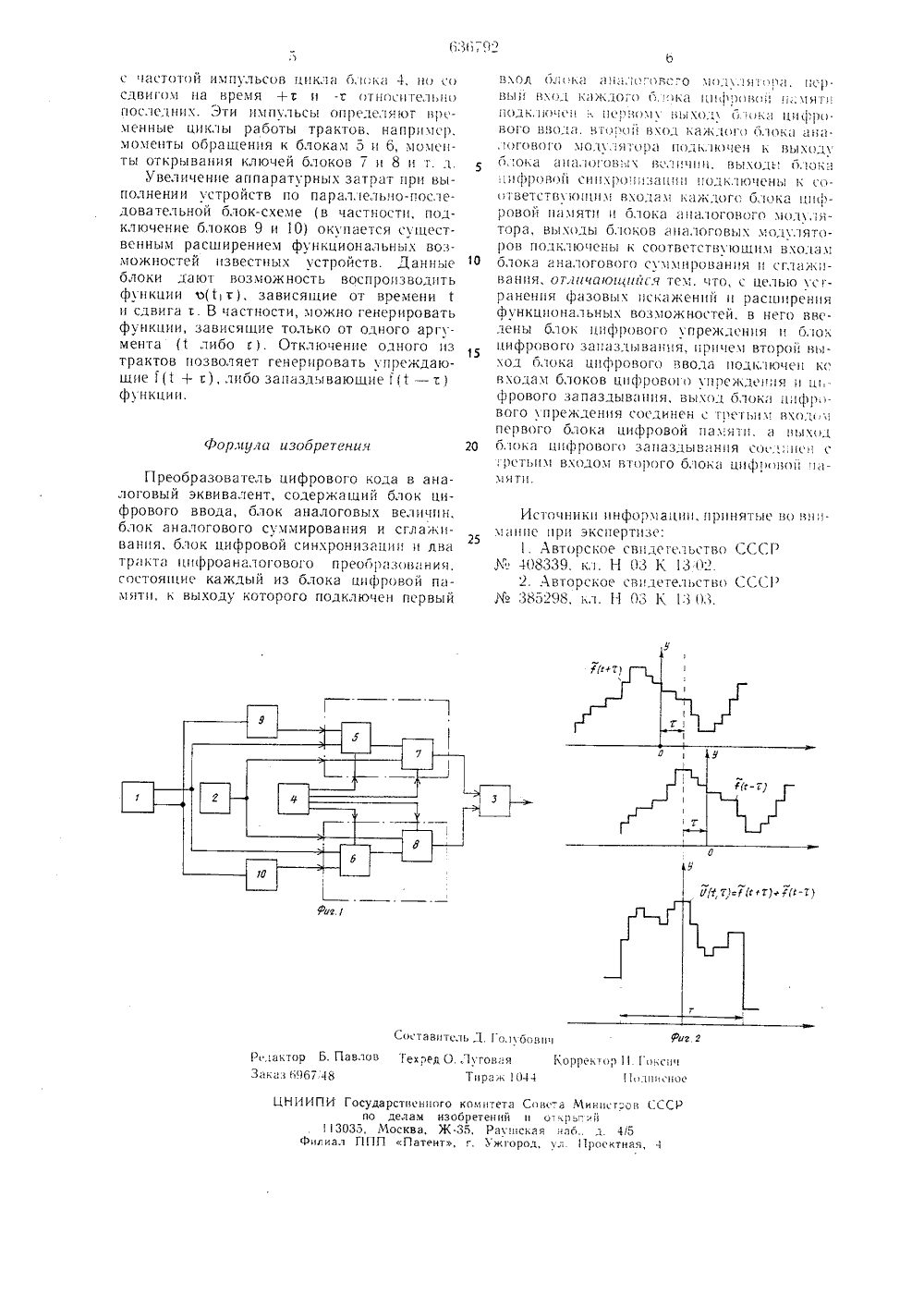

О П И С А Н И Е ( 636792ИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Соретскик Социалистических Республик) 4, Кл присоединением заявки23) Приоритет43) Опубликовано 05. 12.78,Бюллетень 445) Дата опубликования описания 06 д 3 К 13/02 Государственный комитет Совета Министров СССР по делам изобретений и открытий(71) Заявител 4) ПРЕОБРАЗОВАТЕЛЬ ЦИфРОВЭКВИВАЛЕНТ ОДА В АНАЛОГОВЪЙ Изобретение относится к области вычислительной и измерительной техники и может быть использовано для преобразования информации из цифровой формы ваналоговую, а также для цифрового управления амплитудными искажениями сигналапроизвольной формы.Известен преобразователь цЛа в аналоговый эквивалент,на способе последовательного купроизведения зависимости вре,ции 11,ифрового копостроенныисочного восменной фнкжит блок цифрои к нему блокаровой синхронисуммирования и с блоком анаватель содерподключенныпамяти и цианалоговогосоединенныизяторов. м его является наличие фазо й при цифровом управленииискажениями аналоговог ь цифрового коент, содержащийаналоговых весуммирования и й синхронизации зовате вивал а, бло ового ифрово реобра вый эк го ввод аналог блок ц Преобразовоо ввода сми цифровойзации и блоксглаживания,логовых модуНедостатквых искаженамплитуднымисигнала.Известенда в аналогоблок цифроволичин, блокс г; е жв а н5,и лва тракта цифроаналогового нреооразован 5. Ос)рызованньх олокоз цнфзовой а Чт и олоком аналоговых модуляторов, причем блок цифрового ввода подключен ко входу блока цифровой памяти, блок цифровой памяти и блок аналоговых величин управляют входами блока аналоговых модуляторов, выход которого соединен со входом блока аналогового суммирования и сглаживания, выход последнего служит выходом устройства 121.Недостаток известного устройства - оно не может само по себе осуществлять амплитудные искажения воспроизводимого сигнала, не внося при этом никаких фазовых искажений, то есть не способно производить цифровое управление амплитудами всех гараонических составляющих без нарушения фазовых соотношений между ними. Необходимо отметить, что указанный недостаток вызван не составом отдельных блоков, а построением всей блок-схемы устройства.Цель предлагаемого изобретения устранение фазовьх искажений при цифровом управлении амплитудными искажениями аналогового сигнала, воспроизводимого в соответствии с цифровым колом начвьходс стройства, и расширеци фмцкццоняльых Возможностей устройства.Оця достигается тем, что, в преобразователь цифрового кода в аналоговый эквиВалент, содержащий блок цифрового Вв;11, О ЯОК яцялОГОВых Величин, Олок я на;О 15- го суммирования ц сглаживания, глк цифрвой синхронизации и два тракта цифрояна.ового црец)рзнация, сост 5 и каждый из блока цифровой памяти, и выходу которого цолключен первый вход блока ацалогвого модулятора, первый вход какдого блока цифровой памяти подклочсн к первому выоду блока цифрового ввода, второй вход каждого блока аналогового модулятора подключен к выходу блока аналоговых величин, выходы блока цифровой синхронизации подключсцык соответствующим входам каждого блкя цифровой памяти и блока аналогового модулятора, выходы блоков аналоговых молуляторов подключены к соответствующим Входам олока аналогового суммирования и сглаживания, введены блок шфрового упреждения ц блок цифрового запаздывания, причем второй выход блока цифрового ввля подключен ко входам блоков цифрового уцрежления и цифрового запаздывания, выход блока цифрового упрежления соединен с третьим входом первого блока цифровой памяти, а выход олока цифрового запаздывания соединен с третьим входом второго блока цифровой памяти.Таким образом, преобразователь цифрового кода в аналоговый эквивалент выполняется на паралл,ьно-последовательной олок-схеме, вксночаюшсй два параллельных тракта цифроаналогового преобразования.11 ри этм между Вторым выходом блока цифрового ввода и третьим входом одного из трактов цифроаналогового преобразователя включен блок цифрового упреждения, а между вторым выхолом блока цифровог ввода и третьим входом другого тракта цифроаналогового преобразования - блок цифрового запаздывания, осуществляюш е сдвиг временных циклов работы трактов ца -г т и г соответственно.111 1)11. 1 цриВсдена стэдикту рц 151 схем 1црср;зовтсл 51, ца фцг. 2 -- временная ди р 1) Я, цоясц 51 юцая цицци 1 еГО работы.(.хема (фиг. 1) содержит блокцифрового в 1 ла, блок 2аналоговых величин, блок 3 аналогового суммирования и сглаживания, блок 4 цифровой синхронизации, блоки 5 и 6 цирровой памяти, блоки 7 и 8 аналоговых модуляторов, блок 9 цифровог упреждения и блок 10 цифрового зацаз,ы ва н ия.Благодаря с Нгх временных циклов работы тряктоь ца +с и - т соответственно, первыи тракт цифроаналогового преобразователя вырабатывает упреждающую запаздывающую ступенчатую структуру Р(1 + т ), Обе структуры совершенно идентичны, но15 С,1 цицс 1,1 ц; 2 с;рГ Отнситсг 1 ьно друа.11 слс сучНровция в блке 3 цлучается структура (1,г ) =- 1 (1 - г ) 1 (1- -), котОр 1 я зягс) И;ВсрГяетс 51 сг.аж и Вянию. (.двиг гцрслсляется числом Ь, которое зНмицается ц блоке 1 и остается неизменным в течение отрезка времени, кратного Йериолу Т = 1 - 1 с Изменяя , можно активш управлять формой крцвои о(1 с ).110 кяжем, что ступенчатая структура )(1 с ) действительно представляет собой амплитудно искаженный сигнал 1" (1) (какие-либ фазовыс искажения одного сигналя по Отношению к дрхГомм Отсутствмют) . ДГ 5 этого представим 1(1) ряЛом Фурье1(Ц=,Б Ак сна Рк (1) (1)лс ц общем случяА, сВ р,(1) -- А, =- сс.,-1- М г .)- Сся (,(Ц - )т 3 1 сл гжлствнных тригонометрическихцрсбрязнаций из цлелцего равенства получаем.0(1, г) =Х АсоьЬ.гсов( (2)Видим, чт и сравнению с исходным сигналом (1) преобразованный сигнал (2) содержит любуо )с-ю гармонику с измененнойВ = сов )ссот раз амплитудой, но с неизменной фазой р (1). В частности, примецение указанных операций (сдвига на +г4 и г и последующего суммирования) кмоцгармоническому сигналу Г (1)=ДсВ со 1 - 1(0)1 приводит к з)ецсцц0,ЬКО 1 МЦ.Ц Х.Ы СИна 1 Я В ГР = СГИ о Тряз без искажения ег формы. Послелцсе мжст быть цсц.1 Гоцяцо лля осуцествлсция цифровой ям - .тулцсй моЛЛЯЦИИ ГЯРМОНЦЧЕСКГГО И Ц 1 Г 11.Выполнение цреобрязонятс.я цо параллгьно-цследовательОй блок-схс. с (фиг. 1)связаи с полклочениех блоков 9 ц 1 О меж 55 лу вторым выходом блока 2 и третьими вхо.ями блоков 5 и 6. Код числя Я по второмувыходу блока 1 поступает в олоки 9 и 10,где преобразуется в импульсы, следующие.)ос) в)и Р.)актор Б. Павл31)каз 6)62 13 О. Пуговин гира к 04 Ео 1 ки) лииио). игор НИИПИ Государпо13033, М Филиал ППП та0) кг) Минит:овв)" 31бд. 4/531 роектнан ствнного комитета Со елам изобретений и сква, Ж, Рау)иска Патенти г. Ужгород с 1 астотс)й импульсов цикла блока 4, ПО Гл) сдвипм на время +с и -т с)тпвстел)нс) Г)ос.)е;1 нг)х. Зтг Пхпульс. Опреде,яюг Временные циклы работы трактов, например, моменты оорашения к блокам 5 и 6, моменты открывания ключей блоков 7 и 8 и г. д.Увеличение аппаратурных затрат при выполнении устройств по параллельи-последовательной блок-схеме (в частности, подклочение блоков 9 и 10) окупается су 1 цественным расширением функциональных возможностей известных устройств. Данные блоки дают возможность воспроизводить функции о(1)т), зависяшие от времени и сдвига с. В частности, можно генерировать функции, зависяшие только от одного аргумента (1 либо с). Отключение одного из трактов позволяет генерировать упреждаюшие 1(1 + с), либо запаздываюшие 111 - Т.1 функции. Г 1 реобразователь цифрового кода в аналоговый эквивалент, содержаший блок цифрового ввода, блок аналоговых величин, блок аналогового суммирования и сглажи 25 вания, блок цифровой синхронизации и лвя тракта ш)фроаналогового преобразования, состоящие каждый из блока цифровой памяти, к выходу которого подключен первый Вход с)л с к 11 я);1,13) Гс) Бс О .3)дт, 1511 и 1, пер. Бы и Бхс).1 кяждОГО б, ч)кя цп)13) Бс)31 и;.мят) подк,1 Очеп к пе 1 нс)т 1 Б 1 з 1 хс)д с) )с)1 цифр)- ВО 0 ББОДС. Бто;)Ои Вход КЯж;10 с) Олок 11 13 н 11- 1 С)ГС)БОГО МО 1) 153 ГО)Р;1 ПС) ДК,1 ЮЧСН 1, БЫХС)Д С),1 ОКЯ Я ПЯ,10 ОБЫ Х ВЕ, ПЧ 3. П, ВЫХОДВ 0,10 К 11 СИ)РОБО СИПХРОППЗЯЦПП ПОДК 1 К)ЧС.НЫ К С- с)тветствОНим Входам каждого блока цифровой п 11)яти и блОка 1 Н 51,1 ОГОБс)ГР .111:1),151- ТОРЯ, ВЫХС)ДЬ О.1 ОКОБ ЯНЕ)ЛОГОВЫХ МО;1,1 ЯТО- ров подкл)очены к соответствуюцгим вхо:151 Олока яна,1 ОГОВОГО см 15 НрОВянп 51 и сГл 11 жпвания, от.гг)ссгоСсггйея тем. что, с целью усгранения фазовых искажений и расширения функц 3)снальных возможностей, в него введены блок цифрового упреждения и б,ок цифрового зяпаздывяшя, причем второй Выход олока цифрового Вводя подклочеп ке Входам блоков цифрового упреждения и ц- фрового запаздывания, выход блок;1;ифр,)- вого упреждения соединен с греты)м Вход) м пеРВОГО О;1 О к Я Г 1 31 ф Р ОБО Й и а м 51 т и, 13 1311 х с) д б,ОКа цпфрОВОГО ЗапаЗдЫВННПя СОдион С :ретьпм входом второго блока цифВ)вс)й ПЯ- мяти. Источники информации, принятые БО Б)1)- тЯПИЕ ПРП ЭКСПЕРТИЗЕ:1. Авторское свидетельство СССР Ле .408339, кл. Н 03 К 13 11.

СмотретьЗаявка

2184339, 14.10.1975

ПРЕДПРИЯТИЕ ПЯ В-8751

БЕЛОЦЕРКОВСКИЙ БОРИС МИХАЙЛОВИЧ, БЕЛОЦЕРКОВСКИЙ ИСААК МИХАЙЛОВИЧ, ОЛЬХОВИЧ ВИТАЛИЙ ВЛАДИМИРОВИЧ, ЯРЕМА МИХАИЛ ФЕДОРОВИЧ

МПК / Метки

МПК: H03K 13/02

Метки: аналоговый, кода, цифрового, эквивалент

Опубликовано: 05.12.1978

Код ссылки

<a href="https://patents.su/3-636792-preobrazovatel-cifrovogo-koda-v-analogovyjj-ehkvivalent.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь цифрового кода в аналоговый эквивалент</a>

Предыдущий патент: Пороговое устройство

Следующий патент: Преобразователь сигнала цифровой и кусочно-аналоговой формы в аналоговый

Случайный патент: Реостатный преобразователь линейных перемещений