Преобразователь двоичных десятиразрядных чисел в двоично десятичные

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

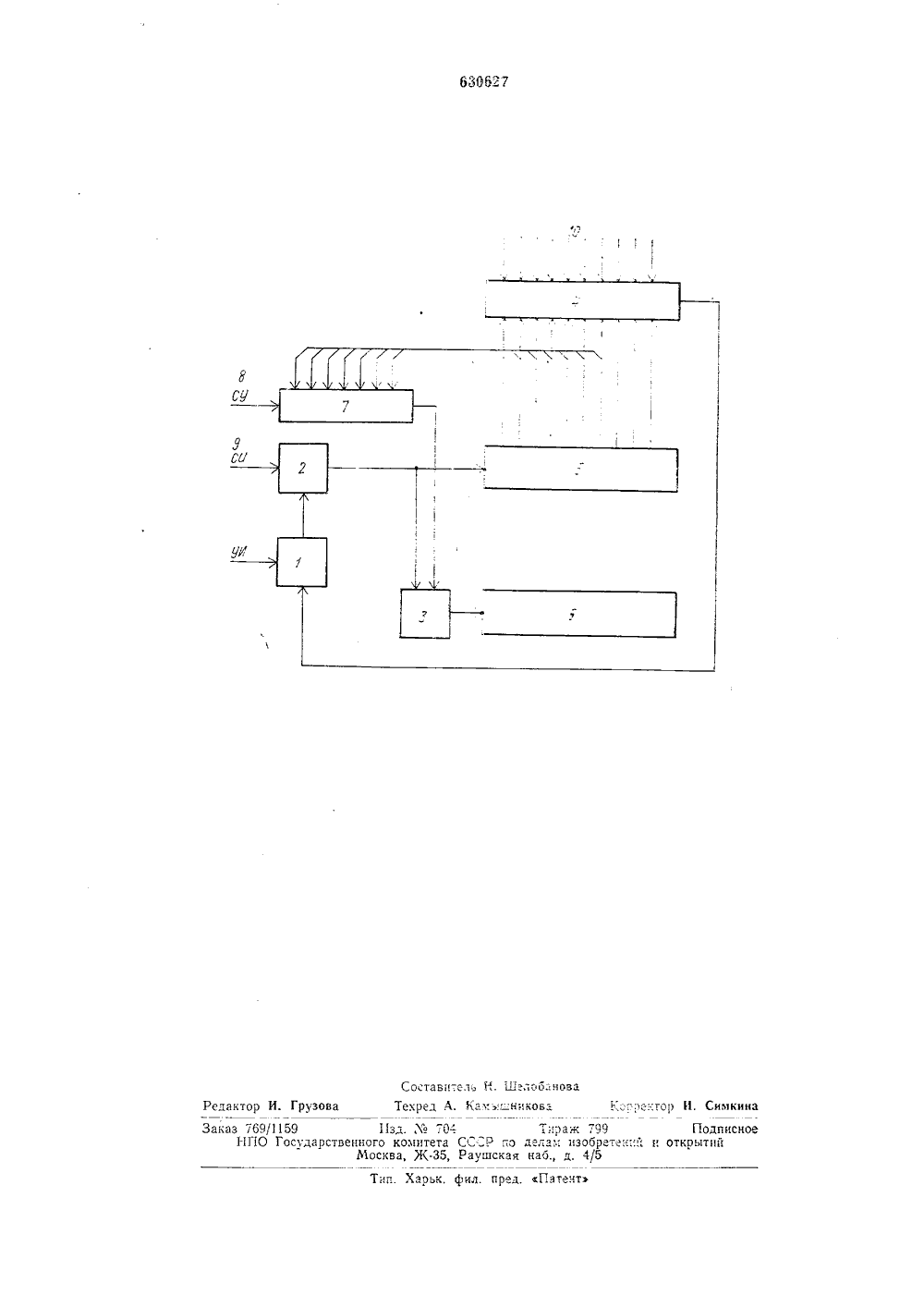

,10.7. - 1 ол лете.1 ь,й откр ыти 45) Дата опубликования описания 01.1.(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНЬ ДЕСЯТИРАЗРЯДНЫХ ЧИСЕЛ В ДВОИЧНО-ДЕСЯТИЧНЫЕ я и ают Изобретение относится к вычислительной технике, а более конкретно к преобразователям двоичных чисел в двоично-десятичные, которые используются в цифровыхвычислительных машинах,Известны преобразователи двоичныхчисел в двоично-десятичные, работающиепо принципу накопления десятичных эквивалентов разрядов преобразуемого двоичного числа и содеркащие двоичные и десятичные счетчики и дешифраторы, сумматоры, усилитель-формирователь, схемы выделения, вычитания и запоминания десятков,ключи 1,Однако такой преобразователь отличается сложностью схемы и может применяться только для преобразования целых двоичных чисел,Наиболее близким по технической сущности к предложенному является преобразователь двоичных чисел в двоично-десятичные, содержащий триггер, подключенныйвыходом к одному из входов элемента И,другой вход которого подсоединен к входной шине, а выход - ко входу двоичногосчетчика, двоично-десятичный счетчик 2,Работа данного преобразователя происходит следующим образом.Десятичный счетчик устанавливаетснуль. Счетные импульсы (СИ) поступ на входы двоичного и десятичного счетчиков до переполнения двоичного счетчика, С этого момента прохождение импульсов па входы счетчиков прек 1 ащается, так как импульс с выхода двоичного счетчика изменяет состояние триггера, вследствие чего элемент И закрывается. Результат преобразования фиксируется в десятичном счетчике.О В преобразователях такого рода моментокончания счета импульсов может определяться другим способом, а именно с помощью схемы сравнения на равенство входного двоичного кода и кода двоичного 15 счетчика. Тогда оба счетчика перед началом преобразования должны устанавливаться в нуль. Такое решение, не меняя принципа работы преобразователя, позволяет использовать счетчики, не имеюцце 20 входов для занесения параллельного кода,например в интегральном исполнении.Недостаток подобных преобразователейсостоит в невозможности их применения для преобразования дробных чисел.25 Цель изобретения - расширение диапазона преобразуемых чисел.Поставленная цель достигается тем, чтов преобразователь введены схема сравнения, анализатор двоичного кода и второй 30 элемент 11. Информационные входы преоо.:0 принятые во разователя подключены к первой группе в.,одов схемы сравнения, а ее вторая Груг.- па входов - к разрядным выходам двоичного счетчика, семь младших разрялов которого соединены с входами анализато;1 а двоичного кода, УправляОший зход анализатора соединен с шиной установки ежима, а выхол - с одним из вколов зто.,ого элемента И, связанного другим входом:, выходом соответственно с вхолами лзоич.ного и двоично-десятичного счетчихсв. Выход схемь сравнения подключен к упразляющему входу триггера. Анализатор двои-.- НОГО кода содержит три э,те".ента 11. Груп.пы входов Оторых являОтея вхола:, а:-ализатора двоичного кола, - выхоль: под.ключеиы к входам элемента 11,. И, зь:ход которого служит выходом анализатора двои шого кода,На чертеже представлена блох-схе:,апреобразователя двоичных лесятиразрялных чисел в лвоично-десятичные,Она содержит триггер 1, элементы 11 2, Л, схему 4 сравнения, двоичный б и лвои Но- десятичный б счетчики, анализатор 7 двоичного кода, шину 8 установки режима и входную шину 9, информационные входы 10 преобразователя.В начале цикла преобразования установочный импульс (УИ) обнуляет счет:яки и устанавливает триггер 1 в состояние, при котором элемент И 2 открыт. Через этот элемент счетные импульсы (СИ, 11 оступают на вход двоичного счетчика б, Гока его когл не станет равньв Вхолному ;.Своичному числу. В этот момент схемасравне 11 ия выдает сигнал, устанавлизающий триггер 1 в исходное состояне, после чего элемент И 2 закрывается и поступление импульсов на счетчики прекращается. В режиме преобразования целых чисел анализатор 7 двоичного кода выключен и элемент И 3 постоянно открыт. Псэтому оба счетчика к концу цикла преобразова. пия сосчитают одинаковое количество пульсов, и на выходах счетчика б установится целое число, соотве:стзуюп;ее входному двоичному числу. В режиме преобразования лробных чисел по сигналу установки реж:эа греоб. разования дробных чисел (СУ) включается анализатор 7 двоичного кода, которь: периодически закрывает элемент И 3, с:беОпечивая блокировку одного имп);тьса на входе счетчика б при определеннь 1 х комбинациях разрядов двоичного счетчика Е,При преобразовании максимального двоичного дробного числа 1 - .имеющего единицы во всех разрядах, количество заблок 1110 ва:11 Ых шп;льсоз равно 2 40 4 50 55 24. В результате двоичный счетчик б сосчитает 1023 импульса, а двоично-десятичный 999, что соответствует десятичному числу 0,999, так как запятая фиксируется перел третьим старшим десятичным разрядом. Моменты блокировки импульсов равномерно распределены по всему лиапазону лвоичных чисел таким образом, что из каждых 128 импульсов, составляюших восьмую часть полного диапазона, исклю. чаются 21, 64 и 107 импульсы. Поэтому к анализатору 7 лвоичного кода, солержашему, например три селектора (элементы Й), выхолы которых объединены по схеме ИЛИ, присоединены только семь младших разрядов двоичного счетчика б.Предложенный преобразователь позволяет производить преобразование лво 1;чных лесятиразрялных как цельх, так и дробных чисел в лвоичио-лесятичные. Формула изобретения 1. Преобразователь двоичных десятиразрялных чисел в двоично-десятичные, содержащий триггер, полключенны выходом к одному из входов элемента И, другой вход которого подключен к входной шине преобразователя, а выход - ко входу двоичного счетчика, лвоично-десятичный счетчик, отлич а ющийся тем, что, с целью расширения диапазона преобразуемых чисел, в него введены схема сравнения, анализатор двоичного кода и второй элемент И, причем информационные входы преобразователя подключены к первой группе входов схемы сравнения, вторая группа входов которой соединена с разрядными выходами двоичного счетчика, семь младших разрядов которого соединены со входами анализатора двоичного кода, управляюший вход которого соединен с шиной установки режима, а выхол - с одним из входов второго элемента И, связанного дрггим входом и выходом соответственно с входами двоичного и двоичнодесятичного счетчиков, выход схемы срав. пения подключен к управляюитему входу триггера.2. Преобразователь по п. 1, о т л и ч аю щ п й с я тем, что анализатор двоичного кода содержит три элемента И, группы входов которых являются входами анализатора двоичного кода, а выходы подключены к входам элемента ИЛИ, выход которото является выходом анализатора двоичного кода,Источники информации,внимание при экспертизе:1. Авторское свидетельство СССР ;й 225551, кл. б 06 Г 5/02, 1967.2. Сухомлинов М. М, и Выхованец В.И. Преобразователи кодов чисел. Киев, изд. Чехника, 1965, с, 68, рис. 14,

СмотретьЗаявка

2439325, 10.01.1977

ПРЕДПРИЯТИЕ ПЯ А-3759

ОЗЕРОВ АРКАДИЙ БОРИСОВИЧ, РОМАНОВА ЛИДИЯ ВАСИЛЬЕВНА

МПК / Метки

МПК: G06F 5/02

Метки: двоично, двоичных, десятиразрядных, десятичные, чисел

Опубликовано: 30.10.1978

Код ссылки

<a href="https://patents.su/3-630627-preobrazovatel-dvoichnykh-desyatirazryadnykh-chisel-v-dvoichno-desyatichnye.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоичных десятиразрядных чисел в двоично десятичные</a>

Предыдущий патент: Буферное устройство канала вводавывода

Следующий патент: Устройство для умножения

Случайный патент: Устройство для заглубления трала