Арифметико-логический модуль

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 598069

Авторы: Нестеренко, Яковлев

Текст

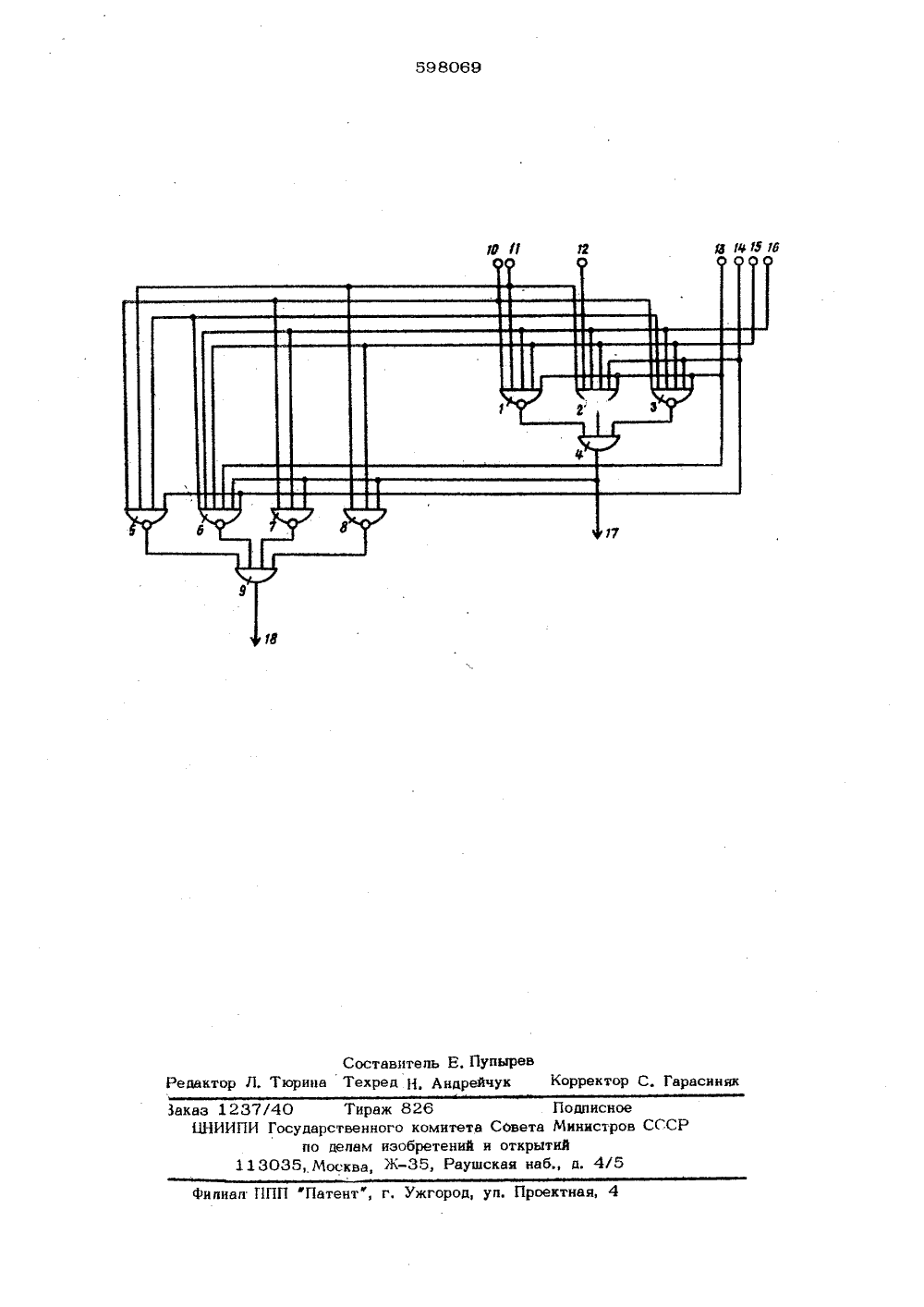

Соеог Советских Социалистицеских Республик(45) Бата опубликования описания 17:02.78 Государственный неинтет Сааатв Мнннетрев СЫР не делим нзоеретеннй н етнрьпнй(54) ЛРИФМЕТИЕО-ЛОП 1 ЧЕС 11 ИЙ МОЬУНЬ Изобретение относится к автоматике ивычиспитепьной технике.Известно устройство дпя выполнения арифметических и логических опервццй,;содержашее три источника напряжения, резистор 5нагрузки и эпементы с непинейцо изменяющимся сопротивпениемЦ. Это известноеустройство не может выполнять функцииарифметического спохсения и коммутациивходных сигнапов. Нвибопее бпиэким к изоб Оретению техническим решением являетсяарифметико-погический модупь, содержащийлогические элементы И-НЕ, И два входа,вход переноса, информационный выход и выход переноса т 21, Однако и оно не может 15выпопнять функции логического спожецияи коммутации (пересыпке кодов слагаемыхчерез сумматор),Цепью изобретения явпяется расширениефункциональных воэможностей путем ревпиза 20ции функций коммутации и погйческсго спожения. В описываемом модупе это достигается тем,что в него введены четыре управпякипихвхода, причем первые четыре входа первого и второго эпементов И-НЕ соединены 25 соответственно с четырьмя управпя 1 ошцмнвходами модуля, пятые входы первсго ивторого эпементов И-НЕ соединены с входом переноса, шестые входы первого и второго эпементов И-НЕ соединены, соответственно, с первым и вторым информациснцымвходами модупя, с первым и вторым входами третьего элемента И-НЕ, третий, четвертый и пятый входы которого соединены соответственно, с первым, третьим и четвертым упрввпяюшими входвмн мсдупя, а выходы первого, второго и третьего эпементовИ-НЕ подкпючены, соответственно, к первому второму и третьему входам первого эпемента И, соединенного своим выходом с выходом переноса и с первыми входами четвертогс, пятого и шестого эпементсв ИЕ,второй вход шестого эпемецтв ИЕ соединен с первым упрввпяюшим входом модупя, а третий, четвертый и пятый входы шестого эпемента И-НЕ соединены, соответственно, с вторым входом четвертого эпементв И-НЕ и третьим управпяюшнм входв;вторым входом пятого эпементв ИЕ иеетвертым упрввпяюшим входом, первымвходом седьмого элемента И-НЕ и с вторымуправпяюшим входом модупя, шестой входшестого элемента ИНЕ соединен с входомпереноса, с вторым входом седьмого эпемента И-НЕ, третий и четвертый входы которого соединены, соответственно, с третьими входами четвертого и пятого эпементов И-НЕ и с первым и вторым информационными входами, выходы четвертого,пятого, шестого и седьмого элементов И-НЕ цсоединены, соответственно с первым, вторым, третьим и четвертым входами второго элемента И, подкпюченногок информапнонному входу модупя.На чертеже показана схема описываемого модупя.Он содержит эпементыИ-НЕ 1,2 и 3,первый эпеменг И 4, .эпементы И-НЕ 5,6,7,и 8, второй эпемент И 9, информационныевходы 10 и 11, вход 12 переноса, управпяюшие входы 13,14,15 и 16, выход 17переноса и информационный выход 18.При подаче на управпяюший вход 13сигнвпв отрицатепьной попярности на информационном выходе 18 модупя ревнизуется погическое спожение ИЛИ сигналов, подаваемых на информационные входы, 10 и11, При подаче на управляющий вход 14сигнала отрицательной попярности на информационном выходе модуля 18 реализуется 50функция сложения по модупю двв сигналов,подаваемых на информационные входы 10и 11, При подаче на управляющий вход 15сигнапв отрицатепьной полярности на информационном выходе 18 модупя появляетсясигнал, равный сигнапу на информационномвходе 10 (реализуется функция коммутации входа 10), Опя реализации функциикоммутации информационного входа 11 науправляющий. вход 16 подается сигнап от 40рицатепьной попярности, При подаче сигнвпов попожитепьной понярности на все управляющие входи на. информационном выходе 18 модупя реапизуется поразрядная сум 45ма, а на выходе 17.переноса модуля реализуется поразрядный перенос сигнапов наинформационных входах 10 и 11 и на входе12 переноса. При подаче всех остальныхкомбинаций сигналов на управпяюшие вхо 50ды и на выходах модуля реализуется функция константы "Оф ипи 1,Таким образом, достигается многофункционапьность арифметико-погического модупя и обеспечивается воэможность припожеЯния его при построении однородных процессоров. Форму па изобретения Арифметико-логический модуль, содержащий погические элементв И-НЕ и И, два входа, вход переноса, информационный выход и выход переноса, о т и и ч а юш и й с я тем, что, с цепью расширения функционапьных возможностей путем реапизацни функции коммутации и функции логического спожения, в него введены четыре управпяющих входа, причем первые четыре входа первого и второго элементов И-НЕ соединены соответственно с четырьмя упрввпян шими входами модуля, пятые входы первого и второго элементов И-НЕ.соединены с входом переноса, шестые входы первого и вто рого эпементов И-НЕ соединены, соответственно с первым и вторым информационными входами модудя, с первым и вторым входамн третьего элемента И-НЕ, третий, четвертый и пятый входы которого соединены соответственно, с первым, третьим и четвертым управляющими входами модуля, а выходы первого, второго и третьего элементов И-НЕ подключены, соответственно, к первому второму и третьему входам первого.элемента Исоединенного своим выходом с выходом переноса и с первыми входами четвертого пятого н шестого элементов И-НЕ, второй вход шестого эпемента И-НЕ соединен с первым управляющим входом модупя, а третий, четвертый и пятый входы шестого экемента И-НЕ соединены, соответственно, с вторым входом четвертого элемента И-НЕ и третьим управляющим входом, вторым входом пятого элемента И-НЕ и четвертым управляющим входом, первым входом седьмого эпементв И-НЕ и с вторым управляющим входом модуля, шестой вход шестого эпемента И-НЕ соединен с входом переноса, с вторым входом седьмого эпемента И-НЕ, третий и четвертый входы которого соединены, соответственно, с третьими входами четвертого и пятого элементов И-НЕ и с первым и вторым информационными входами, выходы четвертого, пятого, шестого и седьмого элементов И-НЕ соединены,. соответственно, с первым, вторйм, третьим и четвеотым входами второго эпемента И, подключенного к информационному выходу модуля.Источники информации, принятые во вни мание при экспертизе:1. Авторское свидетепьство СССР М 470804, кл. 6 г 06 У 7/00, 1972.2. Карцев Н. А. Арифметика цифровых машин, М., "Наука, 1969, с. 157.598069 д Р 1816 ю О Гарасиняк аказ 1237/40 Тираж 826 ОНИИПИ Государственного комитета СОвет по депам изобретений и откр 113035 Москва, Ж, Раушская нФипиал ППП "Патент", г, Ужгород, уп. Проектна Составитеп едактор Л. Тюрина Техред ц, Е, Пупыревдрейчук Корректо Подписноеа Министров СССРытийб., д. 4/5

СмотретьЗаявка

1998755, 20.02.1974

ПРЕДПРИЯТИЕ ПЯ А-7160

НЕСТЕРЕНКО ЮРИЙ ГРИГОРЬЕВИЧ, ЯКОВЛЕВ ЮРИЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/38

Метки: арифметико-логический, модуль

Опубликовано: 15.03.1978

Код ссылки

<a href="https://patents.su/3-598069-arifmetiko-logicheskijj-modul.html" target="_blank" rel="follow" title="База патентов СССР">Арифметико-логический модуль</a>

Предыдущий патент: Амплитудно-временной анализатор

Следующий патент: Устройство вычисления функций

Случайный патент: Способ закрытой раскатки колец