Дифференциальный усилительный каскад

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 581569

Автор: Лапицкий

Текст

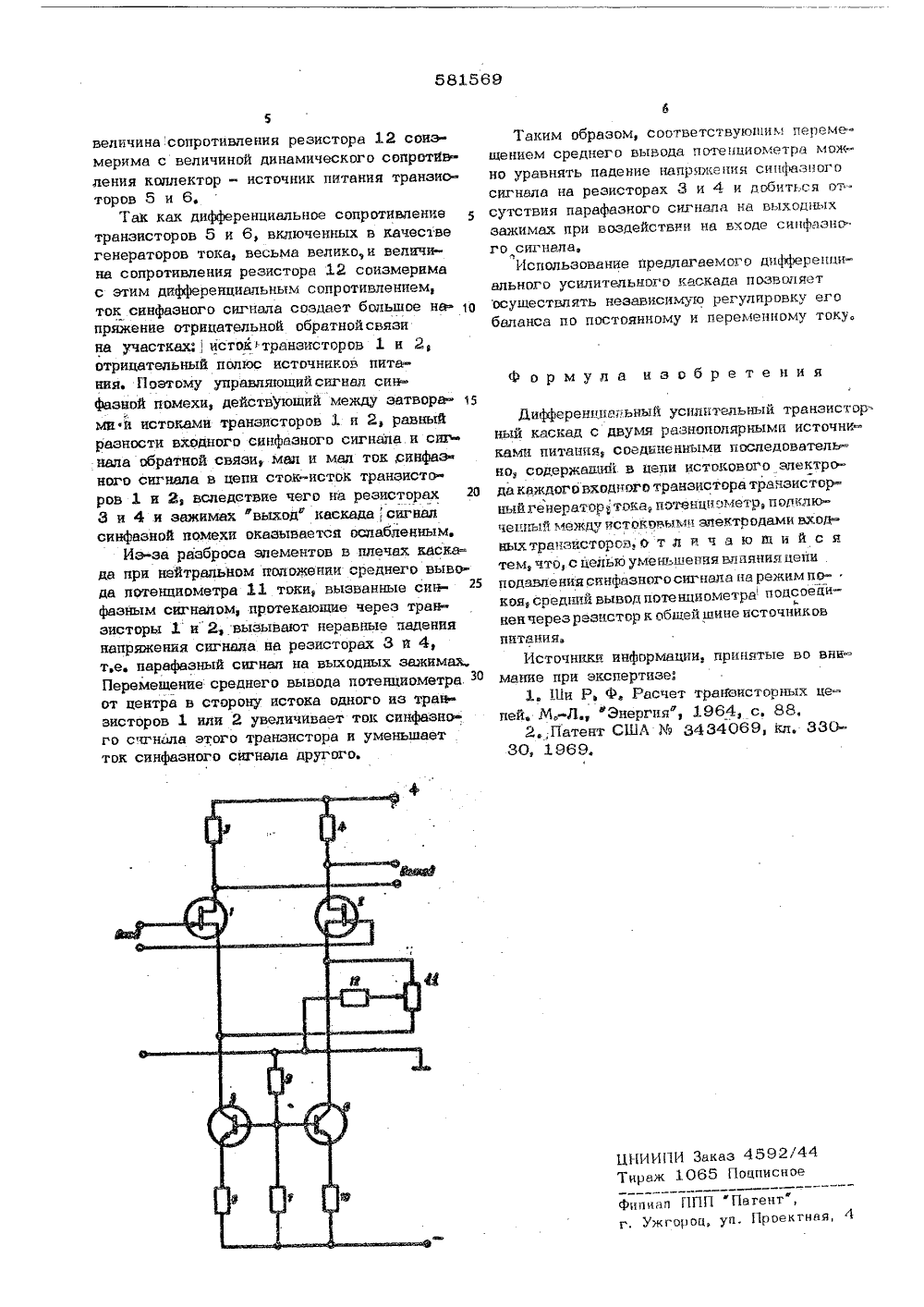

Союз Советскии Социалистических Республик.(51) М, Кл.Н 0 ЗГ 3 05/18 заявки исоединен Приоритет юсудврстввинми иамитетСаввта Министров СССРио делам иаобретеиийи стиРытий ллетень 4(71) Заявите АЛЬНЫИ УСИЛИТЕЛЬНЫЙКАСКАД 54 1Изобретение относится к радиоалектронье н может быть использовано в апектронных устройствах, в которых требуется уселение дифференциапьных сигналов и выделение нх синфаэных помех;Известны дифференциальные усипитепьные каскады с двумя рвэнопопярными источника ми питания, содержащие в цепи истоков (ами теров) входных транзисторов генератор тока и потенциометр, подсоединенный между упомли 1 нутыми апектродами 111 и 2. Подбором положения среднего вывода потенциомет. ра может быть попучен либо баланс по реже му покоя, либо баланс по сигналу, соотвеч ствующих Юиитутствию пврафаэного сигнала 1 на симметричном ютходе каскада при воздействии на его вход сигнала синфаэной по мехи.Таким образом, настройки цепи подавпепия синфаэной помехи сопровождается измене.О пнем режима покоя транзисторов каскада1 Наибопее близким техническим решениеямявляется дифференциальный усилительныйквокад с двумя последовательно соединенными 25 источниками питания, содержащий в цепи втокового апектрода каждого входного транзистора генератор тока и резистор, включенный между истоковыми апектродами 2) .Недостатком известного дифференциального усилительного каскада, является зависимость режима покоя транзисторов от настройки цепи подавленияаннфазных сигналов, например изменение соотношения сопротивленийрезисторов в цепи амиттеров транзисторовгенераторов тока, Настройка цепи подавления на бвпвж по сигналу сопровождаетсяразбалансом по постоянному напряжению итоку, и обратно, настройка на баланс в режвме покои вызывает разбаланс по сигналу н4появление парафазного сигнала, на симметричном выходе каскада при воздействии на еговход сигнала синфазной помехи,Целью изобретения является уменьшениевлияния цепи пбдввлення синфазного сигналана режим покоя, т,е, обеспечение независимости статического режима от регулировкибаланса по свгнвлу,Это достигается тем, что в дифференциальном усилительном каскаде с двумя нсточниками питания, соединенными последователь но, содержащем и цепи истокового электрода каждого транзистора генсратор тока и потен иъмь-.р, включенный менц 1 у истоковыми алектродами, средний вывод потенциометра подключеи через резистор к точке соединения источников питания.В таком каскаде беэ существенного усложнения схемы достигается практическая независимость режима покоя от настройки цепи 10 подавления синфазной помехи на баланс као када по сигналу.На чертеже дана принципиальная апектрн ческая схема предлагаемого дифференциального усилительного каскада. 15Дифференциальный усилительный каскадсодержит 1 тр, нзисторы . и 2, к затворам которых присоединен источник входного сигна ла.,Резисторы 3 и 4 в цепях их истоковых электродов являются нагрузками транэисто ров 1 и 2, К резисторам 3 и 4, с которых снимается выходной сигнал, подключен вход второго каскада. Транзисторы 5 и 6 включены в цепи истоков транзисторов 1 и 2, образуя с делителем напряжения, состоящим 25 из резисторов 7 и 8, симметричный генера тор тока, Делитель напряжения из резисторов 7 и 8 в цепи без транзисторов 5 и 6 и резисторы 9 н 10 в цепях змиттеров этих транзисторов определяют,режим покоя каска- ЗО да.Потенциометр 11 подключен между истоками транзисторов 1 и 2 и служит регулировочным элементом цепи подавления,синфаэФ ного сигнала, величина его сопротивления Зб определяет также глубину отрицательной обратной связи по парафаэному сигналу,Резистор 12, соединяющий средний вывод потенциометра 11 с общейшиной источников литания, образует с транзисторами 5 и 6 гене раторов тока цепь подавления синфазного сир.иалааПостоянная составляющая тока транзисторов 1 и 2 протекает по цепи;,положительный полюс последовательно соединенных источни 45ков питания, резистор 3 ( резистор 4) участокколлектор-емиттер транзистора 5 (транзисто мра 6), резистор 9 (реэистор 10), отрицательный полюс источников питания. Часть постоянной составляющей тока транзисторов 1 и2, протекающая через потенциометр 11 ирезистор 12, весьма мала, так как разностьпотенциалов между общей шиной источниковпитания и эмиттерами транзисторов 1 и 2определяется лишь напряжением смещения,а спопротивление резисторов 12 велико, оносоизмеримо с динамическим сопротивлениемцепи; коллектор транзистора 5 (транзистора 6), отрицательный полюс источников питания60 При перемещении среднего вывода потенциометра 11 изменение величины постояннойсоставляющейтокатранзисторов 1 и 2 пренебрежимо мало, так как оно определяется величиной разности напряжений смещения. Ток покоятранзисторов 1 и 2 может измениться измененем соотношения плеч делителя из резис-оров 7, и 8. Балансировка по режиму покоякаскада, проводится изменением соотношениясопротивлений резисторов 9 и 10, Величина постоянной составляющей выходного сигнала определяетсятокомпокояи резисторами 3 и 4,Дифференциальный усилительный каскадфункционирует следующим образом,.При наличии на входе полезного парафааьного сигнала между затворами каждого изтранзисторов 1 и 2 и общей шиной источников питания действует половина напряженияэтого сигнала, При этом сигналы, действующие нн промежутках затвор-исток транзисторов 1 и 2, равны по величине и противоположны по фазе.Ток парафазного сигнала в каскаде замыкается по цепи сток транзистора 1, истоктранзистора 1, потенциометр 11, исток транзистора 2, сток транзистора 2, резистор 4,резистор 3, сток транзистора 1.,В цепь, подавлениясигналов синфазнойпомехи, состоящую иэ транзисторов 5 и 6генераторов тока и резистора 12, ток парафазного сигнала практически не ответвляется, так как сопротивление этой пепи для тока сигнала великоНа потенциометре 11создается наиряжейие отрицательной обрачной связи, которое уменьшает величину управляющего напрвкения нарафазного сигнайа,действующего между затворами и истоками.транзисторов 1 и 2. С резисторов 3 и 4снимается выходное напряжение усиленногонарафазнзго сигнала.При воздействии на вход сигнала синфазной помехи между затаором каждого из транзисторов 1 и 2 и общей шиной действуютравные налряженни. Ток синфазного сигналав плечах каскада протекает соответственнопо цепям сток - исток тразисторов 1 и 2,коллектор .- эмиттер транзисторов 8 и 6,резисторы 9 и 10, последовательно соединенные источники питания, резисторы Д и 4,сток транзисторов 1 и 2. Часть тока синфазного сигнала каждого плеча от истоковтранзисторов 1 и 2 ответвляется через соответствующееплечо потенциометра 11 ирезистор 3;е, соединенный общей шиной иоточников питания.Величина тока синфазного сигнала, протекающего через почЬнциометр 11 и резистор 12, соизмерима с величиной тока синфазного сигнала, протекающего через транзисторы 5 и 6 генераторов тока, так какНИИПИ Заказ 4592/4 нраж 1065 Поцпнсное Фипиап Г 1 ПП Пате г. Ужгород, уп. П тнея,5величина сопротивления резисторе 12 соизмерима с величиной динамического сопротйвления коллектор - источник питания транзисторов 5 и 6.Так как дифференциальное сопротивление транзисторов 5 и 6, включенных в качестве генераторов тока, весьма велико, и величина сопротивления резисторе 12 соизмерима с этим дифференциальным сопротивлением, ток синфазного сигнала создает большое на о пряжение отрицательной обратнойсвязи на участках: исток транзисторов 1 и 2, отрицательный полюс источников питания. Поэтому управляющий сигнал синфаэной помехи, действующий между затвора ми й истоками транзисторов 1 и 2, равный разности входного синфазного сигнала и сиг нала обратной связи, мал и мал ток,синфаз ного сигнала в цепи сток-исток транзисторов 1 и 2, вследствие чего на резисторах 20 3 и 4 и зажимах выход каскада,сигнал синфаэной помехи оказывается ослабленным,Иэ-эа разброса зпементов в плечах каскада при нейтральном положении среднего вывода потенциометра Х 1 токи, вызванные синфазным сигналом, протекающие через транзисторы 1 и 2, вызывают неравные чадения напряжения сигнала на резисторах 3 и 4, т,е. парафазный сигнал на выходных зажимал Перемещение среднего вывода потенциометра 30 от центра в сторону истока одного из тран;- зисторов 1 или 2 увеличивает ток синфазного сигнала этого транзистора и уменьшает ток синфазного сигнала другого. Таким образом, соответствующим перемэ.- щением среднего вывода потеяциометре можно уравнять падение напряжения синфезного сигнала на резисторах 3 и 4 и добиться от. сутствия парафезного сигнале не выхошпях зажимах при воздействии не входе сицфезнаГо сигнала,Использование предлагаемого дифференциального усилительного каскада позволяет ссуществлять независимую регулировку его баланса по постоянному и переменному току. Ф ормула изобретения Дифференциальный усилительный транзистор=ный каскад с двумя резнополярными источниками питания, соединенными последовательно, содержащий в цепи истокового электрода каждого входного транзистора тречзисторныйгенератор тока, потеыциометр, подключепный между истоковы 1 я электродами входныхтранзисторов о т л и ч е ю щ и й с ятем, что, с целью уменьшения влияния цепиподавления синфаэного сигнала на режим покоя, средний вывод потенциометра подсоеаиненчерез реэистор к общей шине источнйковпитания,Источники информации, принятые во внимание при экспертизе;Х, Ши Р, Ф, Расчет траФисторных цепей. -Л., "Энергия", 1964, с. 88,2,;Патент СШЛ И 3434069, кл. 330 ЗО, 3.969.

СмотретьЗаявка

1958405, 06.09.1973

ПРЕДПРИЯТИЕ ПЯ А-3469

ЛАПИЦКИЙ АНАТОЛИЙ ИОСИФОВИЧ

МПК / Метки

МПК: H03F 3/34

Метки: дифференциальный, каскад, усилительный

Опубликовано: 25.11.1977

Код ссылки

<a href="https://patents.su/3-581569-differencialnyjj-usilitelnyjj-kaskad.html" target="_blank" rel="follow" title="База патентов СССР">Дифференциальный усилительный каскад</a>

Предыдущий патент: Мостовой усилитель мощности

Следующий патент: Перестраиваемое частото-избирательное устройство

Случайный патент: Рабочее колесо прибойного двигателя