Программное задающее устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

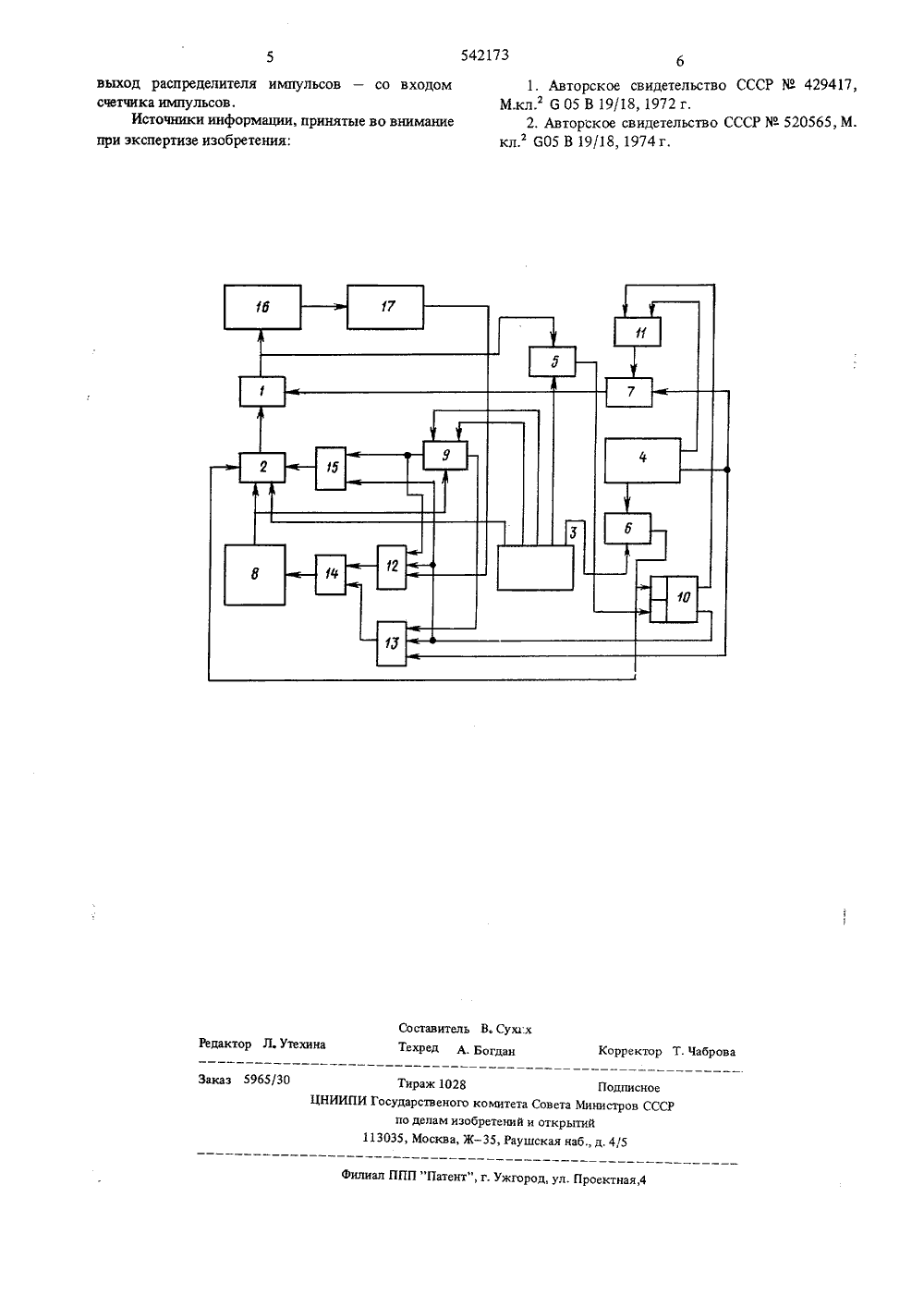

ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советских Социалистицеских Республикс присоединением заявкисударственнн 1 й комитетоввта Министров СССРпо делам изобретенийи открытий оритет -бликовано 05.01.77. Бюллетень1 21-503 55 (088 8 б) Дата опубликования описания 11.04.7 2) Авторыизобретения В. М. Балыбин, С. Ф. Вялых, И. Ф. Двирко, Б. С, Егоров, А. А. Козлови Ю. В. Незнамов 1) Заяви 4) ПРОГРАММНОЕ ЗАДАЮЩЕЕ УСТРОЙСТВО етение относится к области автоматикильной техники, а именно к устройствараммного управления, например, средзи. Изобр вычислите для прог м свя Извес е устроиство, торы импуль.ответственно с устройством арифметичесно программное задающ е первый и второй генер довательно соединенные сочастоты, схемой ИЛИ и одер жа ов, послелителе оединенным со в управлени 10 ния, устанавливать диапа ведется зондирование или лов связи, и автоматическ ную перестройку прием лиапазоне частот с выбра стот, в которыхсвободных канаствлять синхронустановленном поис ник тм шагом перестроики вязи, а область его примене недостаточно широк кого устроиства, и со счетчиком текущего времени, арифметическим устройством и исполнительным органом, содержащее также устройство ввода, соединенное с регистром памяти, выходы которого подключены ко входам арифметического устройства. Это устройство, предназначенное для числово го программного управления координатными перемещениями, не может быть использовано для управления средствами связи, так как не обеспечивает перестройку частоты этих средств по заданной программе 1). 20Наиболее олизким техническим решением к данному изобретению является программное задающее устройство, содержащее блок ввода программы, выходы которого подключены ко входам коммутатора, первой схемы сравнения, другой вход которого через счетчик импульсов подключен к выходу коммутатора, и входу второй схемы сравнения, другой вход которой соединен с выходом задатчика времени, а выход - с одним из входов коммутатора и триггера. Выход первой схемы сравнения подключен к другому входу триггера, выходы которого соединены с первыми входами элементов И, Вторые входы первого и второго элементов И подключены к выходам задатчика времени, соединенного с распределителем импульсов. Выходы второго и третьего элементов И подсоединены ко входу элемента ИЛИ. Это устройство позволяет автоматически определять начало цикла зондироваОднако такое устройство не позволяет произво дить автоматический поиск свободных каналов свя и непосредственно на рабочих частотах, разрешеных для данной линии сЦель изобретения - расширение области применения устройства.Эта цель достигается тем, что в предложенное устройство введены последовательно соединенные блок памяти, вход и выход которого подключены к выходу элемента ИЛИ и входу коммутатора соответственно, и третья схема сравнения, вход которой подсоединен к выходу блока ввода программы, а выход - ко входам третьего и четвертого элементов И, Выход четвертого элемента И соединен со входом коммутатора, а выход распределителя импульсов - со входом счетчика импульсов.Функциональная схема устройства приведена на чертеже.Устройство состоит из декадного счетчика импульсов 1, коммутатора 2, блока ввода программы 3, задатчика времени 4, первой 5 и второй 6 схем сравнения, распределителя импульсов 7, блока памяти 8, третьей схемы сравнения 9, триггера 10, элементов И 11 - 13, элемента ИЛИ 14 и элемента И 15. Устройство работает следующим образом.При совпадении на схеме сравнения 6 времени, поступающего с электронных часов задатчика 4, с временем начала цикла зондирования, установленным на пульте блока 3, эта схема выдает импульс начала зондирования, Этот импульс поступает на коммутатор 2 и триггер 10. При этом начальная частота зондирования, предварительно установленная на пульте блока 3, через коммутатор 2 записывается в счетчик 1, а триггер 10 открывает элемент И 11. Импульсы, следующие с периодом смены частот, с задатчика 4 через элемент И 11 записывают единицу в распределитель 7. Эта единица прогоняется по распределителю импульсами тактовой частоты с задатчика 4. Импульсы с выхода распределителя поступают на вход счетчика 1 и перестраивают его с выбранным шагом перестройки. На каждой частоте сигнал,принятьй приемником 16 оценивается анализатором 17. Схема сравнения 6 сравнивает конечную частоту зондирования, установленную на пульте блока 3, с частотой, поступающей со счетчика 1. При совпадении этих частот схема выдает импульс, который опрокидывает триггер 10, элемент И 11 закрывается и перестройка частоты счетчиком 1 прекращается, а триггер 10 открывает элементы И 12, 13 и 15, После этого на пульте блока 3 устанавливают начальную и конечную частоты диапазона анализа, определенного по результатам зондирования. Эти частоты сравниваются на схеме сравнения 9 выбора частоты с рабочей частотой, записанной в первом адресе блока памяти 8 (частоты в блоке памяти записаны в порядке возрастания их номиналов). Если частота, записанная по первому адресу блока памяти 8, не попадает в диапазон анализа, установленньй на пульте блока 3, схема 9 закрывает элементы И 12 и 15 и открьгвает элемент И 13. При этом адресный вход блока памяти через элемент ИЛИ 14, элемент И 13, подключается к тактовой цепи задатчика 4. Блок памяти опрашивается с тактовой частотой до тех пор, пока очередная рабочая частота не попадает в диапазон анализа.Ь После этого схема 9 открывает элементы И 12,15 и закрывает элемент И 13, При этом рабочая частота через коммутатор 2 записывается в счетчик 1, в адресный вход блока памяти 8 отключается от тактовой цепи задатчика 4 и подключается к 111 анализатору 17.По окончании анализа на этой частоте анализатор 17 выдает импульс, который через элемент И 13 и элемент ИЛИ 14 поступает на адресный вход блока памяти 8, и в счетчик 1 записывается следую щая рабочая частота и производится ее анализ.Этот процесс продолжается до тех пор, покаочередная рабочая частота не вьйдет из диапазона анализа. Как только это произойдет, схема 9 закры вает элементы И 12, 15 и открывает элемент И 13, асхема сравнения 6 опрокидывает триггер 10, который закрывает элементы И 12, 13 и 15. После этого на пульте блока ввода программы 3 устанавливается новый диапазон анализа, и процесс повторяется. Я 5Предложенное устройство осуществляет поисксвободных каналов связи непосредственно на рабочих частотах данной линии связи, что сокращает время поиска свободного канала, а, следовательно, 30повышает эффективность всей системы связи.Формула изобретенияПрограммное задающее устройство, содержащее блок ввода программы, выходы которого подключены ко входам коммутатора, первой схемы сравнения, другой вход которой через счетчик 4 О импульсов подключен к выходу коммутатора, ивходу второй схемы сравнения, другой вход которой соединен с выходом задатчика времени, а выход - с одним из входов коммутатора и триггера, выход первой схемы сравнения подключен к 4 д другому входу триггера, выходы которого соединены с первыми входами элементов И, вторые входи первого и второго элементов "И" подключены к выходам задатчика времени, соединенного с распределителем импульсов, выходы второго и третьего элементов "И" подсоединены ко входу элемеи.та "ИЛИ", отличающееся тем, что, с целью расширения области применения устройства, в него введены последовательно соединенные блок памяти, вход и выход которого 55 подключены к выходу элемента "ИЛИ" и входукоммутатора соответственно, и третья схема сравнения, вход которой подсоединен к выходу блока ввода программы, а выход - ко входам третьего и четвертого элементов "И", выход четвертого 60 элемента "И" соединен со входом коммутатора а542173 Составитель В. Сух 1Техред А Богдан дактор Л. Утехи ректор Т. Чаброва каз 5965/3 одни сное стров СС овета Ми ретений и открытий - 35, Раушская наб.,4/5 Филиал ППП "Патент", г. Ужгород, ул. Проектная,4 выход распределителя импульсов - со входомсчетчика импульсов.Источники информации, принятые во вниманиепри экспертизе изобретения: Тираж 1028 ПИ Государственого по делам изо 113035, Москва, Ж61. Авторское свидетельство СССР В 429417,М.кл.2 6 05 В 19/18, 1972 г.2. Авторское свидетельство СССР М, М.кл.2 605 В 19/18, 1974 г.

СмотретьЗаявка

2139148, 11.05.1975

ПРЕДПРИЯТИЕ ПЯ Г-4554

БАЛЫБИН ВАЛЕНТИН МАТВЕЕВИЧ, ВЯЛЫХ СПАРТАК ФИЛИППОВИЧ, ДВИРКО ИВАН ФЕДОРОВИЧ, ЕГОРОВ БОРИС СЕРГЕЕВИЧ, КОЗЛОВ АЛЕКСАНДР АЛЕКСЕЕВИЧ, НЕЗНАМОВ ЮРИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G05B 19/18, G05B 19/406, G05B 19/418

Метки: задающее, программное

Опубликовано: 05.01.1977

Код ссылки

<a href="https://patents.su/3-542173-programmnoe-zadayushhee-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Программное задающее устройство</a>

Предыдущий патент: Многоканальное устройство для программного управления

Следующий патент: Способ контроля газового наполнения герметизированных двухэлектродных приборов

Случайный патент: Способ получения