Устройство для обнаружения и исправления ошибок в системе остаточных классов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

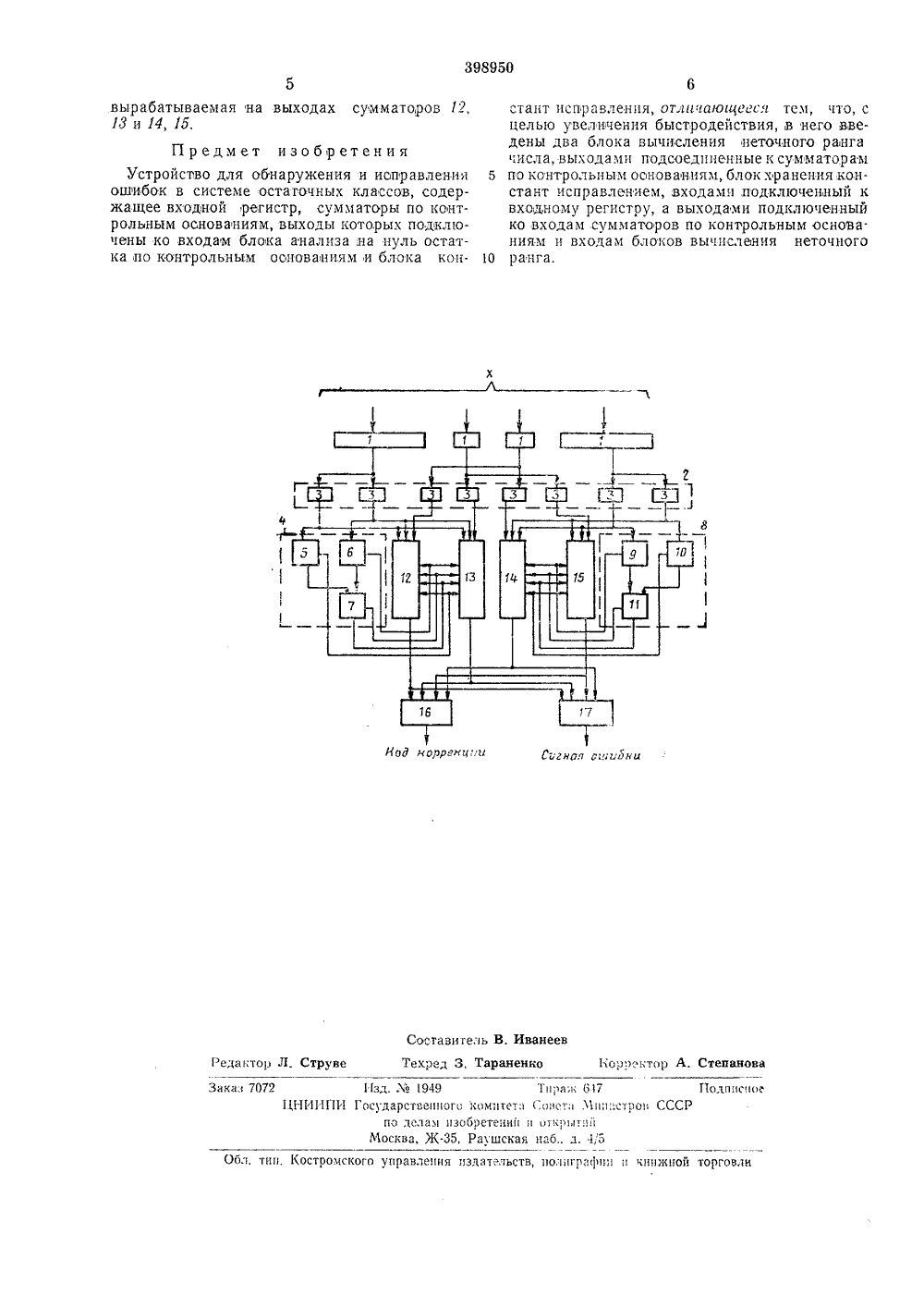

ОП ИСАНИ Е ИЗОБРЕТЕНИЯ Союз Советских Социалистиыеских РеспубликК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Зависимое от авт. сзидетельства-Заявлено 10.11,1971 (% 162626918-24)с присоединением заявки-Пр 1 иоритет -Опубликовано 27.Х,1973, Бюллетень хЪ 38Дата опубликозания описания 27.111.974 М. Кл, б 061 11/00 Государственный комитетСовета Министров СССРпо делам изобретенийи открытий УДК 681,327.66 (088.8) Авторыизобретения И. Я. Акушский, В. М. Амербаев, Ю. Л, Захаров и В. С. Кокорин Заявитель УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВИзобретение Овн Оси тс 51 и вы ч и "л 11 тел ьнн 1 техничке, ч частностаик устройствам для обнаружения и исправления ошибок в системе остаточных классови может быть использовано при построении надежных цифровых устройств.Известно устройство обнаружения и исправления ноформации, представленНОЙ в ссе остаточных классов. Устройство содержит входной регистр, сумматоры по контрольным основаниям, выходы которых подключены ко входам блока анализа на нуль остатка по контрольным основаниям и блока констант исправления ошибки, подключенното к выходу блока определения места ошибки. Оно характеризуется последовательным выполнением операции нулевизации для выявления ошибочной цифры в исходном числе и недостаточным быстродействием.Описываемое устройство отличается тем, чтэ в него введены два блока вычисления неточного ранга числа, выходами подсоединенные к суммато 1 рам по контрольным основаниям, блок хранения констант исправлением, входами подключенный к,входному регистру, а выходами подключенный ко входам сумматоров по контрольным оонованиям и входам блоков вычисления 1 неточного ранга, Это увеличивает быстродействие устройства.На чертеже показа 1 на блок-схема устройства контроля и исправления одиночных модульных Ошибок с неточным вы 1 ислением р 11 нг 1 в одном из варинтов выполнения.Для более полного пояснения работы устройства приводится описание алгоритма обнаружения и исправления ошибки с использованием неточных значений ранга.Опи "ание алгоритма. Устройство формирования ранга существенно сокращается в оборудовании. если вместо точного ранта ) непо О зиционного кода с и символами формироватьего приближенную величину Хи, причем О= и+;-, где ". - неопределенная величина, которая может принимать значения О или15 Пусть задан нспозиционный код (а 1, а.,а.). Под одиночной ошибкой модульного типа или просто модульной ошибкой понимается произвольное искажение одного из символов 2 О непозиционного кода. При этом предполагается, что искаженный символ принадлежит к клаосу символов по рассматриваемому модулю. Под операцией расширения .понимается формирование вычета по пос)д числа х, пред)5 ставленного чепозиционным надоем (а 1, а),а:) по основаниям РР , Р . Операция расширения требует точного восстановления величнны ранга непозиционного кода (а, ае, , а ) .3 О Аппаратура ф ор м и р ов а н ия точного ранга сизмерима с аппаратурой перевода числа, представленного непозиционным кодом, в иепознционный,Устройство основано на использовании в процессе декодирования операции расширения с неточным формированием величины ранга, благодаря чему достигается существенное сокращение оборудования устройства декодирования.Возможность построения такого устройства обосновывается следующим,предложением. Условные обозначения:х р - наименьший,неоприцательный вычет целого числа х по пюдр;с х 1-- целая часть от деления целого числа х на число р, в результате которого получается остаток )х;РпЯК 1 К 2 - кодовый диапазон АУ ЦВМ, где К К 2 - контрольные основания, Я=Р +1;- ЗР 2(х(ЗРЯ - диапазон допустимых значений числа х.Пусть- синдром,модульной ошибочки, формируемый иа основе операцип расширения с оснований Рва КК 2 ц с оснований Я на КК в неточным определением рангов. Тогда, синдроммодульной ошибки имеет структуру (1), если ошибка 71 имела место по одному из ооиований 1 диапазоца Р Я,;=-( )+РК г, (с 1), если ошибка 7 К, имела место по контрольному основанию КьБ = 1 Яч 1 К 2КК 2(аналогично, если ошибка 7 К. имела место по основанию К 2),К= /ЬК 1 г 1 Л 1 Кгде ЛК 1 = (К, -ЛК, (ЦР ЯКа) 1 К 1 )Как следует из указанного предложения, разброс синдромов, связанный с формированием неточеного ранга, невелик (определяется параметром р). Аналитическая форма синдромов указывает алгоритмический прием подбора .контрольных ооцований Кь К 2, удовлетворяющих требованию разделимости ошибок.Устройство контроля и иеправлеиия внформнции содержит (см. чертеж) входной регистр 1, предназначенный для временного запоминания остатков числа х по соответствующим модулям отдельно; устройство 2 для хранения констант исправления, представляющее собой односторонние долговременные запоминающие устройства для каждого модуля; блок д, предназначенный для хранения констант; блок 4 вычисления неточното ранга числа при расширении с оонований Р иа ЯК 1 К, состоящий из сумматоров 5, 6 и схемы 7 анализа переноса цз старшего разряда, соединенные гираллельцо-последовательно между собой; блок 8 вычисления неточного ранга числа при расширении с оснований Я ца Р К К 2, состоящий из сумматоров 9, 10 и схемы 11 анализа переноса из старшего разряда, соединен 10 15 20 2,5 30 г 5 40 45 50 55 00 05 цые последовательно-,параллельно, между со. бой; сумматоры 12, И по контрольным основаниям, предназначенные для суммирования кон-станг при расширении с Р. на ЯК 1 К, поступающих из устройства 2 и блока 4; сумматоры 14, 16 по контрольным основаниям, предназначенные для суммирования констант при расширении с Я на РцК 1 Кг, поступа. ющих из устройства 2 и блока 8; блок 16 констант исправления, предоставляющий собой долговременное запоминающее устройство констант исправления, проверяемого числа х; блок анализа 17 на нуль разности цифр по контрольным основаниям при расширении с ьРна ЯК 1 К и цифр по,контрольным осцованиям при,расширении с Я на ;Р К,К, предназначенный для выработки сигнала наличия или отсутствия ошибки в проверяемом числе. Код проверяемого числа х по шинам принимается ца входной регистр 1. Выходные сигна. лы,регистра подаются на входы блошка 3 хранения констант. Адресом для обращения в блок констант служит код вычетазаписанный на входной регист 1 р по соответствующему основанию, С выходов блока Л хранения констант коды вычетов по контрольным основаниям поступают на входы сумматоров,12, 13, 14, 15, а коды констант, предцазначенные для вычисления неточных рангов числапоступают на входы,сумматоров б, б и 9, 10 блоков 4 и 8.Сумматоры 6, б и 9, 10 представляют собой п одноразрядных сумматоров.Вырабатываемые в каждом, разряде сумматора сумма и перенос поступают в качестве одного из слагаемых одноименного и следующего соответственно, разряда последующих сумматоров. Ситналы переноса, выра(батываемые в старших разрядах сумматоров 6, б и 9, 10, а также сигнал с выхода схем 7, 11 ацализа переноса, подаютоя,на входы сумматоров по контрольным основаниям,12, И и 14, 16, так как эти сигналы являются составляющими неточного ранга числа х. Сумматоры 12, И и 14, Ы суммируют поступающие на их входы коды по соответствующим контрольным основаниям при расширении числа в ту и другую сторону. С выходов сумматоров по контрольным ос юваниям сигналы подаются на входы, блока 16 конста,нт нсправления и блока 17 анализа на нуль.Блох 17 анализа ца,нуль представляет собой логнчеокую схему сравнения кодов контроль. ных логических оснований, поступающих с выходов сумматоров 12 и 14, Ии 15.При равенстве попарно этих кодов ца выходе блока 17 выраоатываегся сигнал правильности проверяемого числа. В противном случае вырабатывается сигнал наличия ошибки. Оба эти сигнала ьыдают;.я в схем равления устройством контроля и исправления. На выходах блока 16 констант исправления вырабатывается код коррекции проверяемого числа х при наличии в нем ошибки. Адресом для обраще. ция в блок 16 констант исправления служит разцос 10 цьигетов ио контрольным основаниям,398950 сианпп си ьБьи од норрам ванеев оставите д 3, Тараненно 11 оректо 1 з А. Степанова едаитор Л. Струв1 зд.,4 1949 Тира;к 617 11 НИИПИ Государственного комитета Совета Мииистрои СС по делаги изобретевии и скрытий Москва, Ж, Раушская наб., д. -1,5акал 7072 дписиое трочского управления издательств, полигииии и книжной торговл Обл, тиг вырабатываемая на выходах сумматоров 12,13 и 14, 15. П редмет изобретен и яУстройство для обнаружения и исправления ошибок в системе остаточных классов, содержащее входной регистр, сумматоры по контрольным основаниям, выходы которых подключены ко входам блока анализа .на нуль остатка по контрольным основаниям и блока констант исправления, отлачаюцееся тем, что, с целью увеличения быстродействия, в него введены два блока вычисления неточного радцига числа, выходами подсоединенные к сумматорам 5 по контрольным основаниям, блок хранения констант исправлением, входами, подключенный к входному регистру, а выходами подключенный ко входам сумматоров по контрольным основаниям и входам блоков вычисления неточного 10 ранга.

СмотретьЗаявка

1626269

И. Я. Акушский, В. М. Амербаев, Ю. Л. Захаров, В. С. Кокорин

МПК / Метки

МПК: G06F 11/10

Метки: исправления, классов, обнаружения, остаточных, ошибок, системе

Опубликовано: 01.01.1973

Код ссылки

<a href="https://patents.su/3-398950-ustrojjstvo-dlya-obnaruzheniya-i-ispravleniya-oshibok-v-sisteme-ostatochnykh-klassov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения и исправления ошибок в системе остаточных классов</a>

Предыдущий патент: Устройство для округления числа в системе остаточных классов

Следующий патент: Устройство для контроля дешифратора

Случайный патент: Регулируемый стоп