Устройство логического управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 397890

Авторы: Вительнаучно, Технологический

Текст

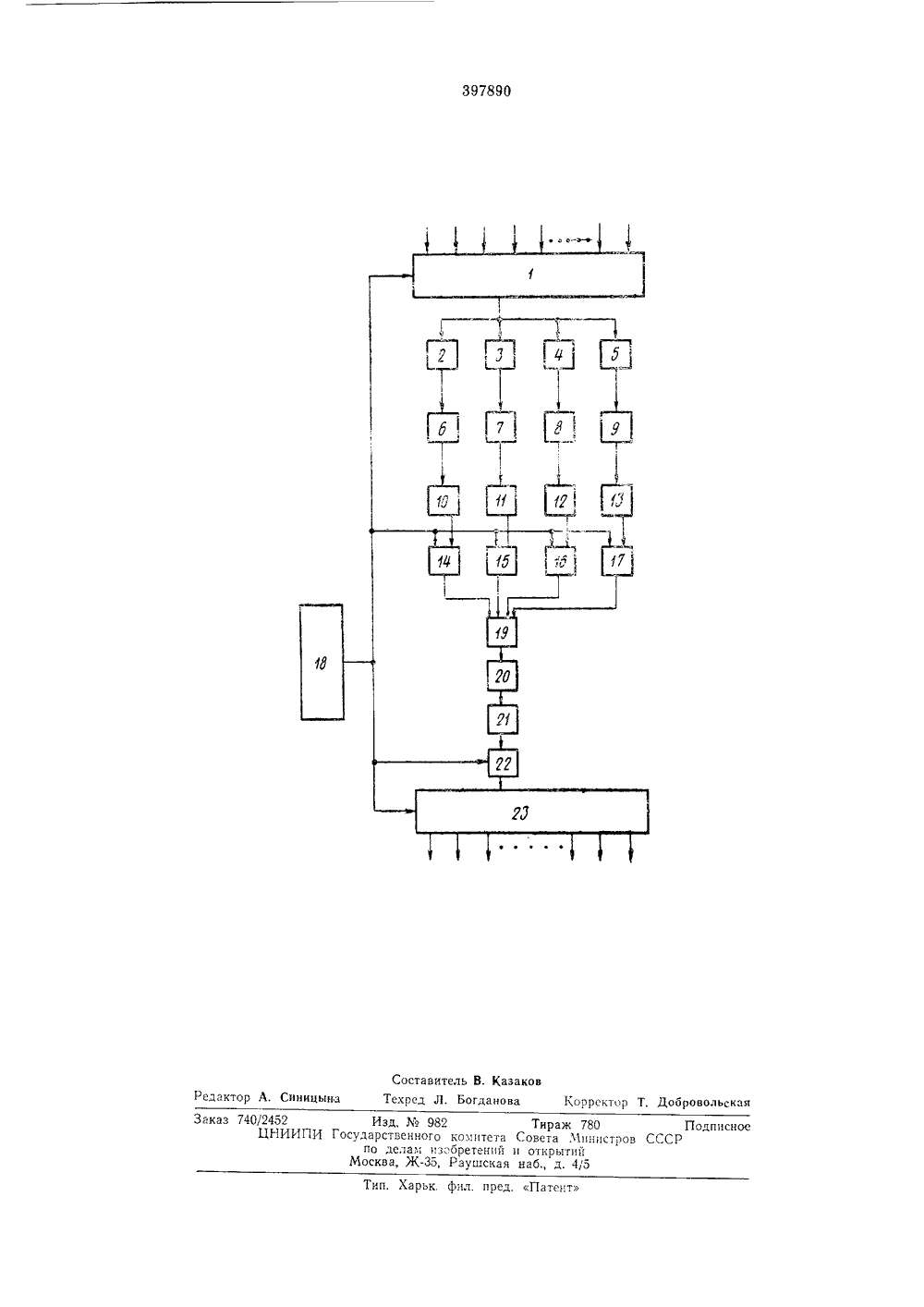

Союз Советскихо иалисти С м цеских РеспубликЗависимое от авт, свидетельства-Заявлено 10.111.1971 (,% 1633852/18-24)с присоединением заявки-М. Кл. б 05 Ь 19,Гасударственный комитет Совета Министров СССР по делам изобретений и открытийриоритет - публиковано ата опублик ДК 621.398,6,1 Х.1973, Бюллетень х:е 3ния описания 15.11.1974 Авторы зобретен В. В. Приблуда, В. П. Лужбин и А. Н, Косых ийвода 3 аявител роектно-констру мплексного алек УСТРОЙСТВО ЛОГИЧ ГО УПРАВЛЕНИ Устройство преднания в слстемах упрами механизмами. начено для использова ения производственны альлые ьн утатор кодных прямо, рас- лешиольную ммутаНаучно-исследовательскии технологический институт Известны устройства логического управле ния, содержащие прямоугольную матрицуусилители, входы которых подключены к выходам матрицы, а выходы - к исполнительным органам.Отличие описываемого устройства состоит 1 О в том, что оно содержит входной и выходной коммутаторы, дешифраторы, усилители входных сигналов матриц, дополнительные прямоугольные матрицы, ключи л распределитель тактовых импульсов, причем к выходам вход ного коммутатора подключены дешифраторы, выходы которых через усилители входных сигналов матриц соединены с вертикальными шинамл дополнительных прямоугольных матриц. Горизонталы ые шины этих матриц под. 20 соединены к сигнальным входам ключей, выходы которых соединены со входом одного из дешифраторов, а его выходы через усилители ,входных сигналов матриц подключены к вертикальным царицам прямоугольной матрицы.Горизонтальные шины этой матрицы через ключи подсоединены ко входу выходного коммутатора, а выход распределителя тактовых импульсов соединен с управляющими входами ключей и коммутаторов.30 Это гозволяет расширить функцио возможности устройства.На чертеже изображена функцио схема устройства.Устройство содержит входной ком 1, дешифраторы 2 - 5, усилители 6 - 9 сигналов матриц, дополнительные угольные матрицы 10 - 13, ключи 14 - пределитель тактовых импульсов 13, фратор 19, усилители 20, прямоу матрицу 21, ключи 22, выходной и тор 23 Все входные переменные поступают на коммутатор 1, выдающий на свои выходы в каждом такте работы устройства только те входные переменные, из которых состоит реа лизуемое уравнение, решаемое в данном такте. Выходы коммутатора. группами по четы. ре или месе, подключены и децшфраторам 2 - 5. На одной из выходных шич каждого дешифратора появляются сигналы, соответствующие комбинациям состояния входных переменных. Эти сигналы через усилители 6 - 9 подсоединены к вертикальным шинам матриц 10 - 13.Алгоритмы решенгий уравнений задаются соединением вертикальных шин матриц 10 - 13 с горизонтальнымл ш:.шами посредством диодов, напаянных з соответствии с десятичными эквивалентами нужных комоинаций вход 39789010 20 25 30 35 40 ных переменных. Эти эквиваленты получаютна,выходах дешифраторов 2 - 5, т. е. нужныедесятичные эквиваленты объединены по схемам ИЛИ, выходы которых (горизонтальные шины матриц) подсоединены к соответствующим ключам 14 - 17.На ключах И 17 реализованы логическиефункции И, входами которых являются сигналы тактов от распределителя 18,и сигналыс горизонтальных шин матриц 10 - 13.Выходы каждой группы ключей объединены вместе, благодаря чему реализуется логическая функция ИЛИ, образующая четырепромежуточные переменные для следующегоэтапа решения логических уравнений - методом суперпозиции этих промежуточньх переменных.Промежуточные переменные поступают навход дешифратора 19. На одной из выходныхшин его появляется сигнал, соответствуюшийкомбинации состояний промежуточных пере.менных. Сигналы с дешифратора через усили"тели 20 подаются на вертикальные шины мат.рицы 21. На матрице 21 посредством диодов,напаянных в соответствии с десятичнымиэквивалентами нужных комбинаций состоянийпромежуточных переменных, задаются ал. оритмы решений уравнений, Ее горизонтальные шины подсоединены к ключам 22, на котор ые подаются сигналы соответствующихтактов,от распределителя 18,Результаты решений уравнений с объединенного выхода ключей 22 идут на выходнойкоммутатор 23, состоящий,из триггеров с управляемыми входами, на цепи управлениякоторых поступают сигналы результатов решений, а на цепи запуска - сигналы тактовот распределителя 18.На выходе триггера, соответствующегоданному решаемому уравнению, сигнал 1сохраняемся до тех пор, пока по цепи управ.ления поступают подтверждающие импульсы(результаты решения уравнения, принимающие значение 1),Подтверждающие импульсы несут инфор. мацию о том, что комбинация состояний входных переменных соответствует заданному алгоритму решения данного уравнения. Если состояния входных переменных не со. ответствуют алгоритму решения уравнения, подтверждающие импульсы отсутствуют, и на выходе соответствующего триггера появляется сигнал 0.Работа всего устройства синхронизируется выходными тактами распределителя 18, т. е. в каждом данном такте комбинационная часть устройства отведена для уравнения, решаемого в данном такте. Предмет изобретения Устройство логического управления, содер жащее прямоугольную матрицу и усилители, входы которых подключены квыходам матрицы, а выходы - к исполнительным органам, отличающееся тем, что, с целью расширения функциональных возможностей, оно содержит входной и выходной коммутаторы, дешифраторы, усилители входных сигналов матриц, дополнительные прямоугольные матрицы, ключи,и распределитель тактовых импульсов, причем к выходам входного коммутатора под. ключены дешифраторы, выходы которы, через усилители входных сигналов матриц соединены с вертикальными шинами дополнительных прямоугольных матриц, горизонтальные шины этих матриц подсоединены к сигнальным входам ключей, выходы которых соединены со входом одного из дешифраторов, а его выходы через усилители входных сигналов матриц подключены к вертикальным шинам прямоугольной матрицы, горизонтальные шины этой матрицы через ключи подсоединены ко входу выходного коммутатора, а выход распределителя тактовых, импульсов соединен с управляющими входами ключей и коммутаторов.,б Г 7 Составитель В. КазаковТехред Л. Богданова Корректор Т, Добровольская Редактор А. Синицына Заказ 7402452 Изд, М 982 Тираж 780 Подписное ЦНИИПИ Государственного комитета Совета Министпов СССР по делам нзооретеннй и открытий Москва, Ж, Раушская наб., д. 4/5

СмотретьЗаявка

1633852

вительНаучно исследовательский проектно конструкторский, технологический институт комплексного электропривода

МПК / Метки

МПК: G05B 19/08

Метки: логического

Опубликовано: 01.01.1973

Код ссылки

<a href="https://patents.su/3-397890-ustrojjstvo-logicheskogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство логического управления</a>

Предыдущий патент: Способ адаптации интервала квантования в дискретных экстремальных регуляторах с постоянной длиной шага

Следующий патент: 397891

Случайный патент: Способ охлаждения ротационного компрессора и ротационный компрессор с катящимся ротором