Цифро-аналоговое вычислительное управляющее

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 386409

Автор: Авторы

Текст

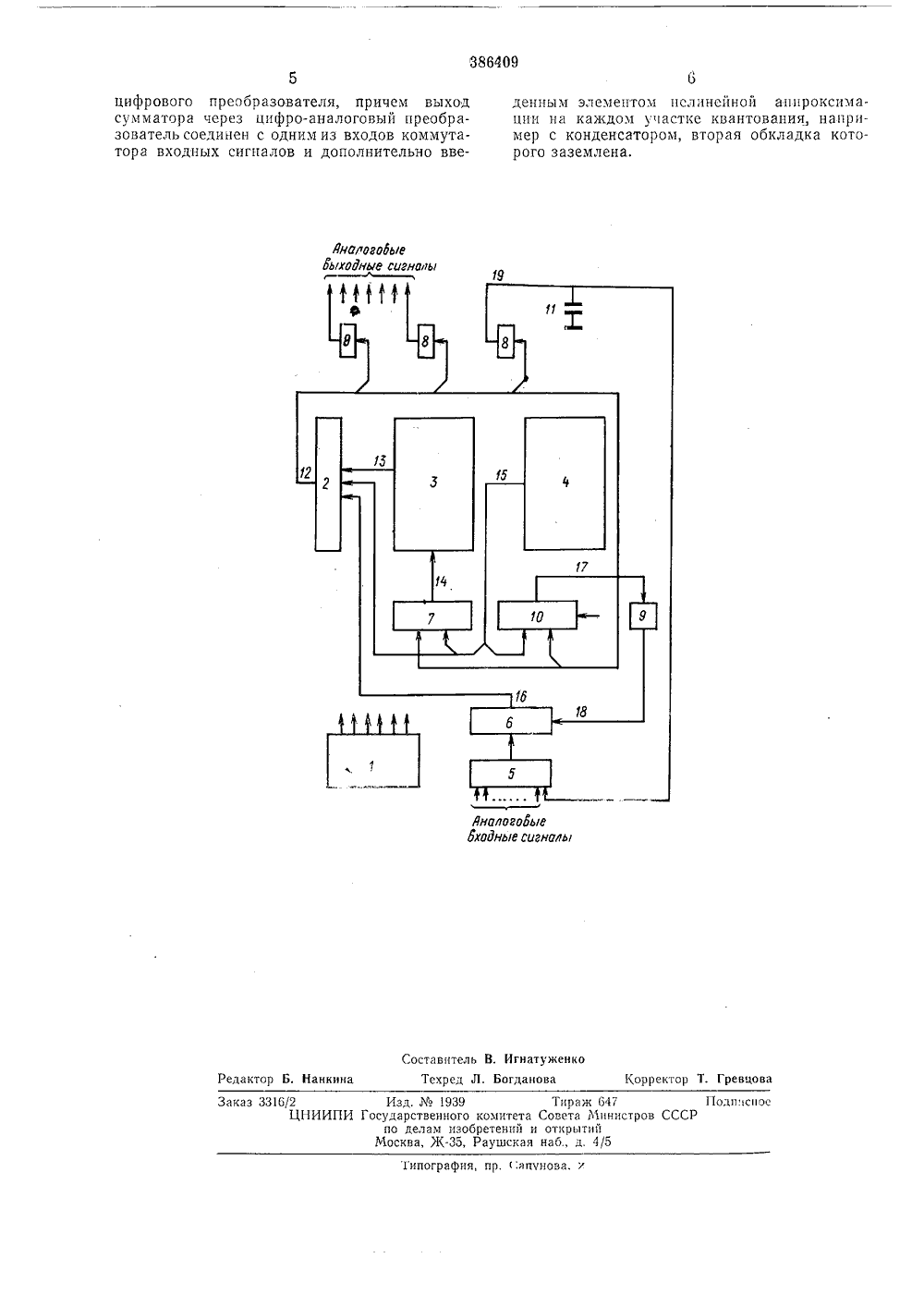

64 Союз СоветскихоциалистицескихРеспублик ОБРЕТЕН И ВТОРСКОМУ СВИДЕТЕЛЬСТ ависимое от авт. с аявлено 10. Ч,1970 детельства К Ло 142,3337/18 61 1/О исоединением заявкиосударственный комитетСовета Министров СССРпо делам изооретенийи открытий риоритет Опубликовано 14.Ч 1.1973. БюллетеньДата опубликования описания 18.Х 11.197 УДК 681.,34(088 Авторыизобретения Н, Малиновский, А. В. Палагин и А. Ф. КургаевИнститут кибернетики АН Украинской ССР Заявител ФРО-АНАЛОГОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УПРАВЛЯЮ УСТРОЙСТВОюча- ъем Изобретение относится к области вычислительной техники.Известны цифро-аналоговые вычислительные управляющие устройства, содержащие блок пассивной памяти с подключенным к нему счетчиком-регистром значений аргумента, схему совпадений, блок оперативной памяти и сумматор, выход которого соединен со входами блока оперативной памяти и счетчика-регистра значений аргумента, а входы подключены через аналого-цифровой преобразователь к коммутатору входных сигналов и выходам блоков пассивной и оперативной памяти.Недостаток известных устройств закл ется в том, что они имеют большой об оборудования блока пассивной памяти,Предложенное устройство отличается тем, что оно содержит счетчик-регистр приращений значений аргумента, входы которого соединены с выходами сумматора и блока оперативной памяти, а выходы через схему совпадений подключены к управляющему входу аналого-цифрового преобразователя, причем выход сумматора через цифро-аналоговый преобразователь соединен с одним из входов коммутатора входных сигналов и дополнительно введенным элементом нелинейной аппроксимации на каждом участке квантования,например с конденсатором, вторая обкладка которого заземлена.Это позволило сократить требуемый объем пассивной памяти,На чертеже приведена схема предлагаемого устройства.Оно содержит блок управления 1, сумматор 2, блок 8 пассивной памяти, блок 4 оперативной памяти, коммутатор 5 аналоговых входных сигналов, аналого-цифровой преобразователь б, счетчик-регистр 7 грубых значений аргумента, цифро-аналоговые преобразователи 8, схему совпадений 9, счетчик-регистр 10 приращений аргумента, конденсатор 11; цифрами 12 - 19 обозначены основные связи, соединяющие соответствующие блоки устройства.Работа устройства состоит в следующем.Блок управления 1 вырабатывает последовательность сигналов, управляющих работой всех остальных блоков и узлов устройства. Аналоговые входные сигналы, поступающие через коммутатор 5 на вход аналого-цифрового преобразователя б, преобразуются в нем в цифровую форму и затем подаются на сумматор 2. Затем осуществляется обработка поступивших входных сигналов в соответствии с заданным алгоритмом и рассчитанные величины регулирующих воздействий поступают на входы цифро-аналоговых преобразователей 8, выходы которых соединены непосредственно3со входами исполнительных устройств. Операции типа сложения, вычитания и другие осуществляются в сумматоре 2. Сложные операции типа умнояения, деления, а также вычисления функций вида у=1(х) (например, у=з 1 пх, у=1 одх, е,хф и др.) осуществляются путем цифро-аналогового моделирования в соответствии с формулой:у -(х)(х ) +(ох),где (б, х) - функция, пропорциональнаявеличине приращения аргумента бх. При этом поведение функции ча участкеквантования Лх (от хо до хо+1) моделируется во времени зарядом (разрядом) конденсатора 11, на который подается напряжение с выхода цифро-аналогового преобразователя 8, пропорциональное приращению искомой функции на рассматриваемом участке квантованияЛ = (х,+1) - (х).Коэффициент преобразования шага квантования аргумента Лх во времени осуществляется изменением частоты импульсов, подаваемых на вход счетчика-регистра 10 приращений аргумента. Частота устанавливается при настройке устройства (генератор импульсов на чертеже не показан).При моделировании различных функций для повышения точности моделирования могут использоваться различные участки кривой заряда (разряда) конденсатора 11. Для выполнения указанных выше операций и вычисления функций в блоке пассивной памяти имеется три таблицы грубых значений функций - логарифмов (хо) =1 оо хо, антилогарифмов(хо) =апИ (1 од хо) и синусов(хо) = =Йп х,.Перед началом вычислений код аргумента х=.хо+бх, представленный грубым значением хо и приращением бх (соответственно старшие и - т разрядов и младшие т разрядов аргумента) подаются на входы счетчиков-регистров 7 и 10 соответственно, Код счетчика- регистра 7 представляет собой адрес ячейки блока 8, где хранится величина (хо), например 1 од хо, которая считывается и подается на сумматор 2. Затем код счетчика-регистра 7 увеличивается на единицу младшего разряда и из блока 8 пассивной памяти на сумматор 2 поступает величина,(хо+1) (например, 1 оо(хо+1), В сумматоре 2 вычисляется разность этих величин, т. е. определяется значение М=Р(хо+1) - Г(хо), которое подается на вход одного из цифро-аналоговых преобразователей 8 (на чертеже расположен справа вверху), который в исходном состоянии очищен. На выходе цифро-аналогового преобразователя 8 устанавливается напряжение, пропорциональное величине Л. При этом начинается заряд конденсатора 11 и одновременно вычитание по единице из счетчика-регистра 10, в котором находилась величина бх.386409 В момент очистки счетчика-регистра 10, который фиксируется схемой совпадений 9, аналого-цифровой преобразователь б измеряет значение напряжения на конденсаторе 11, которое на период измерения для уменьшения динамической погрешности может фиксироваться аналоговым фиксатором (на чертеже не показан). Таким образом, определяется значение функции (бх). Величина (бх) с выхода преобразователя б подается на вход сумматора 2, где вычисляется значение 1(х) =1(хо)+(бх)Умножение и деление осуществляются с помощью таблиц логарифмов путем отыскания логарифмов исходных величин (а, в), Затема определяется величина 1 од(аХв) или 1 од - ив 5 10 15антилогарифмирование описанным выше способом, за исключением того, что измерение значения (бх) осуществляется при разрядке конденсатора 11. Для этого после подачи величины Л на вход преобразователя 10 происходит его очистка и начинается разряд конденсатора 11,Как видно из описания работы схемы, погрешность вычислений лишь незначительно зависит от погрешности аналоговой части вычислителя. Для получения погрешности, рав.ной единице младшего разряда при представлении аргументов и функций 14-ю двоичными разрядами, достаточно иметь в блоке пассивной памяти таблицу 100 значений логарифмов (столько же значений антилогарифмов), Для вычисления функпни у=з 1 пх оказывается также достаточным иметь 100 грубых ее значений при той яе точности вычислений. При этом для получения указанной погрешности 2 в 4 требуется обеспечить относительную погрешность (в сумме) аналогоцифрового и цифро-аналогового преобразователей не более 2 -от полной шкалы, что легко достигается. 20 25 30 35 40 45 Предмет изобретения 50 55 60 65 Цифро-аналоговое вычислительное управляющее устройство, содержащее блок пассивной памяти с подключенным к нему счетчиком-регистром значений аргумента, схему совпадений, блок оперативной памяти и сумматор, выход которого соединен со входами блока оперативной памяти и счетчика-регистра значений аргумечта, а входы ,подключены через аналого-цифровой преобразователь к коммутатору входных сигналов и выходам блоков пассивной и оперативной памяти, отличаюи 1 ееся тем, что, с целью сокращения требуемого объема пассивной памяти, оно содержит счетчик-регистр приращений значений аргумента, входы которого соединены с выходами сумматора и блока оперативной памяти, а выходы через схему совпадений подключены к управляющему входу аналого386409 йнаогоБыеВыходные сигнооы 19 ВнппогогыиВходные сигналы Составитель В. Игнатуженко Техред Л. БогдановаРедактор Б. Ианкина Корректор Т. Гревдова Заказ 33162 Изд. Мз 1939 Тираж 647 Поди.1 спос ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий Москва, Ж, Раушская наб., д. 4/5Типография, пр. (:апунова. и цифрового преобразователя, причем выход сумматора через цифро-аналоговый преобразователь соединен с одним из входов коммутатора входных сигналов и дополнительно введенным элементом нелинейной аппроксимации на каждом участке квантования, например с конденсатором, вторая обкладка которого заземлена,

СмотретьЗаявка

1423337

Б. Н. Малиновский, А. В. Палагин, А. Ф. Кургаев Институт кибернетики Украинской ССР

Авторы изобретени

МПК / Метки

МПК: G06J 1/00

Метки: вычислительное, управляющее, цифро-аналоговое

Опубликовано: 01.01.1973

Код ссылки

<a href="https://patents.su/3-386409-cifro-analogovoe-vychislitelnoe-upravlyayushhee.html" target="_blank" rel="follow" title="База патентов СССР">Цифро-аналоговое вычислительное управляющее</a>

Предыдущий патент: Устройство для моделирования стержневых рам

Следующий патент: Универсальный числовой функциональный

Случайный патент: Подвесная канатная дорога