Аналого-дискретный сумматор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

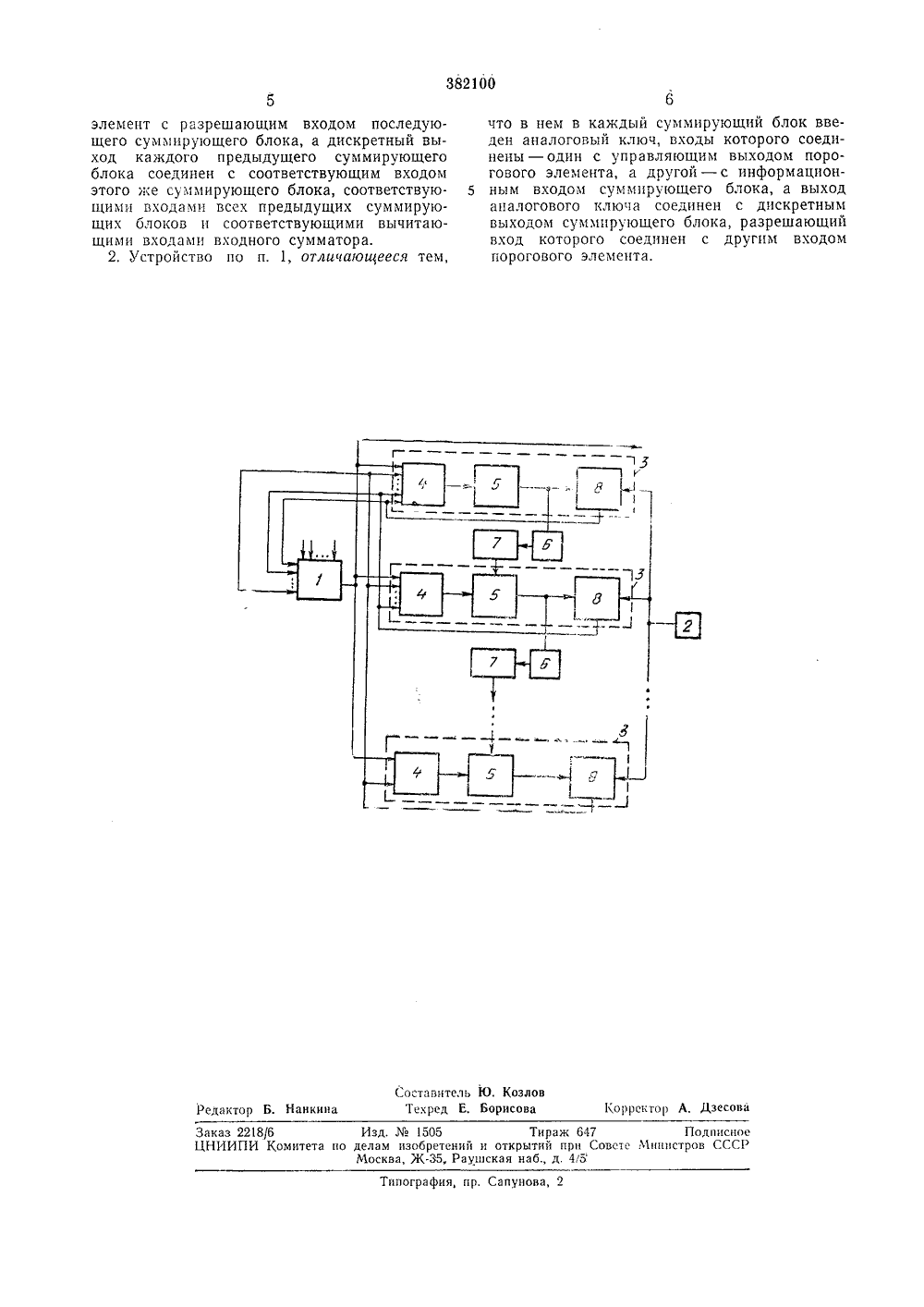

ОП ИСАНИЕ ИЗОБРЕТЕН Ия К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ3821 ОО Союз Соеетскид Соаиалистических(ф 4 Й 3,Зависимое от авт. свидетельства Мо М, Кл, 6 06 д 7/14 аявлено 06.1 Х,1971 (5 чое 1693297118-24 рисоединеиием заявк риоритет комитет по дедам обретении и открытийри Совете тйннистровСССР Опубликовано 22.7.1973 УДК 681.325.54(088.8) юллетень Уе 22 Дата опубликования описания 24 Х 111.1973 Авторыизобретения П. Базаров, А Долгов, Л. М. Маркович, Ю. Г, Раутиан, ищенко и М, Д, Штерк Заявитель ЛОГО-ДИСКРЕТНЫЙ СУММАТОР Изобретение относится к области вычислительной техники.Известны аналого-дискретные сумматоры, содержащие входной сумматор, источник эталонного сигнала, суммирующий блок, выполненный на аналоговом сумматоре, соединенном с пороговым элементом, цепи задержки и коммутирующие элементы.Предложенное устройство отличается от известных тем, что оно содержит ряд сумъирующих блоков, основные входы которых соединены с выходом входного сумматора, а информационные входы подключены к выходу источника эталонных сигналов, причем управля 1 ощий вход предыдущего суммирующего блока соединен через последовательно включенные цепь задер)кки и коммутирующий элемент с разрешающим входом последующего суммирующего блока, а дискретный выход любого предыдущего суммирующего блока соединен с соответствующим входом этого )ке суммирующего блока, с соответствующими входами всех предыдущих суммирующих блоков и соответствующими вычитающими входами входного аналогового сумматора.Кроме того, в каждый суммирующий блок введен аналоговый ключ, входы которого соединены - один с управляющим выходом порогового элемента, а другой - с ицрормациоиным входом суммирующего блока, а выход аналогового ключа соединен с дискретнымвыходом суммирующего блока, разрешающийвход которого соединен с друпм входомпорогового элемента.Это позволило увеличить суммарный уровень входного сигнала и расширить областьприменения устройства,Блок-схема предлагаемого сумматора приведена на чертеже.0 Устройство содержит входной сумматор 1,источник 2 эталонного сигнала, суммирующийблок 3, выполненный иа аналоговом сумматоре 4, соединенном с пороговым элементом б,цепи задер 1 ски б и комътируОщие элементы 7, причем в каждый суммирующий блок 1введен аналоговый кл 1 оч 8.В устройстве входные, выходнь)е и ироме.жуточиыс дискретные величины представляются уровнями (фиксироваиньми знячсниям 110 некоторого параметра) аналогового сигналятак, что целочисленному зиячешпо величины 1,соответствует уровень сигналаУ,=ЛС 1:,25 где Л 1, - величина разнося соседних уровней. Аналого-дискретный сумматор реализует получение результата у =- суммирования 1 дискретных слагаемых (а; ) О, где = - 1,2.1)382100 С. =- "У - И/сгг. с3по избранному модулю сгга ( т , то естьоперацию с,ас = Еас - Й сс,- сссгде /с определяется пз соотношенияО - ссс - Илг (и,или, применительно к принятой аналоговой форме кодирования дискретных величин, - получение дискретного уровня выходного сигнала 1./ = 1.У,. - Ы/ас.Аналого-дискретный сумматор работает следующим образом.В исходном состоянии слагаемые ца входы входного сумматора 1 це поступают (суммаршгй входпой сигнал Х 1/., оказывается равсцым нулю), Вследствие чего ца входы аналоговых сумматоров 4 с выхода входного ацало- ГОВОГО СуМ М стора 1 И даЛЕЕ ца ВХОды П 011 ОГО вых элементов 5 также поступает сигнал, равцый нулю. Каждый пороговый элемент построен таким образом, что его выход возбукдается прц достижении и превышении сиилом ца входе порогового элемента уровпи Ьс ==- Л / сгг. 11 оэтому в исходном состоянии Выходы всех пороговых элементов 5 це Возбуждены, все аналоговые ключи 8 заперты по управляющему Входу, и с их выходов сигналы ца входы сусчматоров 1 и 4 не поступают. Один из пороговых элементов 5 (верхций ца чертеже) подготовлен к работе, Условия, разрешающие работу последующих пороговых элементов, могут возникнуть лишь при возбуждении выходов предыдущих пороговых элементов (для приведенного чертежа - начиная сверху) после некоторой задержки, определяемой цепью задержки б, в результате срабатывания коммутирующего элемента 7 (например, включающего напряжение, питающее соответствующий пороговый элемент 5). Гсли суммарный входной спгпгл Х(/с, (с:( г/с, ца Выходе устройства устанавливаетсясигнал суммы /= Х 1/ прц этом ци одинс. -пз пороговых элементов 5 це срабатывает. Гсли же суммарный входной сипсал сХ(/ ) с/ссс, причем (/г) с./,сс ( Х(/,. ( Н/пг, с: сто оц передается па входы ацалоговых сумматоров 4, и в устройстве начинается переходной режим, в процессе которого последовательно (по чертеку - начиная сверху) срабатывают пороговые элементы 5 (возбуждессие выхода предыдущего порогового элемента через пцтервал времени, определяемый цепью задержки 6, создает условия, разрешающие раооту последующего). При этом в соответствующей последовательности открываются аналоговые ключи 8 и эталонные сигналы с их 5 вьсходов поступают ца вычитающие входывходного сумматора 1. Время цепи задержки б выбирается таким образом, что к моменту срабатывания очередного 1-го порогового элемента 5 эталонные сигналы, поступающие 10 с выходов предыдущих аналоговых ключей 8,оказываются учтецпьсми, и на выходе входного сумматора 1 (и далее ца входе сгг-го порогового элемсцта 5) устанавливается промежуточцос значение сигнала:15,1/с - (/ - 1) с.l сп.сПадение уровня сигнала ца выходе вход ного сумматора 1 не приводит, однако, к измсцецссю входных сигналов предыдущих пороговых элемецтов 5, так как компенсируется соответствующим возрастанием уровней сигналов на входах аналоговых сумматоров 4, 25 связанных с выходамп аналоговых ключей 8,открытых предыдущими сюроговыми элемец 5 После окончания переходного режима сумЗ 0 марцый сигнал, подаваемый ца вычитающиевходы входного сумматора 1 с выходов ацалогоьых ключей 8, оказывается равным Й 1/сгг, в результате чего ца выходе устройства устанавливается результат:35 При этом (/г+1)-й пороговый элемент Б 40 оказывается подготовленным к работе, однаковходной сигцал / ( т, поступающий через соответствующий ацалоговый сумматор 4, це приводит к его срабатыванию, а также к срабатсссванисо всех послеДУюЩих поРоговых4 элсмсцгов 5 П ре/м ет изобретения 50 1. Аналого-дискретпссй сумматор, содержащий входной сумматор, источник эталонного сигнала, суммирующий блок, выполненный ца аналоговом сумматоре, соединенном с пороговым элементом, цепи задержки и коммути рующие элементы, отлссссасогчийся тем, что,с целью увеличения суммарного уровня входного сигнала и расширения области применения устройства, опо содержит ряд суммирующих блокосз, основные входы которых соеди цепы с выходом входного сумматора, а информационные входы которых подключены к выходу источника эталонных сигналов, причем управляющий вход предыдущего суммирующего блока соединен через последовательно 65 включешсые цепь задержки и коммутирующийСоставитель Ю. КозловРедактор Б. Капкина Текред Е, Борисова Корректор А, Дзе Заказ 2218/6 Изд.1505 Тираж 647 ЦНИИПИ Комитета по делам изобретений и открытий при СМосква, ЖРаушская наб., д. 45 Поди иссте Министров ССС ппография, пр. Сапунова элемент с разрешающим входом последующего суммирующего блока, а дискретный выход каждого предыдущего суммирующего блока соединен с соответствующим входом этого же суммирующего блока, соответствую. щими входами всех предыдущих суммирующих блоков и соответствующими вычитающими входами входного сумматора.2, Устройство по п. 1, отличающееся тем,6что в нем в каждый суммирующий блок введен аналоговый ключ, входы которого соединены - один с управляющим выходом порогового элемента, а другой - с информацион ным входом суммирующего блока, а выходаналогового ключа соединен с дискретным выходом суммирующего блока, разрешающий вход которого соединен с друг 11 м входом порогового элемента.

СмотретьЗаявка

1693297

Н. П. Базаров, А. И. Долгов, Л. М. Маркович, Ю. Г. Раутиан, А. М. Тишенко, М. Д. Штерк

МПК / Метки

МПК: G06G 7/14

Метки: аналого-дискретный, сумматор

Опубликовано: 01.01.1973

Код ссылки

<a href="https://patents.su/3-382100-analogo-diskretnyjj-summator.html" target="_blank" rel="follow" title="База патентов СССР">Аналого-дискретный сумматор</a>

Предыдущий патент: Электромеханический сумматор углов поворота

Следующий патент: Множительное устройство

Случайный патент: Устройство для разгрузки контейнеров