Запоминающее устройство для аналоговыхсигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 236098

Авторы: Беломлинский, Ленинградский, Сидоров

Текст

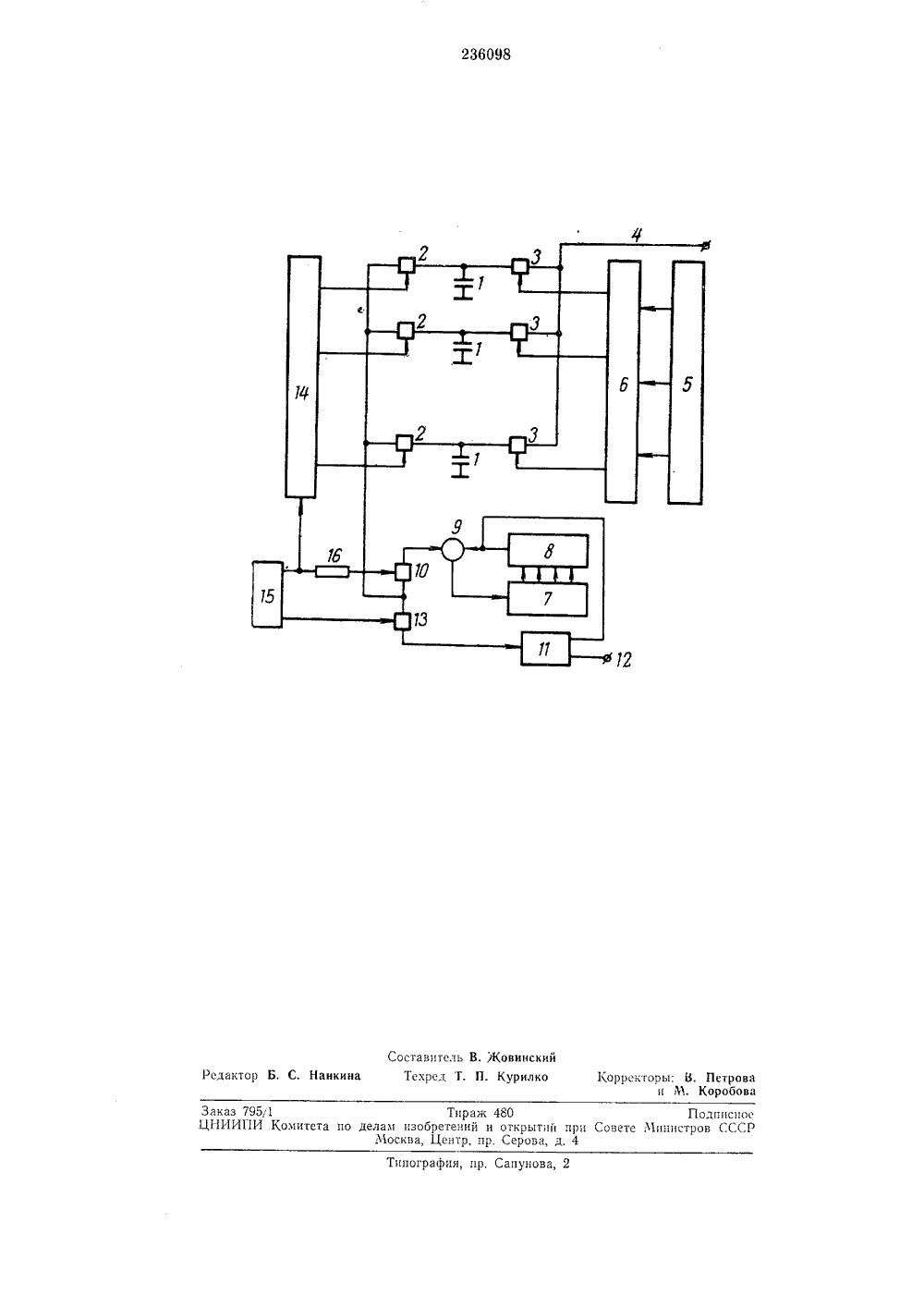

0 П И С А Н И Е 236098 Союз Советских Социалистических Республик.1 ПК 6 06 ах;.(К 681.337(088.8 Номитет по аелатлобретений и открытийри Совете МинистровСССР Опубликовано 24,1,19 ллетень Л та опубликования описания 25 Х 1,1969 ЕР" ч 1 йТ, .1. Беломлинский и В. М. Сидороврадский электротехнический институтим, В, И. Ульянова (Ленина) Заявитель ни ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ДЛЯ АНАЛОГОВЫХ СИГНАЛОВ2 Известны запоминающие устроиства для аналоговых сигналов, содержащие накопительные конденсаторы, входные ключевые схемы, ключевые схемы коррекции, дискретную следящую систему коррекции с последовательным опросом накопительных конденсаторов, олок выбора адресов и аналогово-цифровой преобразователь со схемой сравнения, сумматором и декодирующей схемой.й предлагаемом устройстве система коррекции содержит дополнительный входной ключ, связанный с одним из входов схемы сравнения, выход которой соединен с ее вторым входом через блок подбора цифрового эквивалента, и декодирующую схему, подключенную и одному из входов сумматора. Второй вход сумматора соединен с источником постоянного напряжения. Через выходной ключ сумматор связан параллельно с ключевыми схемами коррекции, управляющие, входы которых соединены с распределителем.Это упрощает устройство.На чертеже показана блок-схема описываемого устройства.Элементы памяти включают накопительные конденсаторы 1, ключевые схемы коррекции 2, ключи 3 записи-считывания, соединяющие конденсаторы 1 с шиной 4 записи-считывания,Блок выбора адреса состоит из регистра адреса 5, соединенного с дешифратором адреса 6, который управляет ключамп д записи-считывания соответствующих элементов памяти.Дискретная следящая схема коррекции содержит аналогово-цифровоп преооразователь, 5 состоящий из блокаподоора цифрового эквивалента, дскодпрующеи схемыи схемы сравнения 9, один пз входоь которои через дополнительный входнои ключ 1 ь схемы коррексоедпнен с ключевыми схемамп коррек цпи 2, а другой - с декодпрующей схемой.Напряжением на декодпрующей схеме 8 управляет блок 7 подбора цифрового эквивалента, соединенный с выходом схемы сравнения 9. 1-1 а один вход сумматора 11 по шине 12 по 1 б дается постоянное напряжение, равное половине шага квантования преобразователя, а другой вход соединен с выходом декодпрующей схемы 8, причем выход сумматора через выходной ключ 13 подключен к ключам ор рекцпи 2. Выходные цепи распределителя 14управляют ключами коррекции . Один из выходов задающего генератора 15 соединен с распределителем 11 и через лшппо задержки 16 - с входным ключом 10, а другой выход 5 управляет работой выходного ключа 13.При работе запоапшающего у стройства следует различать режимы записи, считывания и коррекции хранимой информации.В режпме записи записываемое напряжение 30 подается на шину 4 записи-считывания; одноЯреСИНО дсппфс)яТОр ядреея 6 БЫр 303 ТЫВСТ СИГИ), ОКРЫБс 1 ОЩИЙ КЛ 101 ) ЗсПИГИ-ОЧИЬвс э,с)сита памяи, соогвстстьуОпего адрссм, и;)сдваритсльио занессииом 5 в регистр адрес 5, и коидчсагор 1 этого э,емсгга памяи зар 5 жяется до иаир 51 ксии 5 равиого вхо;- 1 Ь).В рсИС СИТЛБяцп 51 Зс 1 ПОЫИН 1 ЮцСС уСТ- ройстио работасг аналогиио,: По иишс за иси-Г Ить Ви 1 сии)яетс 5 и аир 5 жсиис, соот- БСГСБ 1 ОИСС Исп 1 РЯЖСИИЮ Иа ОИДСИГЯОРС БьО)НОГО э,смста памяти.В режиме оррсци оидсисяторы 1 элс.СИТ)Б И а)5 ТИ ИОО 1 ЕРЕДИО ПОД)11013101 С 5 и ссс Оррекиии. Коррскци 5 зар 5 Дя каждоО 0 1)дс чьи ОГО коидеисяторя 0 уиествл 5 ется Б два эт;па: период отрабоки и период кор- РС КЩИ.11 сриод отработки на:ишается после того, я 0 Срсди 011 коидснсатор 1 элсментс пя)15 ти с;110 юсется . распределителем 14 к схеме оррсии. При этом через ре)ш, определяссс,1 Н 1 исЙ зядерКки 16, Отрьвастс 1 Бходиой лю 10 схемы корреиши, и иаир)сиие коррскирусч)10 одсисяОра 1 поступает на Вход схемь Граьчсипя 9. Вхо Ной ключ 1:) Б Этцг ЧОЧСи ЗсКРЬГ, ПОСКОЛЬКУ СИГНаЛЫ Иа ВЫ- хоН 1 х и 1 ии ск зс 13 ощсГО Гсисрс 1 Оря 15 сдВИ- н)ты Бо врсмсии. Схема срависигя 9 выраба Б Я ет с 1 Гн Я л, У и 0 Я В л 51 10 щ 1 й 0 л ОКО ъ 7 и Од 0 о- )3 ДпфРОВОГО ЭКВИБЯЛСИТс) ДО ТСХ ПОР, ПОс 1 иапрясиие иа выходе дскодирующей схемы 8 Я 13 ЛОГОБО-ии фРОБОГО 1. РСООР Язов атсл 51 1 с стаист ряг:1 ь 1 5 Бходио)1) . 1 эеким раооты преобразователя выбирается таким образом, что ияир 5 жсиис ия щоидеисяторс 1 иоддсрживяс)- с 5 Систс)10 Й коррекции с ИОГрсии Ость 0, ие ИРЕБЫШЯЮЩСй ПОЛОВИНУ ИИТСРБЯЛЯ БпТОБс- ИИ 51,В период коррекции Открь 1)сстс 51 Гю 15КГ 1 юч 1 закрываетс 51), и и Яир 5 Кение с Выхор, 11 ос, "; сствуОций эле)сит памяти. 1 СОДеисатор 1 при этом ЗсР 5 ЖЯЕ 1 СЯ ДО НЯ 1 Р 5 КСНИ 51 РЯВИО 0 БЬХОДИО..1 иир 5 с 1 ю с )1 ыаторя 11.Г 1 ериод подключения кондссаторов 1 к схс)С ОРРСКЦИ ВЫОИРЯЕТС 51 ТаИ. ООРЯЗО)1, 1 ТО- б:. за Бремя подключенпи конденсатор нс из )сиил сгоего заряда иа Бслисшну, больноюИ)ловиы шага кваптования.Таким образом, информация, записшиа Бзапоминающем устройстве, непрерывио иоддержиВяется )екду Опредслеииы)1 и дискрст .ыми уровнями и может хранитьс неограииСНБО дОЛГОС ЗрЕся. 11 редмет изобретенияЗапоминаощее устройство для аалоговыхСИГИ с 1:10 В, С ОДЕРК ЯЩЕЕ И Я КОПИТЕ.1 Ы 111 С КОИДЕИ - СЯТО)Ы ВХОДЧЫЕ КГИО 1 ЕБЬ 1 Е СХЕМЬ, ЛосЕБЬС схсчы коррекции, дискретную слсд 5 щуо систем) Оррекции с пос,едовятел.иым опросом 1;акопительиых конденсаторов, блок выбо;)а 2 з алресов и аналогово-иифровои прсобразов- ель со схемой сравнения, сумматором и дсСДИРУЮЩЕй СХЕМОЙ, ОТЛисаваЕЕСс тСЧ, Чта, с цслью его упрощения, сстема коррекши содержит доио;нтельный БКОДИОЙ .1 оч, свя- .О знный с одни) из входов схсчы сравнения,Выход которой соединен с ее Вторым входом через блок подбора цифрового эквивалента, и дсодируюшую схему, подключенную одно- )1 из Входов СУатОРЯ, ВТОРОЙ ьход котоРОО .5 соединен с источником постоиного напряя;с 1 Ия, сумчатор через выходной кгиоч связан царяллелыО с ключеВы)и схс)13 чи ко) рекции, управляющие входы которых соединены с распределителем.Составитель В. Жовинский Редактор Б. С. Наикииа Тсхрсд Т. П. Курилко Корректоры: В. Петрова и М. Коробова Заказ 795,1 Тираж 480 ПодписноеЦНИИПИ Комитета по делам изобретений и открытий прп Совете Министров ГССРМосква, Центр, пр, Серова, д. 4Типография, пр, Сапунова, 2

СмотретьЗаявка

1167888

В. Беломлинский, В. М. Сидоров, Ленинградский электротехнический институт В. И. Уль нова Ленина

МПК / Метки

МПК: G11C 27/00

Метки: аналоговыхсигналов, запоминающее

Опубликовано: 01.01.1969

Код ссылки

<a href="https://patents.su/3-236098-zapominayushhee-ustrojjstvo-dlya-analogovykhsignalov.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство для аналоговыхсигналов</a>

Предыдущий патент: Функциональный многооборотньш потенциометр

Следующий патент: 236099

Случайный патент: Винтовой питатель