Т-триггер на кмдп-структурах

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1261084

Авторы: Максимов, Петричкович, Филатов, Якушев

Текст

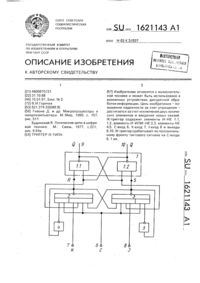

СООЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 84 А 1 4 Н 03 К 3/3ф,л ПИСА Я ВТОР ичков роэлекйств. с. 46 УКТУРАХк обласжет быть юай ЬФ Фиг. ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ ИЕ ИЗОБРЕ У СВИДЕТЕЛЬСТВУ(56) Букреев И.Н, и др, Миронные схемы цифровых устСов. радио, 1973, с. 167.Электроника, 1980, У 2рис. 3.(57) Изобретение относитсти импульсной техники, Мо использовано при разработке цифровыхустройств. Цель изобретения - повышение надежности и быстродействия.В устройство, содержащее прямой иинверсный тактовые входы 1 и 2, Птриггеры 3, 4, каждый из которых содержит бистабильную ячейку на инверторах 5, 6 и 9, 10 соответственно, атакже транзисторы р-и п-типа 7, 8и 11, 12 соответственно, ддя достижения цели путем интенсификации процессов перезаряда межузловых емкостей введены новые связи, 1 з,п.ф-лы,2 ил.Изобретение относится к импульсной технике и может быть использовано при разработке различных цифровых устройств.Цель изобретения - повышение надежности и быстродействия путем интенсификации процессов перезаряда межузловых емкостей.На фиг,1 представлена схема предлагаемого Т-триггера; на фиг,2 - временные диаграммы работы Т-триггера.Т"триггер (фиг.1) содержит прямой и инверсный тактовые входы 1 и 2, первый и второй Э-триггеры 3 и 4. Первый Э-триггер 3 содержит первый и второй инверторы 5 и б, первый и второй Щ 3 П-транзисторы 7 и 8 р- и и-типа выход первого инвертора 5 подключен к входу второго инвертора б, выход которого подключен к входу первого инвертора 5 и к стокам первого и втдрого транзисторов 7 и 8 первого Э-триггера 3, истоки которых подключены соответственно к прямому 1 и инверсному 2 тактовым входам. Второй инвертор 6 первого П-триггера 3 включен между инверсным 2 и прямым 1 тактовыми входами, второй П-триггер 4 содержит первый и второй инверторы 9 и 10, первый и второй ИДП-транзис,торы 11 и 12 р- и и-типа, выход пер" вого инвертора 9 подключен к входу второго инвертора 10, включенного между прямым 1 и инверсным 2 тактовыми входами, выход которого подключен к входу первого инвертора 9 и к стокам первого и второго транзисторов 11 и 12, второго П-триггера 4, истоки которых подключены, соответственно к инверсному 2 и прямому 1 тактовым входам, а затворы - к выходу первого инвертора 5 первого П-триггера 3, выход второго инвертора 10 второго П-триггера 4 соединен с затворами первого и второго транзисторов 7 и 8 первого П-триггера 3.Т-триггер работает следующим образом.Предположим, что в начальном состоянии на прямом и инверсном тактовых входах 1 и 2 в . комбинация сигналов 01 (фиг.2, й, ), Э-триггер находится в состоянии хранения логического нуля (т.е. на ыходе первЬ- го инвертора 5 (Я ) - логический нуль а на входе - логическая.еди 9 ница), тогда логический нуль на выходе инвертора 5 открывает транзистор 11 р-типа и потенциал логической единицы с входа 2 устанавливает 5 бистабильную схему Э-триггера 4 внулевое состояние (т.е. на выходе инвертора 9 (Я ) - логический нуль, а на входе - логическая единица), логическая единица на входе инвертора 9 открывает транзистор 8 и-типа и потенциал логической единицы с инверсного тактового входа 2 ие препятствует хранению логического нуля в бистабильной схеме Э-триггера 3. При переключении прямого и инверсного тактовых входов 1 и 2 в состояние 10 (1 ) Э-триггер 3 переходит в режим установки единичного состояния, а Э-триггер 4 - в режим хранения логического нуля, логическая единица с входа инвертора 9 удерживает открытым транзистор 8и-типа и потенциал логического нуляс инверсного тактового входа 2 устанавливает Э-триггер 3 в единичноесостояние, логическая единица с выхода инвертора 5 открывает транзистор 12 и-типа и уровень логической единицы с прямого тактового входа 2 не З 0 препятствует хранению логическогонуля в П-триггере 4, При переключении прямого и инверсного тактовых входов в состояние 01 Гс ) П-триггер 4 переходит в режим установки единичного состояния, а П-триггер 3 в режим хранения единичного состояния, при этом уровень логической единицы, с выхода инвертора 5 К, )удерживает открытым транзистор 1240 и-типа и потенциал логического нуляс прямого тактового входа устанавливает Э-триггер 4 в единичное состоя"ние, логический нуль с входа инвертора 9 открывает транзистор 7 р-типа 45 и уровень логического нуля с прямого тактового входа 3 не препятствуетхранению логической единицы в Э-триггере 3При переключении прямого иинверсного тактовых входов 1 и 2 в 50 состояние "10" С .) Р-триггер 3 пе 4реходитв состояние установки в нулевое состояние, а П-триггер 4 в состояние хранения логической единицы,при этом уровень логического нуля 55 входа инвертора 9 удерживает открытым транзистор 7 р-типа и уровеньлогической единицы с прямого тактового входа 1 устанавливает П-триг/56Тираж 8ВНИИПИ Государствепо делам изобре 113035, Москва, Ж,6 Подного комитета СССРений и открытий.Раушская наб., д, 4 Заказ 5243 сн Проиэводственно-полиграфическое предприятие, г.ужгород, Проектная, 4; гер 3 в нулевое состояние, уровеньлогического нуля с выхода инвертора 5 открывает транзистор 11 р-типа и:уровень логического нуля с инверсно-.го тактового входа 2 не препятствует 5хранению логической единицы в 0-триггере 4. При переключении прямого иинверсного тактовых зходов 1 и 2 всостояние "01" (5) Т-триггер переходит в состояние, аналогичноесостоянию в момент времени 1,и цикл работы Т-тирггера. завершается.,Второй инвертор одной иэ биста бильных ячеек в любой фазе Т находится в режиме повторителя, однако это не приводит к нарушению работоспособности устройства по той причине, что инвертор, построенный на транзисто рах 7, 8 и 11, 12, в каждой соответствующей фазе сигнала Т подавляет действие повторителя. При этом поскольку соответствующее подавляющее действие осуществляется ИДП-транзис тором, находящимся в крутой области вольтамперной характеристики (малое сопротивление),а подавляемый ИДП- транзистор - в пологой (большое сопротивление), потенциал рассматривае- ЗО мого узла очевидно меньше половины напряжения питаниячто означает его логическую определенность (этого нельзя было бы утверждать только в случаях, когда это напряжение равно Е/2, либо его нельзя оценить) . 4 Формула изобретения,.1. Т-триггер на КИДП-структурах, содержащий прямой и инверсный тактовые входы, первый и второй 0-триггеры, каждый из которых содержит бистабильную ячейку на первом и втором инверторах, первый и второй ИДП-транзисторы противоположного.ти" па проводимости, выход второго инвер- тора бистабильной ячейки подключен к стокам первого и второго ИДП-тран.зисторов, о т л и ч а ю щ и й с я темчто, с целью повышения надежности и быстродействия, к прямому тактовому входу подключены истоки первого ИДП-транзистора первого Р- триггера и второго ИДП.-транзистора второго Р-триггера, а к.инверсному тактовому входу подключены истоки второго ИДП-транзистора первого Р- триггера и первого ИДП-транзистора . второго Р-триггера, затворы первого и второго ИДП-транзисторов первого 0-триггера подключены к выходу второго инвертора второго Р-триггера, а затворы первого и второго ИДП-транзисторов второго Э"триггера -к выходу первого инвертора первого .В -триггера.2. Т-триггер по п.1, о т л и - ч а ю щ и й.с я тем, что истоки первого и второго ЩП-транзисторов по крайней мере одного из 0-триггеров соединены с истоками МДП-транзисторов противоположного типа проводимости второго инвертора того же Р-триггера.

СмотретьЗаявка

3837961, 03.01.1985

ОРГАНИЗАЦИЯ ПЯ В-8466

МАКСИМОВ ВЛАДИМИР АЛЕКСЕЕВИЧ, ПЕТРИЧКОВИЧ ЯРОСЛАВ ЯРОСЛАВОВИЧ, ФИЛАТОВ ВАЛЕРИЙ НИКОЛАЕВИЧ, ЯКУШЕВ ИВАН ДМИТРИЕВИЧ

МПК / Метки

МПК: H03K 3/353

Метки: кмдп-структурах, т-триггер

Опубликовано: 30.09.1986

Код ссылки

<a href="https://patents.su/3-1261084-t-trigger-na-kmdp-strukturakh.html" target="_blank" rel="follow" title="База патентов СССР">Т-триггер на кмдп-структурах</a>

Предыдущий патент: Многостабильный триггер богдановича

Следующий патент: Д-триггер

Случайный патент: Безрельсовая камнерезная машина