Устройство для умножения -разрядных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

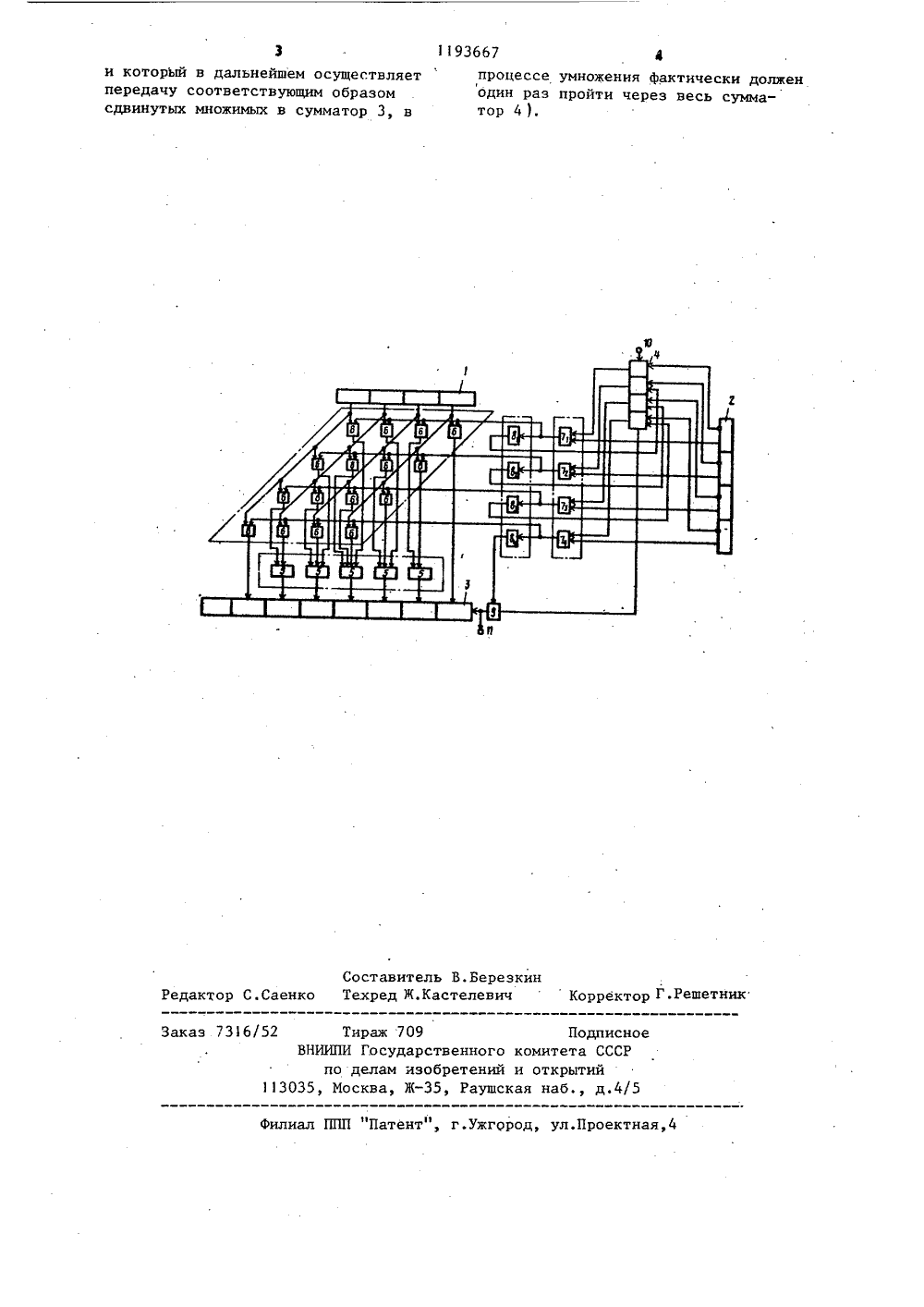

(504 С 06 Р 7/5 ОПИСАНИЕ ИЭОБРЕТ АВТОРСКОМУ СВИДЕТЕЛЬСТВУИЯ О ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(71) Минский радиотехнический ынститут(56) Авторское свидетельство СССРВ 482740, кл. б 06 Р 7/52, 1973Авторское свидетельство СССРР 623204, кл. б 06 Р 7/52, 1977.Авторское свидетельство СССРВ 985783, кл. 6 06 Г 7/52, 1981,(54) (57) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯЬ-РАЗРЯДНЫХ ЧИСЕЛ, содержащее регистры множимого и множителя, матрицуэлементов И, группу элементов И 31 И,накапливающий сумматор, группу элементов И и комбинационный сумматор,причем выходы разрядов регистрамножимого подключены к первым входамэлементов И соответствующих столбцовматрицы, прямые выходы разрядов регистра множителя соединены с первымивходами соответствующих элементов Игруппы, выходы которых соединены свторыми входами элементов И соответствующих строк матрицы, выходпервого элемента И первой строкиматрицы соединен с входом первогоразряда накапливающего сумматора,выход 11-го элемента И в-й строкиматрицы соединен с входом (2 а).-горазряда накапливающего сумматора,выходы элементов И )-й диагонали матрицы ,= 22 о) соединеныс входами(-1)-го элемента ИЛИ группы, выход р-го элемента ИЛИ группы (1=1,, 2 й.-3 ) соединен с входом(р+1 )-го разряда накапливающегосумматора, второй вход каждого элемента И группы соединен с выходомсоответствующего разряда комбинационного сумматора, вход переноса которого соединен с входом начала операции устройства, инверсные выходыразрядов регистра множителя подключены к первым входам соответствующихразрядов комбинационного сумматора,о т л и ч а ю щ е е с я тем, что,с целью повышения быстродействия,оно содержит группу элементов задержки и элемент ИЛИ, а накапливающий сумматор выполнен в виде сумматора с запоминанием переносов, приэтом выход 1 -го элемента И группы (1 =1й.) через соответствующийэлемент задержки группы соединенс вторым входом(1+1)-го разряда комбинационного сумматора, выход переноса которого подключен к первому входу элемента ИЛИ, выход Ь-го элемента И группы через соответствующий элемент задержки группы соединен с вторым входом элемента ИЛИ, выход которого подключен к входу управления приведением переносов на-. капливающего сумматора и выходу кон ца,операции устройства.ии ьН рпСМ Смфср Первая составляющая в приведенном выражении определяет среднее 50 число суммирований, выполняемыхв устройстве на сумматоре 3, предполагая, что появление нулей и единиц в разрядных множителях равновероятно. Вторая составляющая характеризу ет задержку, которую вносит в общеевремя выполнения операции сумматор 4 (сигнал, который в начале выполнения операции поступает на вход 10 1 1Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств умножения асинхронного типа.Цель изобретения - повышениебыстродействия устройства,На чертеже изображена структурная схема предлагаемого устройствадля умноженияЬ-разряднык чисел( для случая ь= 4).Устройство содержит регистр 1множимого, регистр 2 множителя,накапливающий сумматор 3 (выполненныйв виде сумматора с запоминаниемпереносов ), комбинационный сумматор4, группу элементов ИЛИ 5, матрицуэлементов И 6, группу элементов И 7группу элементов 8 задержки, .элементИЛИ 9, вход 10 начала операции,выход 11 конца операции,Устройство работает следующимобразом.Пусть требуется умножить и-разрядное множимое Х на и-разрядныймножитель 7 = 747 5 УУ= 1010. В исходном состояний в регистре 1 множимого хранится двоичный код числаХ без знака, в регистре 2 множителя - двоичный код числа У без знака,сумматор 3 обнулен.Работа устройства начинаетсяс момента подачи на вход 10 сигналаначала операции умножения (этот сигнал подается на вход 10 толькоодин раз в начале операции, а появление сигнала на выходе 11 сигнализирует об окончании операции умноже- .ния чисел 1 После этого на выходесумматора 4 формируется результатС = С 4 СЗСС = 0101+0000+0001 = 0110(первое слагаемое равно инверсномузначению множителя 7; второе слага-.емое поступает с выходов элементов8 задержки, третье слагаемое естьзначение входного переноса сумматора 4 ). Так как только С .У= 1, тоца выходе элемента И 7формируетсяуправляюпдй сигнал, который производит передачу соответствующим образом сдвинутого множимого с выходовэлементов И 6 второй строки матрицычерез элементы ИЛИ 5 в сумматор 3.Этот управляющий сигнал поступаетна вход элемента 8задержки и неменяет своего значения на протяжениивсего времени суммирования первогочастичного произведения в сумматоре3. По истечении времени, равного вре 193667 2мени суммирования первого частичногопроизведения в сумматоре 3, на выходеэлемента 8 задержки появляется сигнал, который, поступая на соответствующий вход сумматора 4, образуетего второе слагаемое 0100. При этомна выходе сумматора 4 формируетсярезультат С = С 1 С 5 С С = 0101+0100++0000 = 1001, в результате чего навыходе элемента И 7 формируется.управляющий сигнал (так как толькоС 4 У 4 = 1), который производит передачу соответствующим образом сдвинутого множимого с выходов элементов И 6 четвертой строки матрицычерез элементы ИЛИ 5 на входы сумматора 3. Этот управляющий сигнал поступает на вход элемента 8 задержки и не меняет своего значения напротяжении всего времени суммированиявторого частичного произведения всумматоре 3. По истечении этоговремени на выходе элемента 84 задержки появляется сигнал, который через .элемент ИЛИ 9 поступает на входуправления приведением переносовсумматора 3, разрешая суммированиев нем запоминающих переносов сцелью формирования результата в однорядном коде, а также подаетсяна выход 11, сигнализируя об окончании выполнения в нем операцииумножения двух чисел.4 Среднее время умножения двух,и-разрядных двоичных чисел в устрой-.стве примерно равно 40 Ънгдес - время суммирования и-разрядных чисел в сумматоре3 с запоминанием переносов;1 - время, необходимое насуммирование ь-разрядныхчисел в сумматоре 4 с распространением переносов.1193667 процессе умножения фактически долженодин раз пройти через весь сумматор 4 ). рректор Г.Решетник Составитель В.Березкинктор С.Саенко Техред Ж.Кастелевич Тираж 709 ВНИИПИ Государственного по делам изобретений 113035, Москва, Ж, Раушскаказ 316/52 Патент", г.ужгород, ул.Проектная,4 и который в дальнейшем осуществляетпередачу соответствующим образомсдвинутых множимых в сумматор 3, в Подписноеомитета СССРоткрытийя наб., д.4/5

СмотретьЗаявка

3499219, 14.10.1982

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

ЛОПАТО ЛИЛИЯ ГРИГОРЬЕВНА, ШОСТАК АЛЕКСАНДР АНТОНОВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: разрядных, умножения, чисел

Опубликовано: 23.11.1985

Код ссылки

<a href="https://patents.su/3-1193667-ustrojjstvo-dlya-umnozheniya-razryadnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения -разрядных чисел</a>

Предыдущий патент: Устройство для формирования знака результата последовательного сложения

Следующий патент: Устройство для умножения

Случайный патент: Пишущая машина с откидной съемной и заменяемой кареткой