Преобразователь последовательного кода в параллельной

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

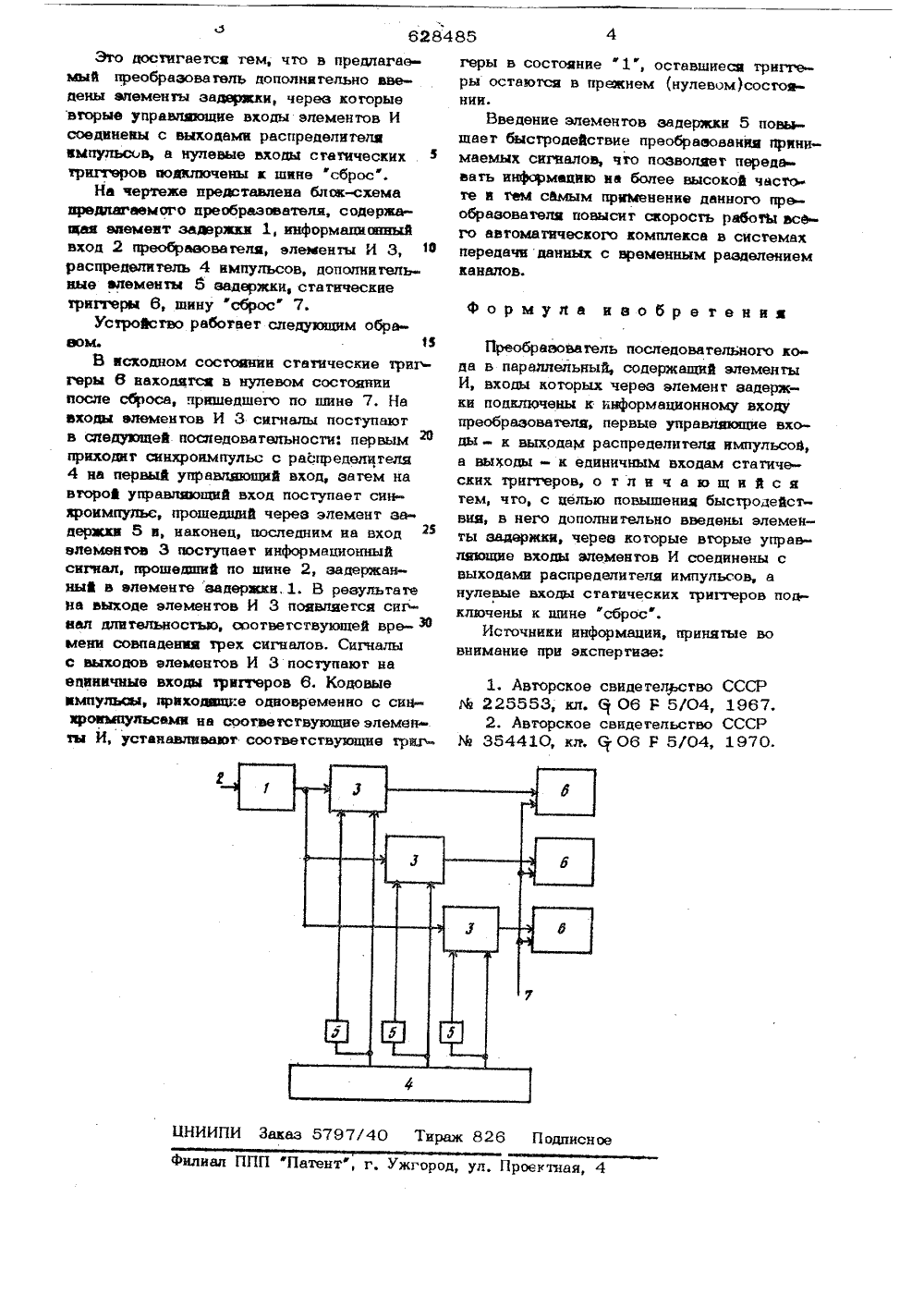

(22) Заявлено 2 с присоединен (23) Приорите (43) Опублико Гооудврственный квинтет Соовтв Мнннотров ССС оо делам нзобретеннй н открьтнйно 15.10.78.Бюллетень38 81.32588.8) 45) Дата опубликован исания 25,08,1 12) Авторы изобретени, А. Базалев и 3. И. Шарапов 1) Заявитель 4) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДЛ В ПАРАЛЛЕЛЬНЫЙинформационны на по величин сов, используе ся задержкаО отношению к не более по пульса. в течение первой соответствующего дается ложное сра преобразова те половины длсинхроимпубатывание с и тельностильса наблю татически ов, что перехопиводит, с скорости Наиболее бл ности к данном преобразовател в параллельный менты И, вхоць задержки подкл входу преобраз шие входы - к о технической сущтению являетси овательного кода 2 О зким и изобр послед 2 конечном иных процесодной старопередачи иэ-за налич рах, и ичению сов в триггены, к ограинформации,дежности содержаший элех через элемент ороны,ния при с д которь реобразредачи.является ин ормационн повышении Целью орос тибретенияйствия пр первые управляюраспрепели тели втелвходам повыше ние быстра образования. Изобретение относится к области вычислительной техники и может быть использовано для поеобразования последовательного кода в параллельный для систем передачи данных с временным разделением каналов.Известны преобразователи последовательного кода в параллельный 1 , содержащие регистр сдвига, генератор тактовых импульсов и схему фиксации конца кодовой комбинации.Недостатком таких устройств являет ся необходимость двухтактной сетки синхроимпульсов, а также возможность возникновения помехи в выходных схемах изза переходных процессов в устройстве. улъсов, а выходы - к единичным входамческих триггеровпреобразователе для повышения наежностц в случае, когда длительностьх символов близка или раве длительности синхроимпультся прямой и инверсный сигалпоследовательного кода и производитинформационного импульса по синхроимпульсу на величинулозины длительности синхроим628485 геры в состояние "1", оставшиеся триггеры остаются в прежнем (нулевом)состоянии.Введение элементов задержки 5 повышает быстродействие преобразования принимаемых сигналов, что позволяет передавать инфармацию на более высокой часто те и гвм самым применение данного преобразователя повысит скорость работы всего автоматического комплекса в системах передачи данных с временным разделением каналов. Преобразователь последовательного ко да в параллельный, содержащий элементы И, входи которых через элемент задержки подключены к информационному входу преобразователя, первые управляющие входы - к выходаМ распределителя импульсоб, а выходы к единичным входам статических триггеров, о т л и ч а ю щ и й с я тем, что, с целью повьппения быстродействия, в него дополнительно введены элементы задержки, через которые вторые управляющие входы элементов И соединены с выходами распределителя импульсов, а нулевые входы статических триггеров подключены к шине "сброс".Источники информации, принятые во внимание при экспертизе: 1. Авторское свидетельство СССРМ 225553, кл. С 06 Р 5/04, 1967. 2, Авторское свидетельство СССР% 354410, кл, Я 06 Р 5/04, 1970,5797/40 Тираж 8 П одписн ое Филиал ППП Патент", г. Ужгоро л. Проектная, 4 Это достигается тем, что в предлагаемый преобразова гель дополнительно введены элементы задерзиси, через которые вгорые управляющие входы элементов И соединены с выходами распределителя импульсов, а нулевые входы статических триггеров подключены к шине сброс.На чертеже представлена блок-схема предлагаемого преобразователя, содержащщ элемент задержки 1, информапианный вход 2 преобразователя, элементы И 3, распределитель 4 импульсов, дополнительные элементы 8 задержки, статические триггеры 6, шину сброс 7.Устройство работает следующим обраэомэ 15И исходном состоянии статические триггеры 6 находятся в нулевом состоянии после сброса, чришедшего по шине 7. На входы элементов И 3 сигналы поступают в следующей последовательности: первым ф приходит синхроимпульс с распределителя 4 на первый управляющий вход, затем на второй управляющий вход поступает сннхроимпулье, прошедший через элемент за держки 5 и, наконец, последним на вход элементов 3 поступает информационный сигнал, прошедший по шине 2, задержанный в элементе задержки, 1. В результате на выходе элементов И 3 появляегся сит зал длительностью, соответствующей вре- ЗО мени совпадения трех сигналов, Сигналы с выходов элементов И 3 поступают на едииичныв входы триггеров 6. Кодовые импульсы, приходвцке одновременно с снн ироимпульсами на соответствующие элемен ты И, устанавливают соответствукнцив гркгФормула изобретения

СмотретьЗаявка

2352592, 21.04.1976

ПРЕДПРИЯТИЕ ПЯ А-1001

БАЗАЛЕВ ЮРИЙ АЛЕКСЕЕВИЧ, ШАРАПОВА ЗОЯ ИВАНОВНА

МПК / Метки

МПК: G06F 5/04

Метки: кода, параллельной, последовательного

Опубликовано: 15.10.1978

Код ссылки

<a href="https://patents.su/2-628485-preobrazovatel-posledovatelnogo-koda-v-parallelnojj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельной</a>

Предыдущий патент: Устройство для ввода информации

Следующий патент: Устройство для сравнения двоичных чисел

Случайный патент: Кормораздатчик