Преобразователь последовательного кода переменной длины в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1290538

Авторы: Джанджулян, Маргарян, Папоян, Чалахян

Текст

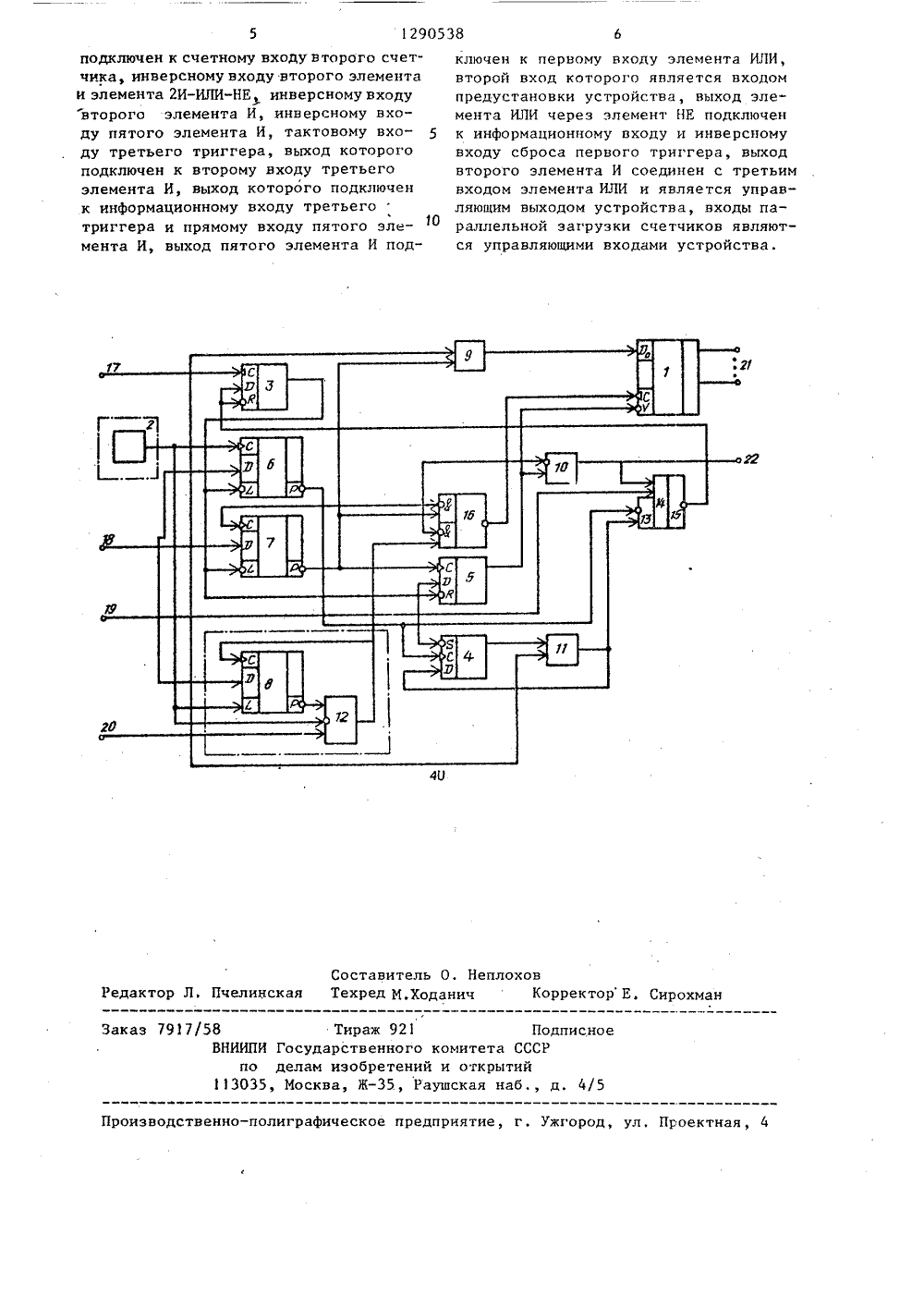

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК И 9) (И) 4 Н 03 М 9/О СВИДЕТЕЛЪ Н ДВТОРСН нджул ССС1984 ВАТЕЛЬПАРАЛ -к циф может ии ста СЭ Об ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ(54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕ ГО КОДА ПЕРЕМЕННОЙ ДЛИНЫ В ЛЕЛЬНЫЙ(57) Изобретение относится вой вычислительной технике быть использовано при пост преобразователей, входящих блоков сопряжения цифровых устройствс каналами связи. Целью изобретенияявляется расширение функциональныхвозможностей за счет введения контроля и расширения области примененияза счет приема кодов переменной длины. Для этого устройство содержитсдвиговый регистр 1, генератор 2импульсов, триггеры 3,4,5, счетчики6,7,8, элементы 9-13 И, элемент 14ИЛИ, элемент 15 НЕ, элемент 6 2 ИИЛИ-НЕ, информационный 7, управляющий 18, предустановки 19, тактовый20 входы преобразователя, информационные 21 и управляющий 22 выходыпреобразователя. 1 ил, 1 12905Изобретение относится к циФровойи вычислительной технике и можетбыть использовано при построениипреобразователей, входящих в составблоков сопряжения цифровых устройствс каналами связи.Цель изобретения - расширениефункциональных возможностей путемвведения контроля и расширения области применения обеспечением приема10кодов переменной длины.На чертеже показана блок-схемапредлагаемого устройства.П еобразователь содержит сдвигаР15вый регистр 1, генератор 2 импульсов,триггеры 3-5, счетчики 6-8, элементы 9-13, элементы ИЛИ 14, элементыНЕ 15, элементы 2 И-ИЛИ-НЕ 16, информационный 17, управляющий 18,предустановки 9 и тактовый 20 входы20преобразователя, информационные 21и управляющий 22 выходы преобразователя,Устройство работает следующим образом.С поступлением сигнала предустановки по входу 19 устройство устанавливается в исходное состояние:триггер 3 сбрасывается, в результате30,чего нулевой уровень на его выходепереводит счетчики 6 и 7 в состояниеприема данных со своих информационных входов, устанавливается триггер4 и сбрасывается триггер 5. На инверсном выходе переноса счетчика б Формируются сигналы стробирования данных, поступающих по информационномувходу 17 устройства в сдвиговый регистр 1, в серединах периодов битов.Для этого на информационных входах40счетчика 6, выбранного четырехразрядным, скоммутирован код чисел 7(0111) , а частота сигналов генератора 2 выбрана равной шестнадцатикратной частоте поступления битов.45По спаду сигнала на информационномвходе 17 преобразователя, соответствующему поступлению стартового разряда кода, триггер 3 устанавливается исчетчики 6 и 7 переходят в счетныйрежим. Отсчитав по сигналам генератора 2 восемь импульсов, счетчик бпринимает значение 15 (111) и вотрицательный полупериод импульсагенератора 2 на его выходе переносаустанавливается нулевой уровень, Папервому сигналу счетчика 6 производится прием стартового бита в сдвига 38вый регистр 1. Счетчик б прадалжа" ет циклически, отсчитывать шестнадцать импульсов с 0 (0000) до 15 (111) и Формировать сигналы переноса в серединах следующих битов, С приемом битов прибавляется единица к содержимому счетчика 7. Исходное значение счетчика 7 устанавливается в соответствии с длиной принимаемого кода на управляющих 18 входах преобразователя, подключенных к информационным входам счетчика 7. Для И-разрядного кода исходное значение счетчика 7 устанавливается в соответствии с выражением 2 -(И+1)-, где (И+) число разрядов с учетом,стартовога;разрядность счетчика. Таким образам, в момент времени, когда счетКчик 7 досчитает до 2 - 1, стартовый и все информационные разряды приняты в сдвиговый регистр . В случае приема кода разрядностью 2в сдвиговам регистренаходятся только информационные разряды, а стартовый разряд выдвинут из сдвигового регистра, Для кодов меньшей разрядности требуется произвести нормализацию принятого кода в сдвигавом регистре таким образом, чтобы стартовый разряд выдвинулся из сдвигавого регистра, младший разряд кода установился в младшем разряде регистра, а используемые старшие ега разряды заполнялись нулями. Дополнительные сдвиги производятся в течение времени переноса счетчика 7, Сигнал переноса ,счетчика 7 Формируется при поступлении следующего сигнала переноса счетчика б для страбиравания контрольного разряда по паритету. Нулевой уровень на выходе переноса счетчика 7 запрещает прохождение сигнала переноса счетчика 6 через элемент.2 И-ИЛИ-НЕ 6, устанавливает нулевой уровень на входе элемента И 9 и разрешает прохождение сигналов нормализации с выхода элемента И 12. Число импульсов нормализации определяется начальным значением кода счетчика 8, В положительные палупериады сигналов генератора 2 счетчик 8 находится в состоянии приема начального значения кода, поступающего с управляюцгих входов 18 устройства на информационные входы счетчика 8. Элемент И 12 закрыт в положительные палупериады сигнала генератора 2, поступающего на ега инверсный вход. В отрицательг.ые палупериадысигналов генератора 2 элемент И 12 открыт и тактовые сигналы с входа 20 преобразователя поступают на счетный вход счетчика 8 и на вход элемента 2 И-ИЛИ-НЕ 16, Прохождение этих сигналов на тактовый вход сдвигового регистра управляется сигналом переноса счетчика 7, На информационном входе сдвиговом регистре 1 установлен нулевой уровень, поэтому при норма- О лизации кода неиспользуемые старшие его разряды заполняются нулями. Процесс нормализации прекращается при возникновении сигнала переноса на выходе счетчика 8, 5По окончании сигнала переноса счетчика 7 (перепад с нулевого уровня в единичный) устанавливается триггер 5, который блокирует режим сдвигового регистра 1 и разрешает прохождение сигнала переноса счетчика 6 через элемент И 10, Следующий сигнал переноса счетчика 6, формируемый в момент приема первого стопового бита проходит через элемент 10 И на выход 22 преобразователя и может быть использован в качестве стробирующего сигнала передачи данных из сдвигового регистра 1 во внешние схемы, Кроме того, этот же сигнал проходит30 через элемент ИЛИ 14 и устанавливает преобразователь в исходное состояние, С поступлением следующего стартового сигнала по информационному входу 6 работа устройства возобновляется. 35 Достоверность принимаемой информации определяется посредством триггера 4 и элемента . И 11. Триггер 4 в исходном состоянии установлен. В момент стробирования стартового бита (первый сигнал переноса счетчика 6) проверяется состояние линии связи, т.е. если на информационном входе 17 устройства и соответственно на втором 45 входе элемента И 11 нулевые уровни, это означает, что имеется действительная стартовая посылка и нет помех на линии связи. Поэтому на Э- входе триггера 4 установлен нулевой уровень. С приходом сигнала переноса счетчика 6 он сбрасывается по заднему фронту сигнала (перепад с нулевого уровня на единичный). В противном случае триггер 4 не сбрасывается, на выходе элемента . И 1 остается единичный .уровень, и сигнал переноса счетчика 6, проходя через элемент И-ИЛИ-НЕ, приводит устройство в исходное состояние,Формула изобретенияПреобразователь последовательного кода переменной длины в параллельный, содержащий первый элемент И, первый вход которого является информационным входом устройства, выход подключен к .информационному входу регистра сдвига, выходы которого являются информационными выходами устроЙ- ства, первый триггер, первый счетчик, генератор импульсов, элемент ИЛИ, элемент НЕ, о т л и ч а ю щ и й с я тем, что, с целью расширения функциональных воэможностей за счет введения контроля и расширения области применения за счет приема кодов переменной длины, в него введены второй и третий счетчики, второй и третий триггеры, второй, третий, четвертый и пятый элементы И, элемент 2 И-ИЛИНЕ, выход которого соединен с тактовым входом регистра сдвига, управляющий вход которого объединен с прямым входом второго элемента И и подключен к выходу второго триггера,выход первого триггера подключен к инверсному входу сброса и информационному входу второго триггера, инверсным входам загрузки первого и второго счетчиков, инверсному входу установки четвертого триггера, тактовый вход первого триггера объединен с первым входом третьего элемента И и подключен к информационному входу устройства, выход генератора импульсов подключен к тактовому входу первого счетчика, прямому входу загрузки.третьего счетчика и инверсному входу четвертого элемента И, первый прямой вход которого является тактовым входом устройства, выход переноса третьего счетчика подключен к второму прямому входу четвертого элемента И, выход которого соединен со счетным входом третьего счетчика и прямым входом первого элемента И элемента 2 И-ИЛИ-НЕ, инверсный вход которого объединен с прямым входомФвторого элемента И элемента 2 И-ИЛИ-НЕ тактовым входом второго триггера, вторым входом первого элемента И и подключен к инверсному выходу переполнения второго счетчика, инверсный выход переполнения первого счетчика1290538 Составитель О, Неплоховедактор Л. Пчелинская Техред М.ХоданичКорректор Е. Сирохман каз 7917/5 Тираж 921 Подписноеосударственного комитета СССРелам изобретений и открытийМосква, Ж, Раушская наб., д. 4/5 8 ВНИИПИ Гпо д 113035,Производственно-полиграфическое предприятие, г. Ужго Проектная подключен к счетному входу второго счетчика, инверсному входу второго элементаи элемента 2 И-ИЛИ-НЕ инверсному входувторого элемента И, инверсному входу пятого элемента И, тактовому входу третьего триггера, выход которогоподключен к второму входу третьегоэлемента И, выход которого подключенк информационному входу третьеготриггера и прямому входу пятого элемента И, выход пятого элемента И подключен к первому входу элемента ИЛИ, второй вход которого является входом предустановки устройства, выход элемента ИЛИ через элемент НЕ подключен к информационному входу и инверсному входу сброса первого триггера, выход второго элемента И соединен с третьим входом элемента ИЛИ и является управляющим выходом устройства, входы параллельной загрузки счетчиков являются управляющими входами устройства.

СмотретьЗаявка

3941619, 06.08.1985

ПРЕДПРИЯТИЕ ПЯ А-7390

ЧАЛАХЯН ЭДУАРД ПЛАТОНОВИЧ, ДЖАНДЖУЛЯН ЭДУАРД ЛЕВОНОВИЧ, МАРГАРЯН АМАЯК ГАРЕГИНОВИЧ, ПАПОЯН АНАИТ ОГАНЕСОВНА

МПК / Метки

МПК: H03M 9/00

Метки: длины, кода, параллельный, переменной, последовательного

Опубликовано: 15.02.1987

Код ссылки

<a href="https://patents.su/4-1290538-preobrazovatel-posledovatelnogo-koda-peremennojj-dliny-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода переменной длины в параллельный</a>