Интегратор импульсных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

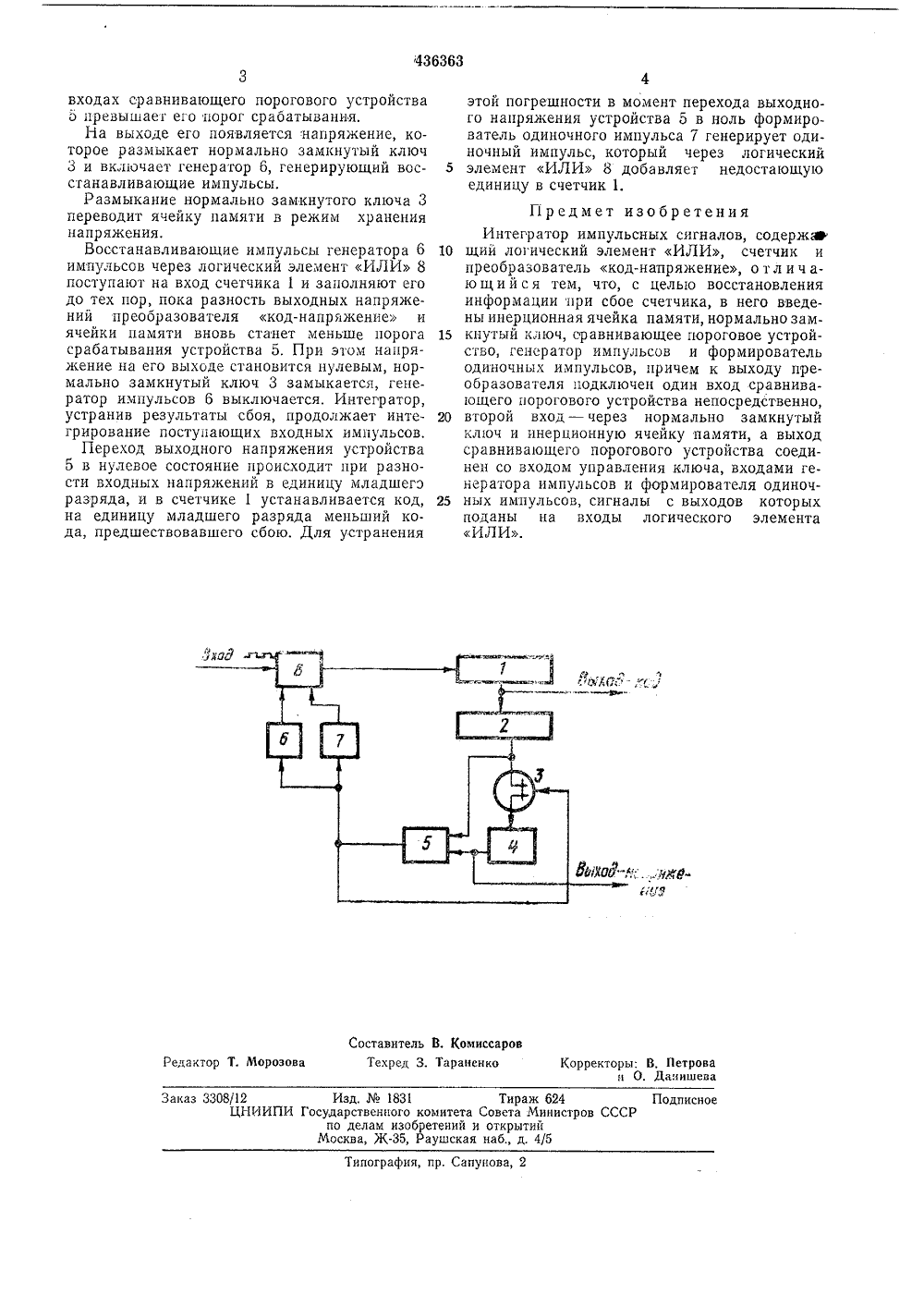

(32) Приоритег 51) М, Кл, б 06 д 7/18Н 031 5/156 Гасударстеенныи комитет Совета Министров СССР оо дедам иэааретений и открытий(54) ИНТЕГР Интегратор работает следующим образом.Импульсы, подлежащие интегрированию, через логический элемент ИЛИ поступают на вход счетчика 1, в нем они накапливаются в 5 виде кода. Код преобразуется в преобразователе 2 в сигнал постоянного тока, который при замкнутом ключе 3 прикладывается ко входу инерционной ячейки 4 и запоминается ею при размыкании нормально замкнутого ключа 3. О Напряжения с выходов преобразователя 2 иячейки 4 прикладываются ко входам сравни вающего порогового устройства 5. Если разность напряжений не превышает по абсолютной величине порога срабатывания, то напря 5 жение на выходе сравнивающего пороговогоустройства 5 нулевое. Величина порога соответствует значению, большему единицы и меньшему двух единиц младшего разрядасчетчика 1.О Инерционно при поступлен руемых импул частоты напря 25 личаются мень батывания сра ства 5. При с чика, кроме п за появления ЗО перерыва пита1етение относится к импульсной техИзобрнике.Известен интегратор импульсных сигналов, содержащий логическую схему ИЛИ, счетчик и преобразователь код-напряжение.С целью восстановления информации при сбое счетчика в предлагаемый интегратор введены инерционная ячейка памяти, нормально замкнутый ключ, сравнивающее пороговое устройство, генератор импульсов и формирователь одиночных импульсов, причем к выходу преобразователя подключен один вход сравнивающего порогового устройства непосредственно, второй вход - через нормально замкнутый ключ и инерционную ячейку памяти, а выход сравнивающего порогового устройства соединен со входом управления ключа, входами генератора импульсов и формирователя одиночных импульсов, сигналы с выходов которых поданы на вход логического элемента ИЛИ.На чертеже дана блок-схема предлагаемого интегратор а.Предлагаемый интегратор содержит счетчик 1, преобразователь 2 код-напряжение, нормально замкнутый ключ 3, инерционную ячейку памяти 4, сравнивающее пороговое устройство 5, генератор 6 импульсов, формирователь 7 одиночного импульса, логический элемент ИЛИ 8,сть ячейки памяти такова, что ии на вход счетчика 1 интегриьсов максимально возможной жения на ее входе и выходе отше, чем на величину порога сравнивающего порогового устройбое в любом из разрядов счетервого, что может произойти из помехи или кратковременного ния, разность напряжений наректоры: В, Петрова н О, Данишева озова еда кто Тираж 624 а Совета Министров и открытий я наб., д. 4/5Изд.1831 И Государственного комите по делам изобретени Москва, Ж, Раушскаказ 3308/12ЦНИ ПодписноеСР ипография, пр. Сапунова, 2 входах сравнивающего порогового устройства 5 превышаег его порог срабатывания.На выходе его появляется напряжение, которое размыкает нормально замкнутый ключ 3 и включает генератор б, генерирующий восстанавливающие импульсы.Размыкание нормально замкнутого ключа 3 переводит ячейку памяти в режим хранения напряжения.Восстанавливающие импульсы генератора б импульсов через логический элемент ИЛИ 8 поступают на вход счетчика 1 и заполняют его до тех пор, пока разность выходных напряжений преобразователя код-напряжение и ячейки памяти вновь станет меньше порога срабатывания устройства 5. При этом напряжение на его выходе становится нулевым, нормально замкнутый ключ 3 замыкается, генератор импульсов б выключается. Интегратор, устранив результаты сбоя, продолжает интегрирование поступающих входных импульсов.Переход выходного напряжения устройства 5 в нулевое состояние происходит при разности входных напряжений в единицу младшегэ разряда, и в счетчике 1 устанавливается код, на единицу младшего разряда меньший кода, предшествовавшего сбою, Для устранения этой погрешности в момент перехода выходного напряжения устройства 5 в ноль формирователь одиночного импульса 7 генерирует одиночный импульс, который через логический 5 элемент ИЛИ 8 добавляет недостающуюединицу в счетчик 1,Предмет изобретенияИнтегратор импульсных сигналов, содержМ 10 щий логический элемент ИЛИ, счетчик ипреобразователь код-напряжение, о т л и ч аю щ и й с я тем, что, с целью восстановления информации при сбое счетчика, в него введены инерционная ячейка памяти, нормально зам кнутый ключ, сравнивающее пороговое устройство, генератор импульсов и формирователь одиночных импульсов, причем к выходу преобразователя подключен один вход сравнивающего порогового устройства непосредственно, 20 второй вход - через нормально замкнутыйключ и инерционную ячейку памяти, а выход сравнивающего порогового устройства соединен со входом управления ключа, входами генератора импульсов и формирователя одиноч ных импульсов, сигналы с выходов которыхподаны на входы логического элемента ИЛИ.

СмотретьЗаявка

1835954, 06.10.1972

Ю. В. Каштанов, А. А. Прозоров, Ю. Н. Родионов, Н. Т. Тренкин

МПК / Метки

МПК: G06G 7/18, H03K 5/156

Метки: импульсных, интегратор, сигналов

Опубликовано: 15.07.1974

Код ссылки

<a href="https://patents.su/2-436363-integrator-impulsnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Интегратор импульсных сигналов</a>

Предыдущий патент: Устройство для умножения и деления напряжений

Следующий патент: 436364

Случайный патент: Весовыбойный аппарат для упаковки муки в тканевые мешки