410567

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 410567

Текст

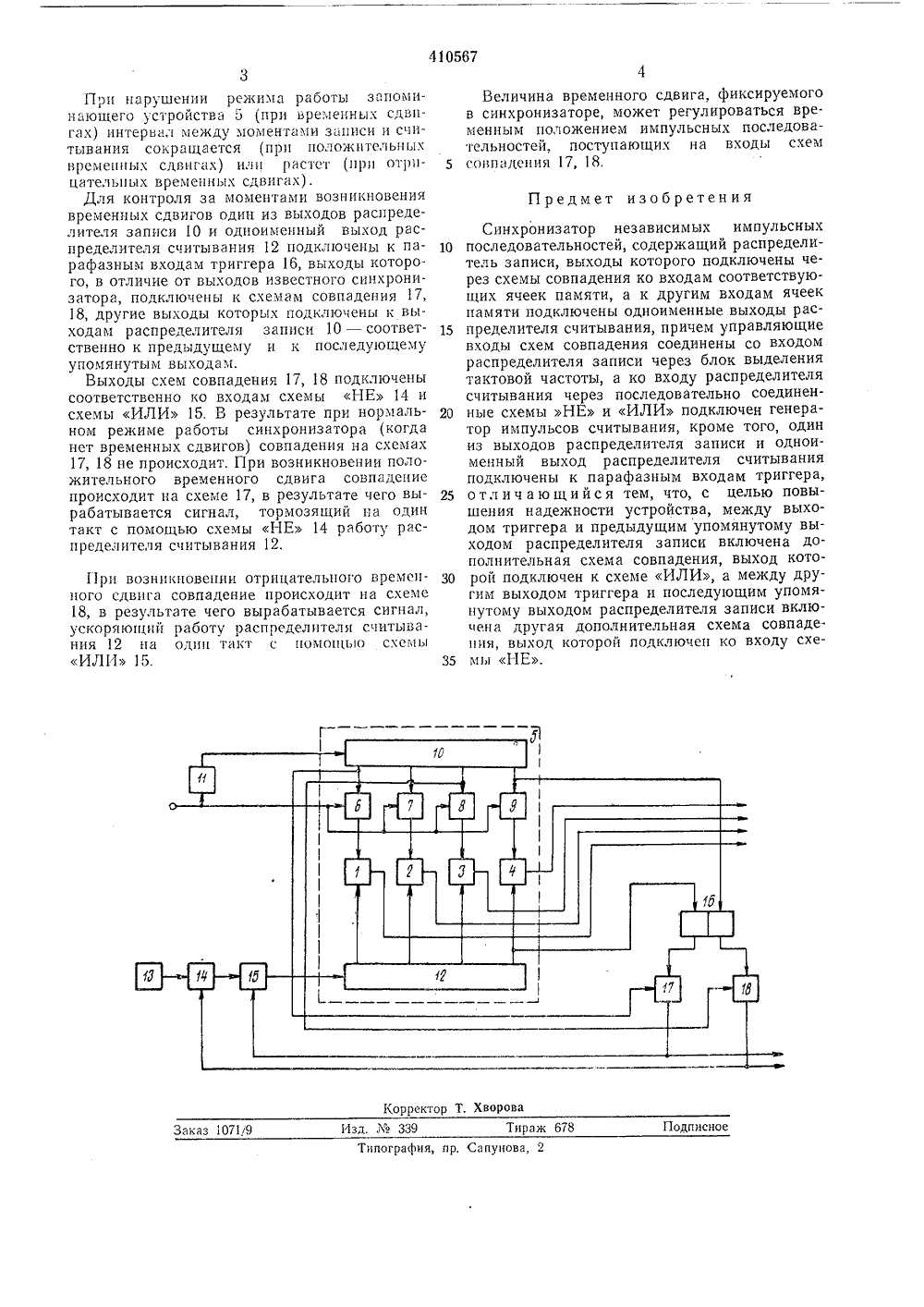

ийтй н тес=то а. пи ч еса библиосна МБА ОПИСАНИЕ ИЗОБРЕТЕНИЯ 4 Ю 567 Союз Советских Соыфйпистимеск 1 х Р:пупикТЕЛЬСТВУ тваявлено 16.11,1972 (Лф 1759280/26 7/04 М. Кл,Государственный комит Совета Министров ССС о делам иэооретений и открытий. С. Л ягков Заявитель тральный научи тут связ тельскии и сследо ИМЫХ ИМПУЛЬСНЫХЛЬНОСТЕй пия,выход которой и а между другим выхо щим упомянутому в записи включена дру ма совпадения, выхо входу схемы НЕ. На чертеже изображея схема синхронизатора,Импульсная последовательность от источника информации записывается последовательно в ячейки памяти 1 - 4 запоминающего устройства 5.Процессом записи управляют схемы совпадения б - 9, открываемые поочередно сигналами с соответствующих выходов распределителя записи 10, на вход которого поступает сигнал с блока выделения тактовой частоты 11.Считывание выполняют сигналы с выходов распределителя считывания 12, управляемого генератором импульсов считывания 13 через последовательно соединенные схемы НЕ 14ИЛИ 15 на функциональна запиа кпос синхроциот момен- боты запозаписи в ячейки 1, 2, при заПри нормал затора момен та записи на минающего у ячейку 3 счит при записи в писн в ячейку ме работыия отстоитпериода раТак, приоисходит сс ячейкийкиЗит. ьном режит считыванполовинустройства,ывание прячейку 4 -1 - с яче К АВТОРСКОМУ СВИ Зависимое от авт. свидетель исоединением заявкита опубликования описа СИНХРОНИЗАТОР НЕЗАВИ ПОСЛ ЕДОВАТИзобретение относится к многоканальнои связи с импульсно-кодовой модуляцией и временным делением каналов, предназначенной для передачи независимых импульсных последовательностей.Известен синхронизатор независимых импульсных последовательностей, обеспечивающий ввод этих последовательностей в системы связи с импульсно-кодовой модуляцией, содержащий распределитель записи, выходы которого через схемы совпадения подключены ко входам соответствующих ячеек памяти, а к другим входам ячеек памяти подключены одноименные выходы распределителя считывания, причем управляющие входы схем совпадения соединены со входом распределителяси через блок выделения тактовой частоты,о входу распределителя считывания через ледовательно соединенные схемы НЕ и ИЛИ подключен генератор импульсов считывания. Кроме того, один из выходов распределителя записи и одноименный выход распределителя считывания подключены к парафазным входам триггера.Цель изобретения - повышение надежности устройства.Предлагаемый синхронизатор отличается тем, что между выходом триггера и предыдущим упомянутому выходом распределителя записи включена дополнительная схема совпадедключен к схеме ИЛИ, ом триггера и последуюыходом распределителя гая дополнительная схекоторой подключен ко410567 Корректор Т, Хворова Подписное Тираж 678 Изд.339 Заказ 1071/9 Типография нр, Сапунова, 2 Прц нарушении режима работы запоминающего устройства 5 (при временных сдвигах) интервал между моментами записи и считывания сокращается (прп положительных времешпях сдвигах) или растет (при отрицательных временных сдвигах),Для контроля за моментами возникновения временных сдвигов один из выходов распределителя записи 10 и одноименный выход распределителя считывания 12 подключены к парафазным входам триггера 16, выходы которого, в отличие от выходов известного синхронизатора, подключены к схемам совпадения 17, 18, другие выходы которых подключены к выходам распределителя записи 10 - соответственно к предыдущему и к последующему упомянутым выходам.Выходы схем совпадения 17, 18 подключены соответственно ко входам схемы НЕ 14 и схемы ИЛИ 15. В результате при нормальном режиме работы синхронизатора (когда нет временных сдвигов) совпадения на схемах 17, 18 не происходит. При возникновении положительного временного сдвига совпадение происходит на схеме 17, в результате чего вырабатывается сигнал, тормозящий на один такт с помощью схемы НЕ 14 работу распределителя считывания 12. 11 ри возникновении отрицательного временного сдвига совпадение происходит на схеме 18, в результате чего вырабатывается сигнал, ускоряющий работу распределителя считывания 12 на один такт с помощью схемы ИЛИ 5. Величина временного сдвига, фиксируемогов синхронизаторе, может регулироваться временным положением импульсных последовательностей, поступающих на входы схем 5 совпадения 17, 18,Предмет изобретения Синхронизатор независимых импульсных 10 последовательностей, содержащий распределитель записи, выходы которого подключены через схемы совпадения ко входам соответствующих ячеек памяти, а к другим входам ячеек памяти подключены одноименные выходы рас пределителя считывания, причем управляющиевходы схем совпадения соединены со входом распределителя записи через блок выделения тактовой частоты, а ко входу распределителя считывания через последовательно соединен цые схемыНЕ и ИЛИ подключен генератор импульсов считывания, кроме того, один из выходов распределителя записи и одноименный выход распределителя считывания подключены к парафазным входам триггера, 25 отл ич а ющи йся тем, что, с целью повышения надежности устройства, между выходом триггера и предыдущим упомянутому выходом распределителя записи включена дополнительная схема совпадения, выход кото рой подключен к схеме ИЛИ, а между другим выходом триггера и последующим упомянутому выходом распределителя записи включена другая дополнительная схема совпадения, выход которой подключен ко входу схе мы НЕ,

СмотретьЗаявка

1759280, 16.03.1972

МПК / Метки

МПК: H04L 7/04

Метки: 410567

Опубликовано: 05.01.1974

Код ссылки

<a href="https://patents.su/2-410567-410567.html" target="_blank" rel="follow" title="База патентов СССР">410567</a>

Предыдущий патент: 410566

Следующий патент: 410568

Случайный патент: Состав покрытия для защиты металла от окисления при нагреве и способ приготовления покрытия