Интегро-дифференциальный вычислитель

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1108445

Автор: Баранов

Текст

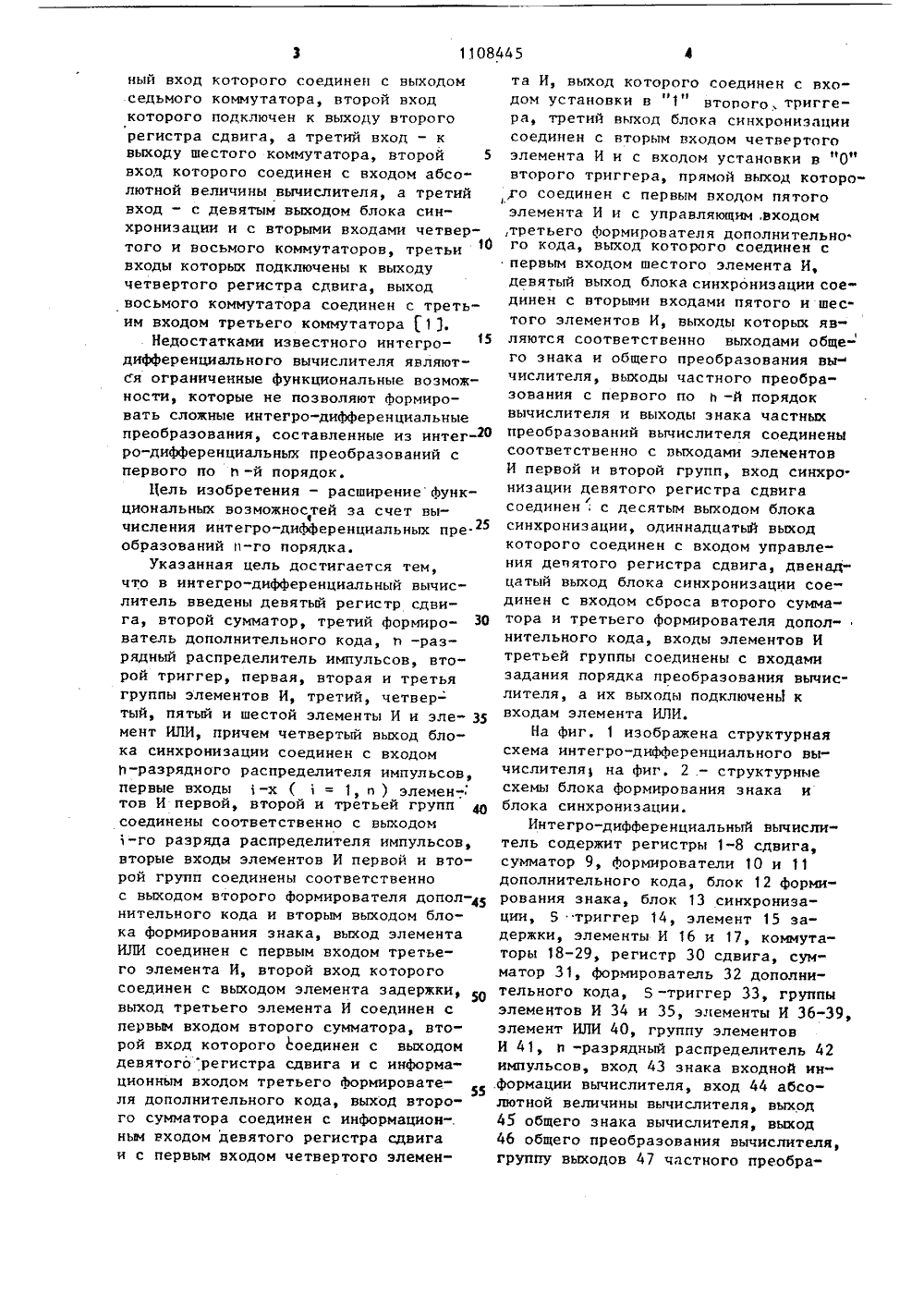

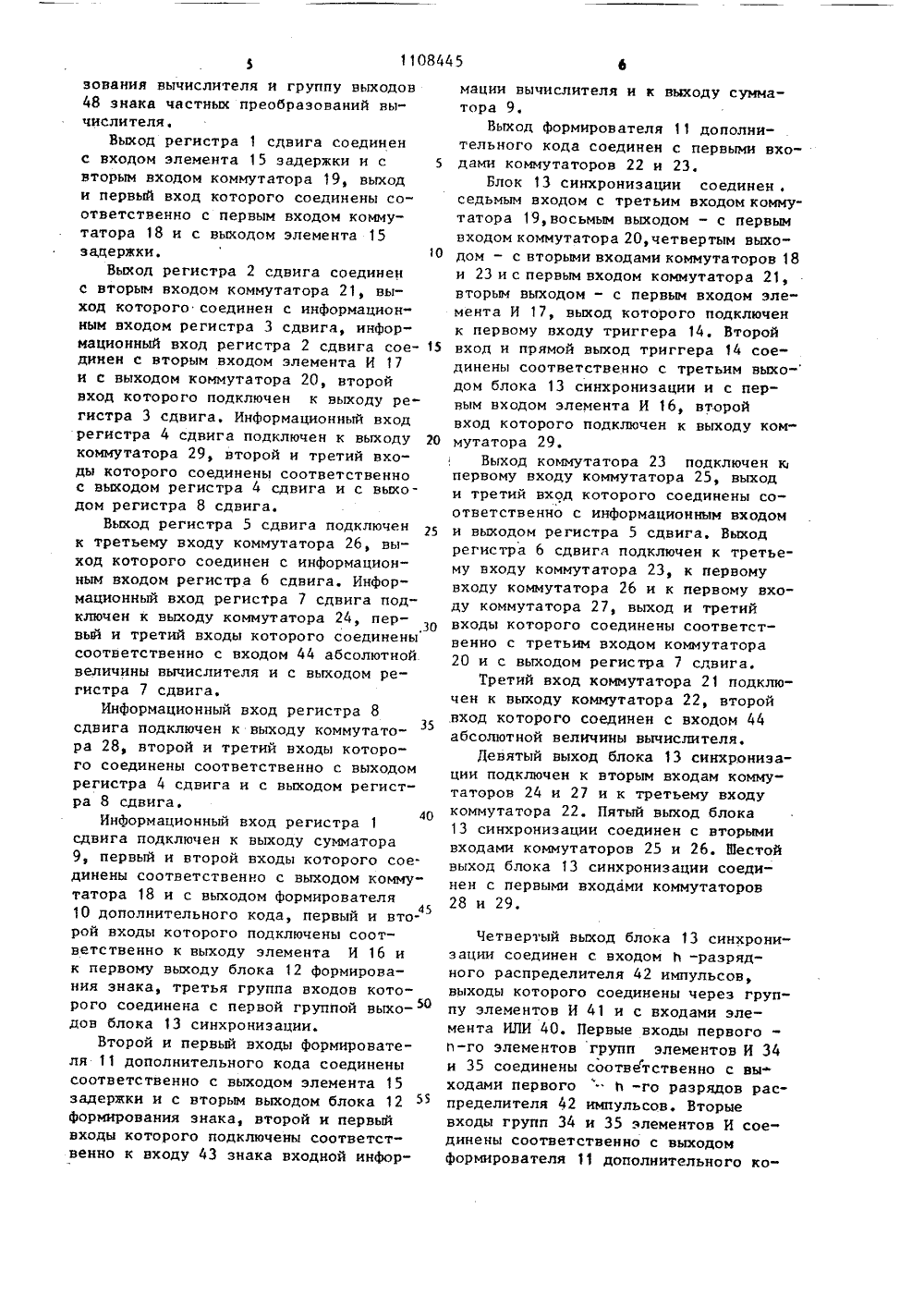

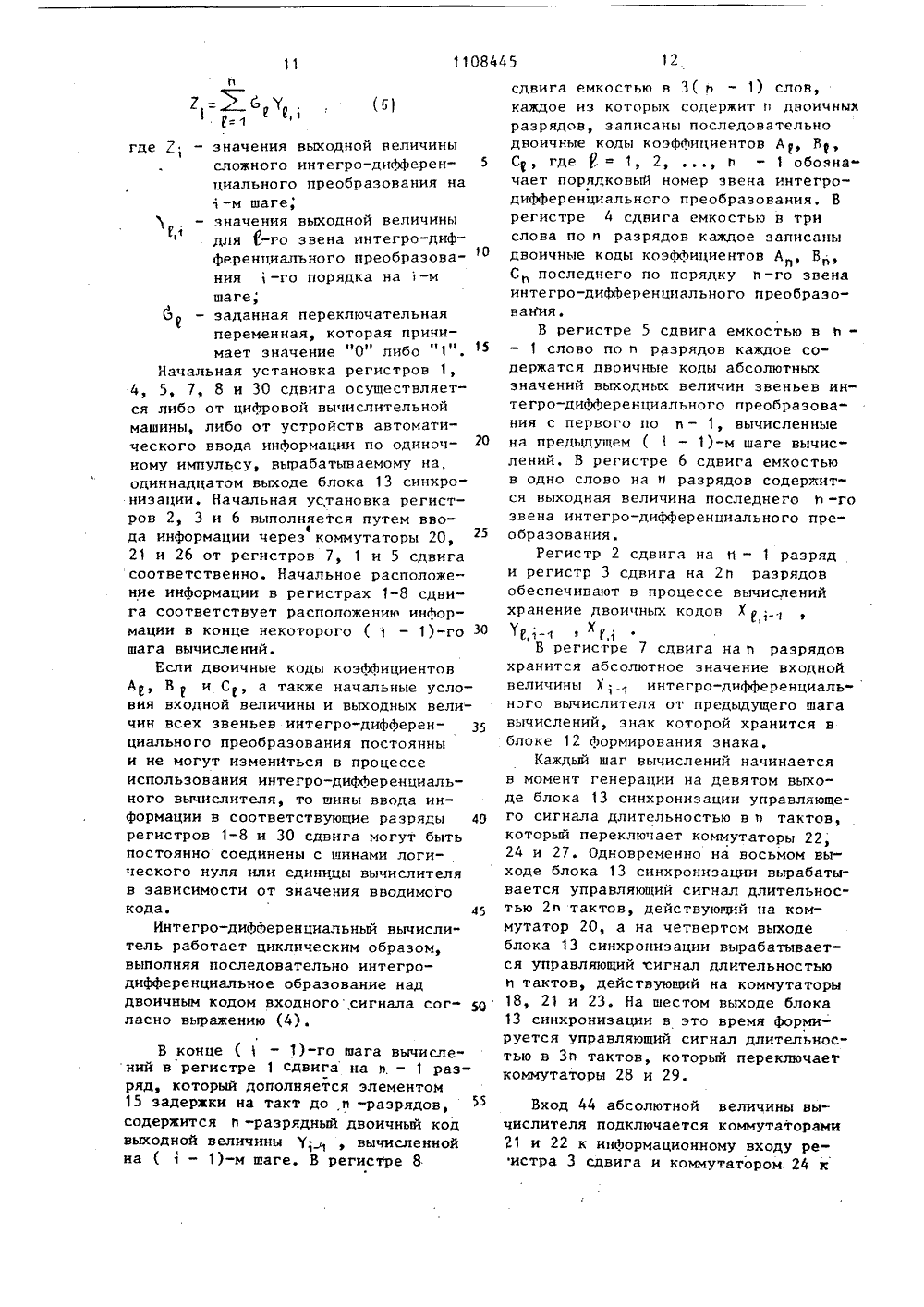

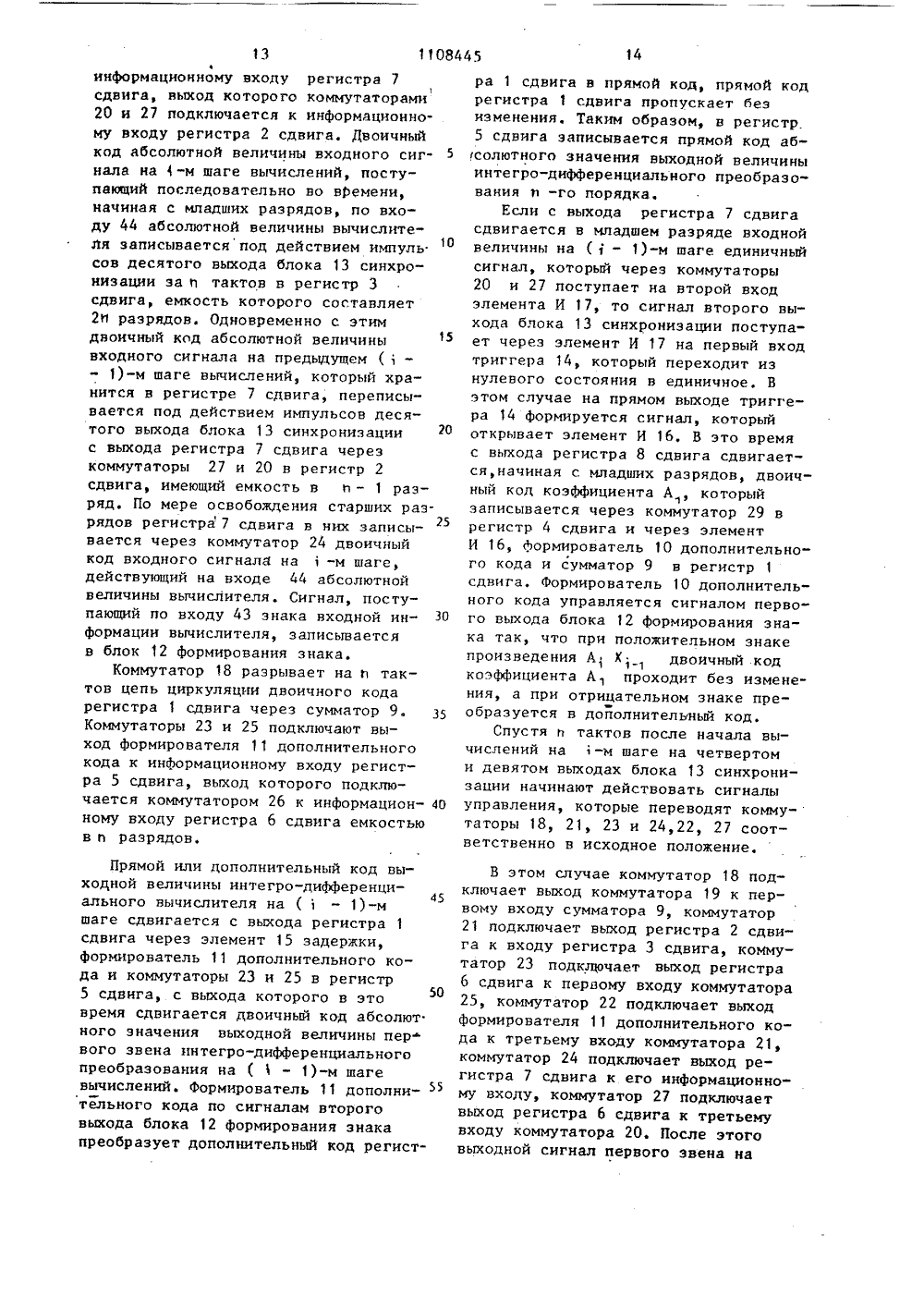

.801108445 А С 06 Р 7/64 ОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬПИЙ(71) Институт электродинамики АН УССРи Ордена Ленина институт кибернетики им, В.М, Глушкова(56) 1, Авторское свидетельство СССРВ 955051, кл. Ь 067/64, 1981(54)(57) ИНТЕГРО-ДИФФЕРЕНЦИАЛЬНЫЙВЫЧИСЛИТЕЛЬ по ант,св. У 955051,о т л и ч а ю щ и й с я тем, что,с целью расширения функциональныхвоэможностей за счет вычисления интегро-дифференциальных преобразований и -го порядка, в него введены девятый регистр сдвига, второй сумматор, третий формирователь дополнительного кода, и - разрядный распределитель импульсов, второй триггер,первая, вторая и третья группы элементов И, третий, четвертый, пятыйи шестой элементы И и элемент ИЛИ,причем четвертый выход блока синхронизации соединен с входом и -разрядного распределителя импульсов, первые входы 1-х (1=1,п) элементов Ипервой, второй и третьей групп соединены соответственно с выходом 1-горазряда распределителя импульсов,вторые входы элементов И первой ивторой групп соединены соответственнос выходом второго формирователя дополнительного кода и вторым выходомблока формирования знака, выход элемента ИЛИ соединен с первым входомтретьего элемента И, второй вход ко торого соединен с выходом элемента задержки, выход третьего элемента И соединен с первым входом второго сумматора, второй вход которого соединен с находом девятого регистра сдвига и с информационным входом третьего формирователя дополнительного кода, выход второго сумматора соединен с информационным входом девятого регистра сднига и с первым вхо. дом четвертого элемента И, выход которого соединен с входом установки в "1" второго триггера, третий выход блока синхронизации соединен с вторым входом четвертого элемента И и с входом установки в "0" второго триг- ф гера, прямой выходкоторого соединен с первым входом пятого элемента И и с управляющим входом третьего формиро . вателя дополнительного кода, выход которого соединен с первым входом шестого элемента И, девятый выход блока синхронизации соединен с вторыми входами пятого и шестого элементов И,Феей выходы которых являются соответственно выходами общего знака и общего преобразования вычислителя, выходы частного преобразования с первого по п-й порядок вычислителя и выходы знака частных преобразований вычислителя соединены соответственно с выходами элементов И первой и нторой групп, вход синхронизации девятого регистра сдвига соединен с десятым выходом блока синхронизации, одиннадцатый выход которого соедийен с входом управления девятого регистра сдвига, двенадцатый выход блока синхронизации соединен с входом сброса второго сумматора и третьего формирователя дополнительного кода, входы элемен 1108445 18,вующими на первом входе элементаИ 17, совпадают сигналы вторых разря"дов величин Х 1 , У 1,, Х,Спустя Зь тактов после началавычислений на седьмом и шестом выхадах блока 13 синхронизации формируются сигналы управления, которые приводят к переключению коммутаторов 19,28 и 29 соответственна. Коммутатор19 подключает выход регистра 1 сдвига через коммутатор 18 к первому входу сумматора 9, Этим обеспечиваетсясдвиг в регистре 1 двоичного коданакопленной суммы коэффициентов А 1,В , Сна один разряд или умножениеэтой суммы на два.Коммутатор 28 подключает выход регистра 8 сдвига к его информационному входу, а коммутатор 29 подключает выход регистра 4 сдвига к своемувходу. В результате этого в регистре4 сдвига запоминаются двоичные кодыкоэффициентов А, В , С, а в регистре 8 сдвига - двоичные коды коэффициентов А, В, С, где ь = 2, 3. и ЛСпустя и тактов после переключения коммутатора 19 на седьмом выходе блока 13 синхронизации формируется сигнал управления, который возвраща 30 ет коммутатор 19 в исходное состояние.Цепь циркуляции кодов в регистре 1 сдвига вновь замыкается через элемент 15 задержки, коммутаторы 18 и 19 и сумматор 9.В течение 3 итактов после начала вычислений интегро-дифференциальный вычислитель работает так же, как и на первых Зп тактах работы. В регистре 1 сдвига накапливаются и стар"40 ших разрядов суммы произведений величин Х;, У,и Х на двоичныекоды коэффициентов А, В, С соответственно. Согласно соотношению (4) этот результат соответствует выход 45 ной величине Упервого звена интег 1ро -диффер е нци ально го преобразования на 1 "м шаге вычислений . Спустя 2 итактов после начала вычислений на пятом выходе блока 1 3 синхронизации формирует ся на время и ( и - 1 ) тактов сигнал управления , который при- , водит к переключению коммутаторов 2 5 и 26 . Если до переключения коммута торы 2 5 и 2 6 объединяли регистры 5 5 5 и 6 сдвига в кольцевой регистр н аслов по п разрядов в каждом, то после переключения коммутаторов 2 5 и 26 выход регистра 5 сдвига соединяется с его входом через коммутатор25, а выход регистра 6 сдвига подключается к своему входу через коммутатор 26. После этого в регистре5 сдвига емкостью в о - 1 словопа и разрядов каждое осуществляетсяхранение последовательности величинУ где= 1, 2,. , п - 1, ав регистре 6 сдвига запоминается величина У, , Спустя (п - 1) О тактов после переключения коммутаторов25 и 26 на пятом выходе блока 13синхронизации формируется сигнал управления, возврагающий коммутаторы25 и 26 в исходное состояниеВ этомслучае выход регистра 6 сдвига подключается через коммутаторы 23 и25 к входу регистра 5 сдвига, выходкоторого соединяется через коммутатор 26 к входу регистра 6 сдвига.Регистры 5 и 6 сдвига вновь объединяются в кольцевой регистр сдвигана и слов по о разрядов в каждом.Таким образом осуществляется сдвигпоследовательности величин Ч1-/где ь = 1, 2,и, на одно словов кольцевом регистре сдвига, образованном регистрами 5 и 6,Спустя 3после начала вычислений на (- 1)-м шаге или к моментуначала вычислений для второго звенаинтегро-дифференциального преобразования в регистре 5 сдвига содержитсяпоследовательность величин У, ,Уэ; У; , а в регистре 6 сдви"га - величина ЧВо время первых и тактов вычислений для второго звена интегро-дифференциального преобразования на 1 -мшаге на восьмом и четвертом выходахблока 13 синхронизации формируютсясигналы управления, которые переключают коммутаторы 20, 18, 21, 23 соответственно.Импульсный сигнал четвертого выхода блока 13 синхронизации поступаетна вход п -разрядного распределителя42 импульсов, на первом выходе которого начинает действовать импульс,открывающий первые элементы И 34 и 35.Двоичный код абсолютного значенияЧвыходной величины интегро-диф 1,1Ференциального преобразования первого порядка сдвигается с выхода регистра 1 сдвига через элемент 15 задержки, формирователь 1 1 дополнительного кода и первый элемент И 34 на20 1108445 1 О 55 19первую виходную шину 4 частотногопреобразования интегро-дифференциального вычислителя. Знак выходной величины интегро-дифференциального преобразования первого порядка поступает с второго выхода блока 12 формирования знака через первый элементИ 35 на первую выходную шину 48 знака частного преобразования интегродифференциального вычислителя.Двоичный код выходной величиныпервого звена интегро-дифферен 1,циального преобразования также сдвигается с выхода регистрасдвигачерез элемент 15 задержки, формирователь 11 дополнительного кода, коммутаторы 23 и 25 в регистр 5 сдвига,с выхода которого последовательностьвеличин У 1З1Уп11сдвигается в регистр 6 сдвига. ОКроме этоого, величина У сдви 1 пгается с выхода регистра 1 сдвигачерез элемент 15 задержки, формирова.тель 11 дополнительного кода, коммутаторы 21 и 22 в регистр 3 сдвига в 5качестве входного сигнала Х 2 для,1второго звена интегро-дифференциального преобразования,Величина У , в это время сдви 1 1-1гается с выхода регистра 6 сдвига 30через коммутаторы 27 и 20 в регистр2 сдвига в качестве входного сигнала Хдля второго звена интегро 1дифференциального преобразования,В последующие п тактов с выходарегистра 6 сдвига сдвигается двоичный код величины "У, которыйчерез коммутаторы 27 и 20 записывается в регистр 2 сдвига. Таким образом, в кольцевой регистр сдвига,образованный объединением регистров2 и 3, записываются начальные условия Х ; . , У,, Х, необходимые для выполнения вычислений длявторого звена интегро-дифференциаль 45ного преобразования. В первые 311 тактов вычислений для второго звена интегро-дифференциального преобразования на шестом выходе блока 13 синхронизации формируется сигнал управления, который переключает коммутаторы 28 и 29. В этом случае с выхода регистра 8 сдвига через коммутатор 29 сдвигаются в регистр 4 сдвига двоичные коды коэффициентов А , Вз и С для второго звез 1 а интегро-дифференциального преобразования, а двоичные коды коэффициентов А 1, В, С 1 с выхода регистра 4 сдвига сдвигаются через коммутатор 28 на вход регистра 8 сдвига.Спустя 3 и тактов коммутаторы 28 и29 возвращаются в исходное состояние. Поэтому во время вычислений длявторого звена интегро-дифференциального преобразования в регистре 4сдвига хранятся коэффициенты А , Вз,С, а в регистре 8 сдвига - коэффициенты А, В, С, Аз, Вз, Сз ю А, В 4С., А, В, 1Таким образом, в регистры 2, 3 и4 сдвига записываются двоичные кодыначальных условий и коэффициентов,необходимые для выполнения вычислений второго звена интегро-дифференциального преобразования, которыевыполняются аналогично вычислениямдля первого звена интегро-дифференциального преобразования.После окончания вычислений интегро-дифференциального преобразованиявторого порядка на четвертом выходеблока 13 синхронизации вырабатывается импульс, который проходит навыход второго разряда распределителя 42 импульсов и на первые входывторых элементов И 34 и 35. С выходарегистра 1 сдвига через элемент 15задержки, формирователь 11 дополнительного кода и второй элемент И 34на вторую выходную шину 47 частногопреобразования интегро-дифференциального вычислителя сдвигается двоичный код абсолютного значения 1 Увыходной величины интегро-дифференциального преобразования второго порядка. Одновременно с второго выхода блока 12 формирования знака черезвторой элемент И 35 на вторую выходную шину 48 знака частного преобразования поступает знак выходной велины интегро-дифференциального преобразования второго порядка.Вычисления для всех последующихзвеньев интегро-дифференциальногопреобразования до ь -го звена включительно выполняются аналогичным образом.Вычисления на ( з + 1)-м шаге вычислений и всех последующих для всех11 звеньев интегро-дифференциальногопреобразования осуществляются аналогично,Одновременно с интегро-дифференциальными преобразованиями от перво,го до,в -го порядка интегро-дифференциальный вычислитель формирует согласно выражению (5) величину сложного интегро-дифференциального преобразования. С помощью группы элементов И 41 задают переключательные Функции 5 6 , которые определяют функцию и вид сложного интегро-дифференциального преобразования. Группа элементов И 41 подключает выход первого разряда распределителя 42 импульсов к первому 10 входу элемента ИЛИ 40, если выходная величина интегро-дифференциального преобразования первого порядка входит в состав сложного интегро-дифференциального преобразования, т.е. 151. Аналогично, выход -го.разряда распределителя 42 импульсов подключается элементом И группы 41 к соответствующему 1-му входу элемента ИЛИ 40, если выходная величина интег ро-дифференциального преобразования -го порядка входит в состав сложного интегро-дифференциального преобразования, т.е. 6= 1. На выходе элемента ИЛИ 40 Формируется управляю щий сигнал, который открывает элемент И 36 во время сдвига с выхода регистра 1 сдвига выходных величин 1; звеньев интегро-дифференциального преобразования, соответствующих за- Зо данным переключательным переменным 6 = 1, 8 = 1, 2, ,и . Двоичный код выходной величины У; заданного/6-го звена интегро-дифференциального преобразования под действием импуль 5 сов десятого выхода блока 13 синхронизации сдвигается с выхода регистра 1 сдвига через элемент 15 задержки, элемент И 36 и сумматор 31 на информационный вход ь -разрядного регистра 40 30 сдвига и записывается в него, на" чиная с младшего разряда. Двоичный код выходной величины У+,. следующего заданного, например 7, + % )-го интегро-дифференциального преобразования, поступая аналогичным образом на вход сумматора 3 1, суммируется с двоичным кодом величины ; , кото рый сдвигается с выхода регистра 30 сдвига, и записывается под действием импульсов десятого выхода блока 13 синхронизации вновь в регистр 30 сдвига, где формируется двоичный код выходной величины 2; сложного интег- ро-дифференциального преобразования на 1 -м шаге вычисления.После каждого 1 -го шага вычислений в течение и тактов следующего( 1 + 1)-го шага вычислений интегродифференциальный вычислитель выдаез на выходах 45 и 46 соответственноФ двоичный код абсолютной величины и сигнал знака сложного интегро-дифференциального преобразования (5). Если величина 2 отрицательна, то в1регистре 30 сдвига записан дополнительныйл двоичный код, единичный сигнал знака которого в п -м такте 1-го шага вычислений с выхода сумматора 31 поступает через элемент И 37 на вход триггера 33, устанавливая его в единичное состояние, Единичный сигнал триггера 33 открывает элемент И 38, через который на выход 45 с девятого выхода блока 13 синхронизации поступает единичный сигнал отрицательного знака величины 2; сложного интегро-дифференциального преобразования. Дополнительный двоичный код величины Е;, сдвигаемый с выхода регистра 30 сдвига, преобразуется формирователем 32 дополнительного кода в прямой код абсолютной величиныЕ; сложного интегро-дифференциального преобразования (5) и выдается через элемент И 39 на выход 46 в виде последовательного двоичного кода.Если величина 2, положительна, то триггер 33 сохраняет нулевое состояние, а формирователь 32 дополнительного кода пропускает без изменения прямой двоичный код регистра 30 сдвига на выход 46 интегро-дифференциального вычислителя, В этом случае элемент И 38 закрыт нулевым сигналом прямого выхода триггера 33 и на выходе 45 действует нулевой сигнал положительного знака величины Е; .Блок 12 формирования знака и блок 13 синхронизации работают в процессе вычислений следующим образом.Знак входной величины Х 1 содержится в первом разряде двухраэрядногс регистра 49 сдвига блока 12 формирования знака.Знак выходных величин звеньев интегро-дифференциального преобразования с первого по п -й содержится в регистре 50 сдвига на и + 1 разряд блока 12 формирования знака.Знаки коэффициентов Ар, б щ 1, 2, , и , содержится в регистре 51 сдвига блока 12 Формирования знакаЗнаки коэффициентов Ви С, В1,2, , и , всегда положительны и нетребуют предварительной, установки.1108445 23Генератор 60 тактовых сигналов блока 13 синхронизации вырабатывает последовательность импульсов частотыкоторая делится распределителем 61 импульсов на и раз и затем задерживается элементом 62 задержки на длительность тактового импульса. Последовательность импульсов частоты /и на выходе и -го разряда распре- целителя 61 импульсов (шина 70 третье 4 О го выхода блока 13 синхронизации) определяет п -е такты работы интегродифференциального вычислителя, а последовательность импульсов частоты Е/и на выходе первого разряда рас пределителя 6 1 импульсов (шина 69 второго выхода блока 13 синхронизации) задает первые такты работы.Счетчик 63 выполняет деление на Зъ частоты выходной последовательнос.О ти импульсов элемента 62 задержки. Выходная последовательность импульсов счетчика 63 частоты/3 иделится на и раз делителем 64 частоты, на выходе которого Юормируется последовательность импульсов частоты /3 и з, период следования которых определяет один шаг вычислений.С помощью дешифратора 66, входы которого подключены к выходам триг- ЗО геров счетчика 63, формируются пять последовательностей импульсов заданной длительности и периода следования, которые необходимы для управления работой интегро-дифференциально 35 го вычислителя (шины 71-75 четвертого - восьмого выходов блока 13 синхронизации соответственно).Каждый шаг вычислений в интегродифференциальном вычислителе начинается в момент генерации импульсов на выходе делителя 64 частоты блока 13 синхронизации, который устанавливает триггер 65 в единичное состояние и сдвигает на один разряд инфор 45 мацию о знаке входной величины в регистре 49 сдвига блока 12 формирования знака. В результате сдвига в первый разряд регистра 49 записывается знак входной величины на текущем-м шаге, сигнал которого дейст 50 вует на шине входа 43 знака входной информации вычислителя, а знак входной величины на предыдущем ( 1 - 1)-м шаге сдвигается иэ первого разряда во второй разряд регистра 49 сдвига.На прямом выходе триггера 65 (шина 76 девятого выхода блока 13 синхронизации) формируется сигнал, который 24с помощью коммутаторов 52 и 53 подключает выходы регистра 49 или 50сдвига к входам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 56 и коммутатора 54 соответственно. Коммутатор 54 по сигналамтрехканального распределителя 55импульсов опрашивает последовательночерез каждые,Ъ тактов выходы элемен"та ИСКЛЮЧАЮЩЕЕ ИЛИ 56, регистра 50сдвига и коммутатора 53. На выходеэлемента ИСКЛ 10 ЧАЮЩЕЕ ИЛИ 56, входыкоторого подключены к выходу регистра 51 сдвига и через коммутатор 52к выходам регистров 49 и 50 сдвига,формируется сигнал знака произведения А Х; или АЕХ,;= А 1 У-12, 3. иНа выходе и -го разряда регистра50 сдвига формируется сигнал знакапроизведения ВрУ , 1 1, 2,1н, а на выходе коммутатора 53 - сигфнал знака произведения С Х илиСХ; =СУ 1, 6 2, 3,у и еТаким образом, на выходе коммута"тора 54 (шина 58 первого выхода блока 12 формирования знака) каждыетактов последовательно во временидействуют на сигналы знаков произвении А Х 1 1 В Хи С)(ф1, 2, , л,На выходной шине 59 второго выхода блока 12 формирования знака действует сигнал выхода первого разрядарегистра 50 сдвига, в который с выхода сумматора 9 по шине 57 записывается и -й знаковый разряд выходныхвеличин Ч , где 6 = 1, 2,всех звеньев интегро-дифференциального преобразования.Выходная последовательность импульсов генератора 60 тактовых сигналов, действующая на шине 77 десятоговыхода блока 13 синхронизации, осуществляет синхронизацию сдвига информации в регистрах 1-8 и 30 сдвига,Одиночный импульс на шине 78 один"надцатого выхода блока 13 синхронизации формируется генератором 67 одиночных импульсов, запуск которогоосуществляется коммутатором 68, выполненным, например, в виде кнопочногопереключателя.Последовательность импульсов,действующая на шине 79 двенадцатоговыхода блока 13 синхронизации черезкаждые и тактов, поступает на входысброса сумматоров 9 и 31, а такжеформирователей 10, 11 и 32 дополни1108445 Составитель А.ЧекановТехред Т.Дубинчак Корректор 0,Тиго едак ексеенк аэ 5866/ Тираж 699Государственногелам изобретенийсква, Ж, Рау11 ОЯДД 5 тов И третьей группы соединены с входами задания порядка преобразования вычнслителя,а их вйходы,подключенык входам элемента ИЛИ,3шестой, седьмой и восьмой регистры сдвига и пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый и двенадцатый коммутаторы, причем первый вход пятого коммутатора соединен с выходом второго формирователя дополнительного кода и с первым входом шестого коммутатора, втоРой вход - с четвертым выходом блока синхронизации, с вторым входом второго коммутатора, с первым входом седьмого коммутатора, третий вход - с выходом пятого регистра сдвига, с первым входом восьмого коммутатора и с первым входом девятого коммутатора, а выход - с первым входом десятого коммутатора, второй вход которого подключен к пятому выходу блока синхронизации и к второму входу девятого коммутатора, третий вход которого соединен с третьим входом десято- ного коммутатора и с выходом шестого регистра сдвига, информационный вход которого подключен к выходу десятого коммутатора, выход девятого коммутатора соединен с информационным входом пятого регистра сдвига, шестой выход блока синхронизации подключен к первому входу одиннадцатого коммутатора и к первому входу двенад-, цатого коммутатора, второй вход которого соединен с вторым входом одиннадцатого коммутатора и с выходом седьмого регистра сдига, информационный вход которого подключен к второ му входу первого элемента И и к выходу одиннадцатого коммутатора, третий вход которого соединен с третьим входом двенадцатого коммутатора и с выходом восьмого регистра сдвига, информационный вход которого подключен к выходу двенадцатого коммутатора, седьмой выход блока синхронизации соединен с третьим входом первого коммутатора, восьмой выход блока синхронизации соединен с первым входом третьего коммутатора, второй вход которого подключен к выходу третьего регистра сдвига, информационный вход которого соединен с выходомседьмого коммутатора, второй входкоторого подключен к выходу второгорегистра сдвига, а третий вход - квыходу шестого коммутатора, второй 5вход которого соединен с входом абсолютной величины вычислителя, а третийвход - с девятым выходом блока синхронизации и с вторыми входами четвертого и восьмого коммутаторов, третьивходы которых подключены к выходучетвертого регистра сдвига, выходвосьмого коммутатора соединен с третьим входом третьего коммутатора13.Недостатками известного интегродифференциального вычислителя являются ограниченные функциональные возможности, которые не позволяют Формировать сложные интегро-дифференциальныепреобразования, составленные из интег-фро-дифференциальных преобразований спервого по и -й порядок,Цель изобретения - расширение функциональных возможностей за счет вы 6числения интегро-дифференциальных пре образований и-го порядка.Указанная цель достигается тем,что в интегро-дифференциальный вычислитель введены девятый регистр сдвига, второй сумматор, третий формиро- ЗОватель дополнительного кода, и -разрядный распределитель импульсов, второй триггер, первая, вторая и третьягруппы элементов И, третий, четвертый, пятый и шестой элементы И и элемент ИЛИ, причем четвертый выход блока синхронизации соединен с входомП-разрядного распределителя импульсов,первые входы 1-х ( 1 = 1, и ) элемен",тов И первой, второй и третьей группсоединены соответственно с выходом1-го разряда распределителя импульсов,вторые входы элементов И первой и второй групп соединены соответственнос выходом второго формирователя допол нительного кода и вторым выходом блока формирования знака, выход элементаИЛИ соединен с первым входом третьего элемента И, второй вход которогосоединен с выходом элемента задержки,выход третьего элемента И соединен спервым входом второго сумматора, второй вход которого соединен с выходомдевятого регистра сдвига и с информационным входом третьего формирователя дополнительного кода, выход второго сумматора соединен с информацион-.ным входом девятого регистра сдвигаи с первым входом четвертого элемента И, выход которого соединен с входом установки в "1" второго, триггера, третий выход блока синхронизации соединен с вторым входом четвертого элемента И и с входом установки в "0" второго триггера, прямой выход которо,го соединен с первым входом пятого элемента И и с управляющим, входом ,третьего Формирователя дополнительно. го кода, выход которого соединен с первым входом шестого элемента И, девятый выход блока синхронизации соединен с вторыми входами пятого и шестого элементов И, выходы которых являются соответственно выходами общего знака и общего преобразования вы числителя, выходы частного преобразования с первого по ь -й порядок вычислителя и выходы знака частных преобразований вычислителя соединенЫ соответственно с выходами элементов И первой и второй групп, вход синхро. низации девятого регистра сдвигаГсоединенс десятым выходом блока синхронизации, одиннадцатый выход которого соединен с входом управления дечятого регистра сдвига, двенадцатый выход блока синхронизации соединен с входом сброса второго сумма тора и третьего Формирователя дополнительного кода, входы элементов И третьей группы соединены с входами задания порядка преобразования вычислителя, а их выходы подключень 1 к входам элемента ИЛИ.На Фиг. 1 изображена структурная схема интегро-дифференциального вычислителя на фиг, 2 . - структурные схемы блока Формирования знака и блока синхронизации.Интегро-дифференциальный вычислитель содержит регистры 1-8 сдвига, сумматор 9, Формирователи 10 и 11 дополнительного кода, блок 12 формирования знака, блок 13 синхронизации, 5 триггер 14, элемент 15 задержки, элементы И 16 и 17, коммутаторы 18-29, регистр 30 сдвига, сумматор 31, формирователь 32 дополнительного кода, 5 -триггер 33, группы элементов И 34 и 35, элементы И 36-39, элемент ИЛИ 40, группу элементов И 4 1, и -разрядный распределитель 42 импульсов, вход 43 знака входной информации вычислителя, вход 44 абсолютной величины вычислителя, выход 45 общего знака вычислителя, выход 4 б общего преобразования вычислителя, группу выходов 47 частного преобра 1108445зования вычислителя и группу выходов 48 знака частных преобразований вычислителя.Выход регистра 1 сдвига соединен с входом элемента 15 задержки и с вторым входом коммутатора 19, выход и первый вход которого соединены соответственно с первым входом коммутатора 18 и с выходом элемента 15 задержки. оВыход регистра 2 сдвига соединен с вторым входом коммутатора 21, выход которого соединен с информацион" ным входом регистра 3 сдвига, информационный вход регистра 2 сдвига сое динен с вторым входом элемента И 17 и с выходом коммутатора 20, второй вход которого подключен к выходу регистра 3 сдвига. Информационный вход регистра 4 сдвига подключен к выходу 20 коммутатора 29, второй и третий вхо" ды которого соединены соответственно с выходом регистра 4 сдвига и с выходом регистра 8 сдвига.Выход регистра 5 сдвига подключен к третьему входу коммутатора 26, выход которого соединен с информационным входом регистра 6 сдвига. Информационный вход регистра 7 сдвига подключен к выходу коммутатора 24, первый и третий входы которого соединены соответственно с входом 44 абсолютной величины вычислителя и с выходом ре" гистра 7 сдвига,Информационный вход регистра 8 сдвига подключен к выходу коммутато" ра 28, второй и третий входы которого соединены соответственно с выходом регистра 4 сдвига и с выходом регистра 8 сдвига.4 ОИнформационный вход регистра 1 сдвига подключен к выходу сумматора 9, первый и второй входы которого соединены соответственно с выходом коммутатора 18 и с выходом Формирователя45 10 дополнительного кода, первый и второй входы которого подключены соответственно к выходу элемента И 16 и к первому выходу блока 12 формирования знака, третья группа входов которого соединена с первой группой выходов блока 13 синхронизации.Второй и первый входы формирователя 11 дополнительного кода соединены соответственно с выходом элемента 15 задержки и с вторым выходом блока 12 Формирования знака, второй и первый входы которого подключены соответственно к входу 43 знака входной информации вычислителя и к выходу сумматора 9.Выход формирователя 11 дополнительного кода соединен с первыми входами коммутаторов 22 и 23.Блок 13 синхронизации соединен . седьмым входом с третьим входом коммутатора 19,восьмым выходом - с первым входом коммутатора 20, четвертым выходом - с вторыми входами коммутаторов 18 и 23 и с первым входом коммутатора 21, вторым выходом - с первым входом элемента И 17, выход которого подключен к первому входу триггера 14. Второй вход и прямой выход триггера 14 соединены соответственно с третьим выхо- дом блока 13 синхронизации и с первым входом элемента И 16, второй вход которого подключен к выходу коммутатора 29.Выход коммутатора 23 подключен ц первому входу коммутатора 25, выход и третий вход которого соединены соответственно с информационным входом и выходом регистра 5 сдвига, Выход регистра 6 сдвига подключен к третьему входу коммутатора 23, к первому входу коммутатора 26 и к первому входу коммутатора 27, выход и третий входы которого соединены соответственно с третьим входом коммутатора 20 и с выходом регистра 7 сдвига.Третий вход коммутатора 21 подключен к выходу коммутатора 22, второй вход которого соединен с входом 44 абсолютной величины вычислителя.Девятый выход блока 13 синхронизации подключен к вторым входам коммутаторов 24 и 27 и к третьему входу коммутатора 22. Пятый выход блока 13 синхронизации соединен с вторыми входами коммутаторов 25 и 26. Шестой выход блока 13 синхронизации соединен с первыми входами коммутаторов 28 и 29. Четвертый выход блока 13 синхронизации соединен с входом Ь -разрядного распределителя 42 импульсов, выходы которого соединены через группу элементов И 4 1 и с входами элемента ИЛИ 40. Первые входы первого- и-го элементов групп элементов И 34 и 35 соединены соответственно с вы ходами первого " п -го разрядов распределителя 42 импульсов, Вторые входы групп 34 и 35 элементов И соединены соответственно с выходом формирователя 11 дополнительного кода и вторым выходом блока 12 формирования знака. Выход элемента ИЛИ 40 соединен с первым входом элемента И 36, второй вход которого соединен с выходом элемента 15 задержки, 5 Выход элемента И 36 соединен с первым входом сумматора 31, второй вход которого соединен с выходом регистра 30 сдвига и первым входом формирователя 32 дополнительного кода.Вькод сумматора 31 соединен с информационным входом регистра 30 сдвига и первым входом элемента И 37, выход которого соединен с первым входом триггера 33. Третий выход блока 15 13 синхронизации соединен с вторыми аходами элемента И 37 и триггера 33, прямой выход которого соединен с первым входом элемента И 38 и с вторым входом формирователя 32 дополни тельного кода, выход которого соединен с первым входом элемента И 39.Девятый выход блока 13 синхронизации соединен с вторыми входами элементов4И 38 и 39, вьмоды которых являются 25 соответственно выходами общего знака 45 и преобразования вычислителя 46, вьмоды 47 частного преобразования с первого по и -й порядок и выходы 48 знака частных преобразова- зО ний которого соединены соответственно с выходами групп элементов И 34 и 35. Входы синхронизации регистров 1-8 и 30 сдвига соединены с входом синхронизации элемента 15 задержки и с десятым выходом блока 13 синхронизации, одиннадцатый выход которого соединен с входами управления регистров 1, .4, 5, 7, 8 и 30 сдвига, Двенадцатый выход блока 13 синхрониза О ции соединен с входами сброса сумматоров 9 и 31 формирователей 10, 1 1 и 32 дополнительного кода. Блок 12 формирования знака (фиг,2)15 содержит три регистра 49-51 сдвига, три коммутатора 52-54, распределитель 55 импульсов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 56, входы 43 и 57, выходы 58 и 59Блок 13 синхронизации содержит генератор 60 тактовых сигналов, рас 50 пределитель 61 импульсов, элемент 62 задержки, счетчик 63, делитель 64 частоты, 5 -триггер 65, дешифратор 66, генератор 67 одиночных импульсов, коммутатор 68 и выходы 69-795Вход 43 знака входной информации вычислителя подключен к информационному входу двухразрядного регистра 49 сдвига, шина сдвига которого сое динена с выходом делителя 64 частоты,Информационный вход регистра 50сдвига, содержащего и + 1 разряд,соединен с шиной 57 с выходом сумма"тора 9. Выход регистра 51 сдвига емкостью в в разрядов соединен со своим информационным входом и с первымвходом элемента 56 ИСКЛЮЧАЮЩЕЕ ИЛИ,второй вход которого подключен к вы.ходу коммутатора 52, Выходы первыхразрядов регистров 49 и 50 сдвигасоединены с первым и вторым входамикоммутаторов 53 соответственно. Выходы второго разряда регистра 49 сдви"га и ь + 1-го разряда регистра 50сдвига соединены с первым и вторымвходами коммутатора 52 соответственноПервый, второй и третий входы коммутатора 54 соединены соответственнос выходом коммутатора 53, с выходоми-го разряда регистра 50 сдвига и свыходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 56.Вход распределителя 55 импульсов соединен с выходом элемента 62 задержки. Три управляющих входа коммутатора 54 соединены с соответствующимитремя выходами распределителя 55 импульсов,Выход коммутатора 54 подключен квыХодной шине 58, которая являетсяпервым выходом блока 12 формирования1"знака,Выход первого разряда регистра 50 сдвига соединен с выходной шиной 59, которая является вторым выходом блока 12 формирования знака. Входы управления вводом информации регистров 49-51 сдвига соединены с вькодом генератора 67 одиночных импульсов.Выход генератора 60 тактовых сигналов блока 13 синхронизации подклю" чен к шине 77 и к входу и -разрядного распределителя 61 импульсов, выход и -го разряда которого соединен с входом элемента 62 задержки, с первым входом триггера 65 и с выход. ной шиной 70. Выход первого разряда распределителя 61 импульсов соединен с шиной 69.Выход элемента 62 задержки соединен с входом счетчика 63 и с выходной шиной 79, Выход переполнения счетчика 63, имеющего коэффициент перерасчета Эи, соединен с входом делителя 64 частоты и с шинами сдви 9 1108га регистров 50 и 51 сдвига блока 12формирования знака.Выход делителя 64 частоты, имеющего коэффициент деления , соединен с вторым входом триггера 65, 5прямой выход которого подключен квыходной шине 76 и к третьим входамкоммутаторов 52 и 53 блока 12 формирования знака.Выходы триггеров счетчика 63 подключены к входам дешифратора 66, выходы которого соединены с выходнымишинами 71-75.блока 13 синхронизации.Выход делителя 64 частоты соединенс тактовым входом генератора 67 одиночных импульсов, выход которого соединен с шиной 78, а вход запуска через коммутатор 68 " с нулевой шинойвычислителя.Выходные шины 69-79 являются вторым - двенадцатым выходами блока 13синхронизации соответственно,Интегро-дифференциальный вычислитель реализует в цифровой Форме передаточную функцию ь -й степени видаВ(Р 1=П ю (Р), (11где ВЕ (Р) - передаточная функция -гозвена интегро-дифференциального преобразования,реализуемого из П звеньев.Каждое Г-е звено с интегро-дифференциальным преобразованием Ф Е(Р)интегро-дифференциальный вычислительреализует согласно рекуррентному соотношению гДе У 1 Е и УЕ 1 - значениЯ выхоДнойвеличины для 1-гозвена интегро-дифференциального преоб 45раэования на ,1 -м и( 1 " 1)-м шагах вычислений соответственно,К Е, и ХЕ, - значения входной вееличины для С-го зве Она интегро-дифференциального преобразо"вания на 1-м и ( 1 -1)-м шагах вычислений со ответ стве нно;55АЕ, ВЕ и СЕ - постоянные коэффициенты, от значениякоторых зависит вид интегро-. дифференциального преобразования % Е(Р) согласнотаблице,Заданное интегро-дифференциальноепреобразование высокого порядка представляется согласно выражению (1) ввиде произведения и элементарных интегро-дифференциальных звеньев ВЕ(Р),для каждого иэ которых производятпредварительный расчет постоянныхкоэффициентов АЕ, ВЕ, Спо формуламтабл. 1, где К - коэффициент усиления, Т, Т 1, Т, - постоянные времени1 - шаг последовательного преобразования входной величины в выходную,который выбирается из условия заданной точности,Все звенья интегро-дифференциального преобразования на каждом шагевычислений обрабатываются последовательно с первого до последнего. Входной величиной для каждого звена интегро-дифференциального преобразования, кроме первого, является выходная величина предыдущего звена, т.еХ = 1Е Е,(з 1Х, =Уе(1- 1 е-11 = г, 3, , И,Интегро-дифференциальный вычислитель оперирует с двоичными переменными, для которых соотношение (2) принирает видгде У . . - двоичная переменнаяе,1-1, 11-го разряда величиные; 1,Х . . и Х .:, - двоичные переменные(вида Щр(Р) согласнотаблицей, входящих винтегро-дифференциальное преобразование,равное количеству разрядов представлениядвоичных переменных.Интегро-дифференциальный вычислитель дополнительно формирует на каждом шаге вычислений выходную величину сложного интегро-дифференциального преобразования согласно выраже- нию-м шагезначения выходной величиныедля В-го звена интегро-дифференциального преобразоваОния 1-го порядка на 1-мшаге;6 - заданная переключательнаяпеременная, которая принимает значение "0" либо "1".Начальная установка регистров 1, 4, 5, 7, 8 и 30 сдвига осуществляется либо от цифровой вычислительной машины, либо от устройств автоматического ввода информации по одиночному импульсу, вырабатываемому на, одиннадцатом выходе блока 13 синхро" низации, Начальная установка регистров 2, 3 и 6 выполняется путем вво 4да информации через коммутаторы 20, 21 и 26 от регистров 7, 1 и 5 сдвига соответственно. Начальное расположение информации в регистрах 1-8 сдвига соответствует расположению информации в конце некоторого (- 1)-го 0 шага вычислений.Если двоичные коды коэффициентов А, Ви С, а также начальные условия входной величины и выходных величин всех звеньев интегро-дифферен циального преобразования постоянны и не могут измениться в процессе использования интегро-дифференциального вычислителя, то шины ввода информации в соответствующие разряды 40 регистров 1-8 и 30 сдвига могут быть постоянно соединены с шинами логического нуля или единицы вычислителя в зависимости от значения вводимого кода. 45Интегро-дифференциальный вычисли" тель работает циклическим образом, выполняя последовательно интегродифференциальное образование над двоичным кодом входного сигнала сог ласно выражению (4).В конце (- 1)-го вага вычисле" ний в регистре 1 сдвига на в. - 1 разряд, который дополняется элементом 15 задержки на такт до,я -разрядов, содержится и -разрядный двоичный код выходной величины У;, вычисленной на ( 1 - 1)-м шаге, В регистре 8 сдвига емкостью в 3(- 1) слов,каждое из которых содержит и двоичныхразрядов, записаны последовательнодвоичные коды коэффициентов А, В,С, где , = 1, 2, , и " 1 обозначает порядковый номер звена интегродифференциального преобразования. Врегистре 4 сдвига емкостью в трислова по п разрядов каждое записаныдвоичные коды коэффициентов Ап, В,С последнего по порядку и -го звенаинтегро-дифференциального преобразования.В регистре 5 сдвига емкостью в1 слово по и разрядов каждое содержатся двоичные коды абсолютныхзначений выходных величин звеньев интегро-дифференциального преобразования с первого по п - 1, вычисленныена предыдущем ( 1 - 1)-м шаге вычислений. В регистре 6 сдвига емкостьюв одно слово на н разрядов содержится выходная величина последнего П -гозвена интегро-дифференциального преобразования.Регистр 2 сдвига на й - 1 разряди регистр 3 сдвига на 2 и разрядовобеспечивают в процессе вычисленийхранение двоичных кодов Х ; .1Е,-1 ЕХВ регистре 7 сдвига на и разрядовхранится абсолютное значение входнойвеличины Х; 1 интегро-дифференциального вычислителя от предыдущего шагавычислений, знак которой хранится вблоке 12 формирования знака,Каждый шаг вычислений начинаетсяв момент генерации на девятом выходе блока 13 синхронизации управляющего сигнала длительностью в и тактов,который переключает коммутаторы 22У24 и 27. Одновременно на восьмом выходе блока 13 синхронизации вырабаты"вается управляющий сигнал длительнос"тью 2 п тактов, действующий на коммутатор 20, а на четвертом выходеблока 13 синхронизации вырабатывается управляющий сигнал длительностьюи тактов, действующий на коммутаторы18, 21 и 23. На шестом выходе блока13 синхронизации в это время формируется управляющий сигнал длительнос"тью в Зп тактов, который переключаеткоммутаторы 28 и 29.Вход 44 абсолютной величины вычислителя подключается коммутаторами 21 и 22 к информационному входу реистра 3 сдвига и коммутатором. 24 к13 110844информационному входу регистра 71 сдвига, выход которого коммутаторами 20 и 27 подключается к информационному входу регистра 2 сдвига. Двоичный код абсолютной величины входного сиг нала на 1-м шаге вычислений, поступающий последовательно во вРемени, начиная с младших разрядов, по входу 44 абсолютной величины вычислителя записывается под действием импуль сов десятого выхода блока 13 синхронизации за и тактов в регистр 3 сдвига, емкость которого составляет 2 й разрядов. Одновременно с этим двоичный код абсолютной величины15 входного сигнала на предыдущем (1 -1)-м шаге вычислений, который хранится в регистре 7 сдвига, переписывается под действием импульсов десятого выхода блока 13 синхронизации с выхода регистра 7 сдвига через коммутаторы 27 и 20 в регистр 2 сдвига, имеющий емкость в и - 1 разряд. По мере освобождения старших раз рядов регистра 7 сдвига в них записывается через коммутатор 24 двоичный код входного сигнала на 1 -м шаге, действующий на входе 44 абсолютной величины вычислителя, Сигнал, поступающий по входу 43 знака входной ин- ЗО формации вычислителя, записывается в блок 12 формирования знака.Коммутатор 18 разрывает на и тактов цепь циркуляции двоичного кода регистра 1 сдвига через сумматор 9. з 5 Коммутаторы 23 и 25 подключают выход формирователя 11 дополнительного кода к информационному входу регистра 5 сдвига, выход которого подключается коммутатором 26 к информацион ному входу регистра 6 сдвига емкостью в и разрядов.Прямой или дополнительный код выходной величины интегро-дифференциального вычислителя на ( 1 - 1)-м45 шаге сдвигается с выхода регистра 1 сдвига через элемент 15 задержки, формирователь 11 дополнительного кода и коммутаторы 23 и 25 в регистр 5 сдвига, с выхода которого в это время сдвигается двоичный код абсолют ного значения выходной величины пер вого звена интегро-дифференциального преобразования на ( 1 - 1)-м шаге вычислений. Формирователь 11 дополни тельного кода по сигналам второго выхода блока 12 формирования знака преобразует дополнительный код регист 14ра 1 сдвига в прямой код, прямой код регистра 1 сдвига пропускает беэ изменения. Таким образом, в регистр.5 сдвига записывается прямой код абсолютного значения выходной величины интегро-дифференциального преобразования п -го порядка,Если с выхода регистра 7 сдвига сдвигается в младшем разряде входной величины на ( 1 - 1)-м шаге единичный сигнал, который через коммутаторы 20 и 27 поступает на второй вход элемента И 17, то сигнал второго выхода блока 13 синхронизации поступает через элемент И 17 на первый вход триггера 14, который переходит из нулевого состояния в единичное. В этом случае на прямом выходе триггера 14 формируется сигнал, который открывает элемент И 16. В это время с выхода регистра 8 сдвига сдвигается,начиная с младших разрядов, двоичный код коэффициента А , который1 фзаписывается через коммутатор 29 в регистр 4 сдвига и через элемент И 16, формирователь 10 дополнительного кода и сумматор 9 в регистр 1 сдвига. Формирователь 10 дополнитель" ного кода управляется сигналом первого выхода блока 12 формирования знака так, что при положительном знаке произведения А, М;двоичный код коэффициента А 1 проходит без измене" ния, а при отрицательном знаке премобразуется в дополнительный код.Спустя п тактов после начала вычислений на 1-м шаге на четвертом и девятом выходах блока 13 синхронизации начинают действовать сигналы управления, которые переводят коммутаторы 18, 21, 23 и 24,22, 27 соответственно в исходное положение.В этом случае коммутатор 18 подключает выход коммутатора 19 к первому входу сумматора 9, коммутатор 21 подключает выход регистра 2 сдвига к входу регистра 3 сдвига, коммутатор 23 подключает выход регистра б сдвига к первому входу коммутатора 25, коммутатор 22 подключает выход формирователя 11 дополнительного кода к третьему входу коммутатора 21, коммутатор 24 подключает выход регистра 7 сдвига к его информационному входу, коммутатор 27 подключает выход регистра 6 сдвига к третьему входу коммутатора 20. После этого выходной сигнал первого звена на( - 1)-м шаге сдвигается с выхода регистра 6 сдвига через коммутаторы 27 и 20 в регистр 2 сдвига, с выхода которого через коммутатор 21 в регистр 3 сдвигается И - 1 разряд 5 двоичного кода входной величины на (1 - 1)-м шаге. Если в младшем разряде двоичного кода УсодержитсяФединичный код, то единйчный сигнал с выхода регистра 6 сдвига через ком" 10 мутаторы 27 и 20 поступает на второй вход элемента И 17, на первом входе , которого действует сигнал второго выхода блока 13 синхронизации. В этом случае триггер 14 устанавливает ся в единичное состояние выходным сигналом элемента И 17. Если в младшем разряде величины (содержится нулевой код, то триггер 14 устанавливается в нулевое состояние сиг- Ы налом третьего выхода блока 13 синхро. низации. При единичном состоянии триггера 14 сигнал его прямого выхода открывает элемент И 16. Двоичный код коэффициента В сдвигается с вы 1хода регистра 8 сдвига через коммутатор 29 в регистр 4 сдвига, а также через элемент И 16 и формирователь 10 дополнительного кода на второй ,вход сумматора 9, на первый вход ко торого в это время с выхода регистра 1 сдвига через элемент 15 задержки и коммутаторы 18 и 19 сдвигается двоичный код коэффициента А, Резуль. тат суммирования коэффициентов А и1 В записывается с выхода сумматора 9 в регистр 1 сдвига. Формирователь 10 дополнительного кода в это время управляется сигналом знака произведения В, У, 1 1 у действующим на первом 401выходе блока 12 формирования знака,Спустя 2 й тактов после начала . вычислений на 1 -м шаге на восьмом выходе блока 13 синхронизации формируется управляющий сигнал, который возвращает коммутатор 20 в исходное состояние. Коммутатор 20 подключает выход регистра 3 сдвига к информационному входу регистра 2 сдвига, выход которого подключен коммутато ром 21 к информационному входу регистра 3 сдвига. В результате этого регистры 2 и 3 сдвига объединяются в кольцевой регистр сдвига на Зь - 1 разряд.В момент объединения регистров 2 и 3 сдвига с выхода регистра 3 сдвига сдвигается, начиная с младших разрядов двоичный код входной величинына 1 -м шаге. Если в младшемразряде величины К, содержится единичный код, то единичный сигнал свыхода регистра 3 сдвига через коммутатор 20 поступает на первый входэлемента И 17, открывая его, Сигналвторого выхода блока 13 синхронизации проходит через элемент И 17,устанавливая триггер 14 в единичноесостояние. Если в младшем разрядевеличины К; содержится нулевой код,то триггер 14 сбрасывается в нулевоесостояние сигналом третьего выходаблока 13 синхронизации,В случае единичного состояниятриггера 14 сигнал его прямого выхода открывает элемент И 16. В это время с выхода регистра 8 сдвига черезкоммутатор 29 сдвигается двоичныйкод коэффициента С , который записывается в регистр 4 сдвига и черезэлемент И 16, формирователь 10 дополнительного кода поступает на второйвход сумматора 9. Формирователь 10дополнительного кода в это время управляет сигналами произведения С Хфдействующим на первом выходе. блока12 формирования знака. Одновременнона первый вход сумматора 9 с выходарегистра 1 сдвига сдвигается черезэлемент 15 задержки и коммутаторы18 и 19 двоичный код суммы коэффициентов А и В 1. Результат суммирования (А 1 + В + С) записывается с выхода сумматора 9 в регистр 1 сдвига.Таким образом, спустя 3 тактовпосле начала вычислений в регистресдвига формируется двоичный код суммыпроизведений первых разрядов величийУ;Х; на двоичные коды коэффициентов А 1, В 1, Ссоответственно. Двоичные коды коэффициентов А1 Ф В, С последовательно переписываются под действием импульсов десятого выхода блока 13 синхронизации с выхода регистра 8 сдвига через коммутатор 29 в регистр 4 сдвига, с выхода которого двоичные коды коэффициентов ААн В 11, С переписываются через комму- . татор 28 в регистр 8 сдвига.В кольцевом регистре сдвига, образованном объединением регистров 2 и 3 сдвига, емкостью в 3 и - 1 разряд за Зп тактов происходит сдвиг на один разряд так, что с сигналами второго выхода блока 13 синхронизации, дейст

СмотретьЗаявка

3569081, 25.03.1983

ИНСТИТУТ ЭЛЕКТРОДИНАМИКИ АН УССР, ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ ИМ. В. М. ГЛУШКОВА

БАРАНОВ ГЕОРГИЙ ЛЕОНИДОВИЧ, БАРАНОВ ВЛАДИМИР ЛЕОНИДОВИЧ

МПК / Метки

МПК: G06F 7/64

Метки: вычислитель, интегро-дифференциальный

Опубликовано: 15.08.1984

Код ссылки

<a href="https://patents.su/16-1108445-integro-differencialnyjj-vychislitel.html" target="_blank" rel="follow" title="База патентов СССР">Интегро-дифференциальный вычислитель</a>

Предыдущий патент: Устройство для решения интегральных уравнений фредгольма

Следующий патент: Табличный процессор

Случайный патент: Сборно-разборный ящик