Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1325477

Авторы: Мельников, Никольский, Сперанский, Тимонькин, Ткаченко, Улитенко, Харченко

Текст

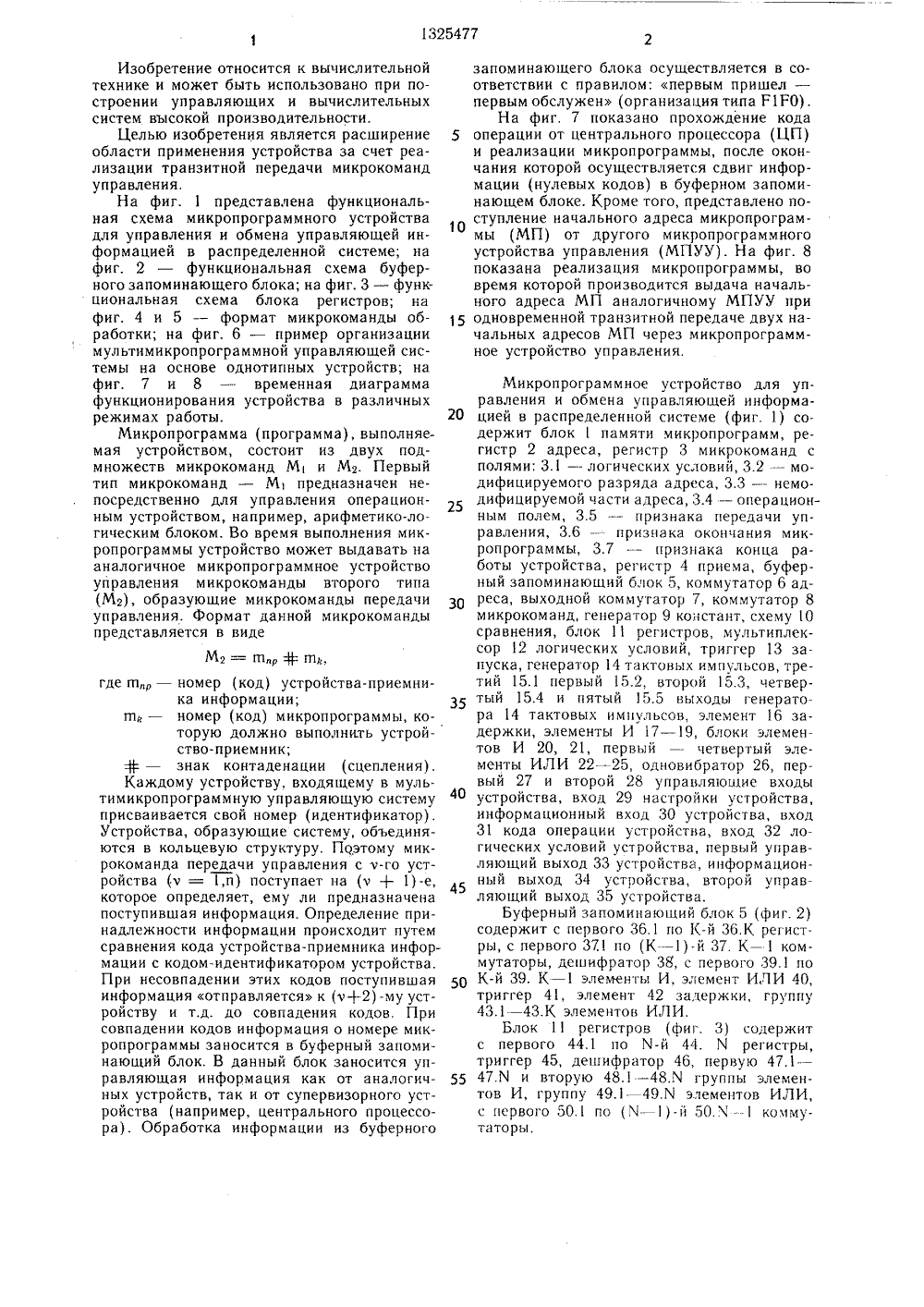

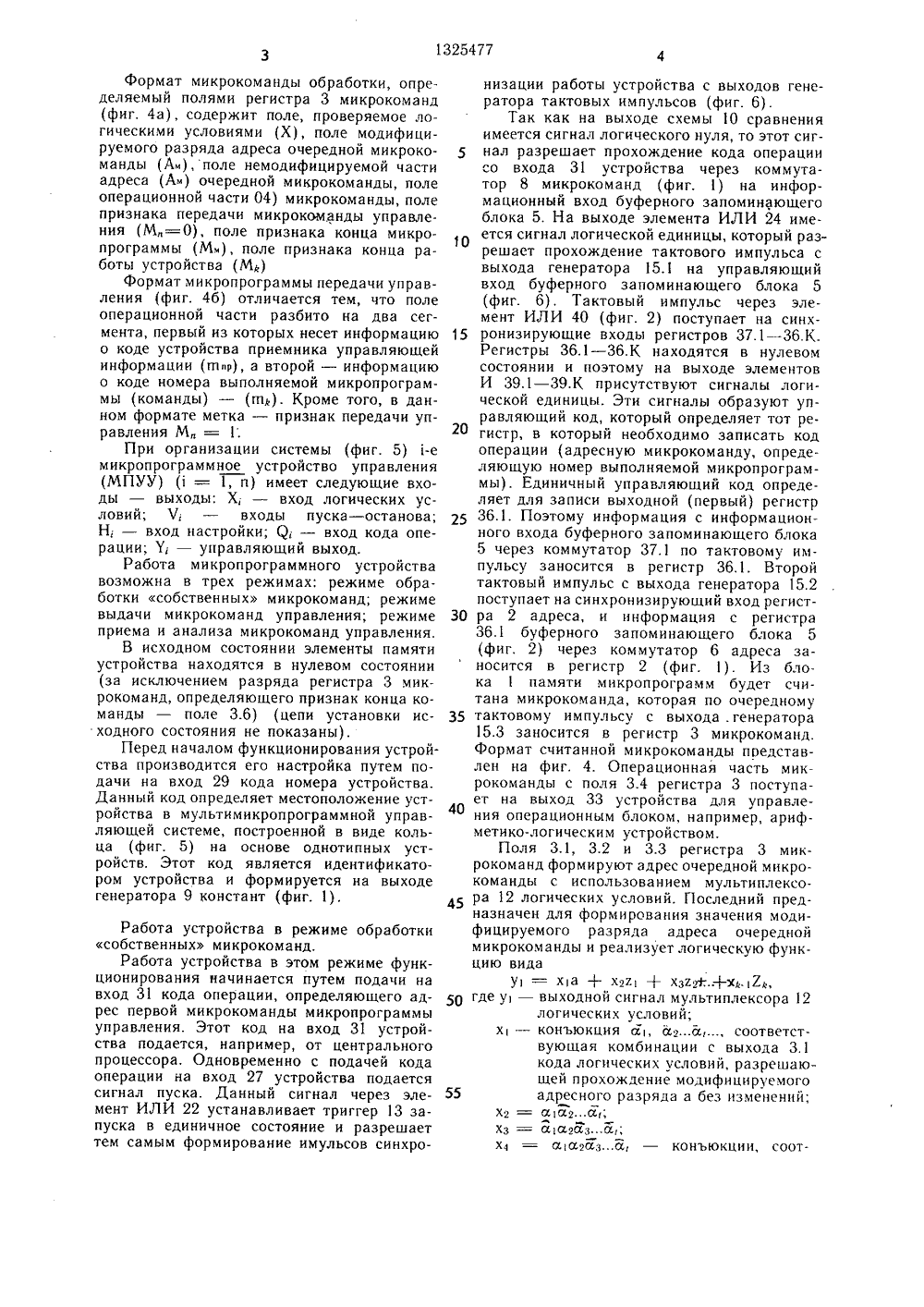

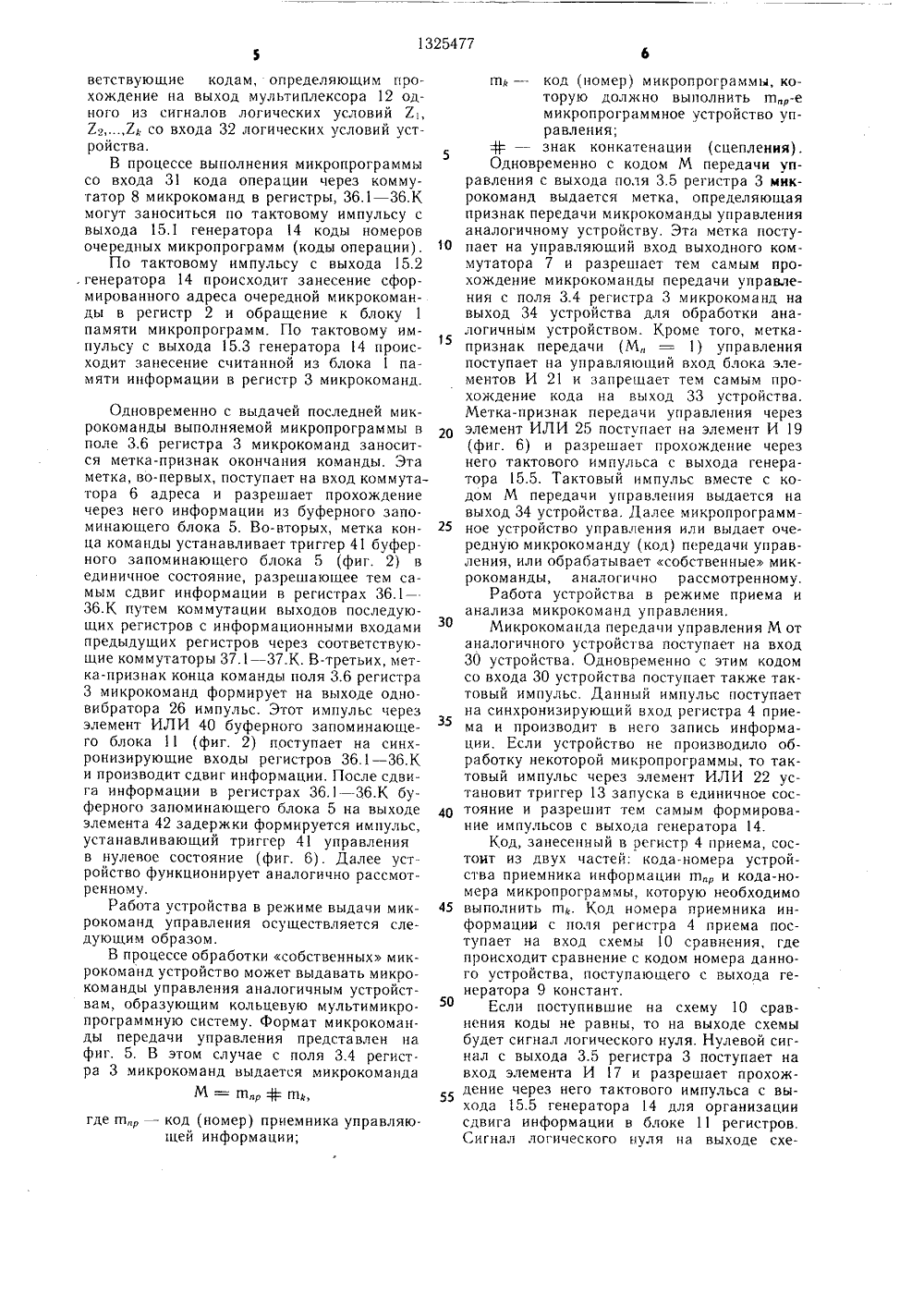

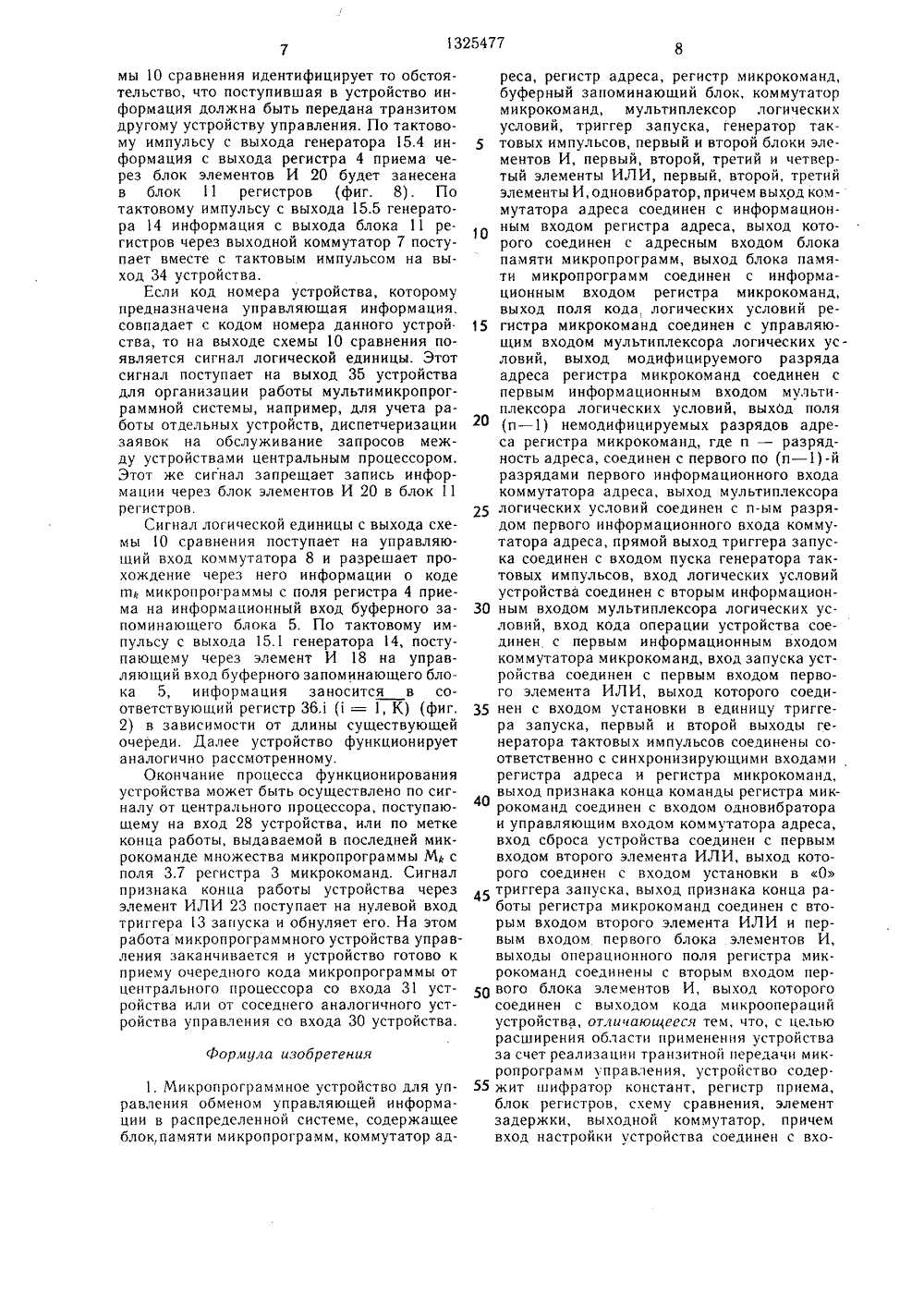

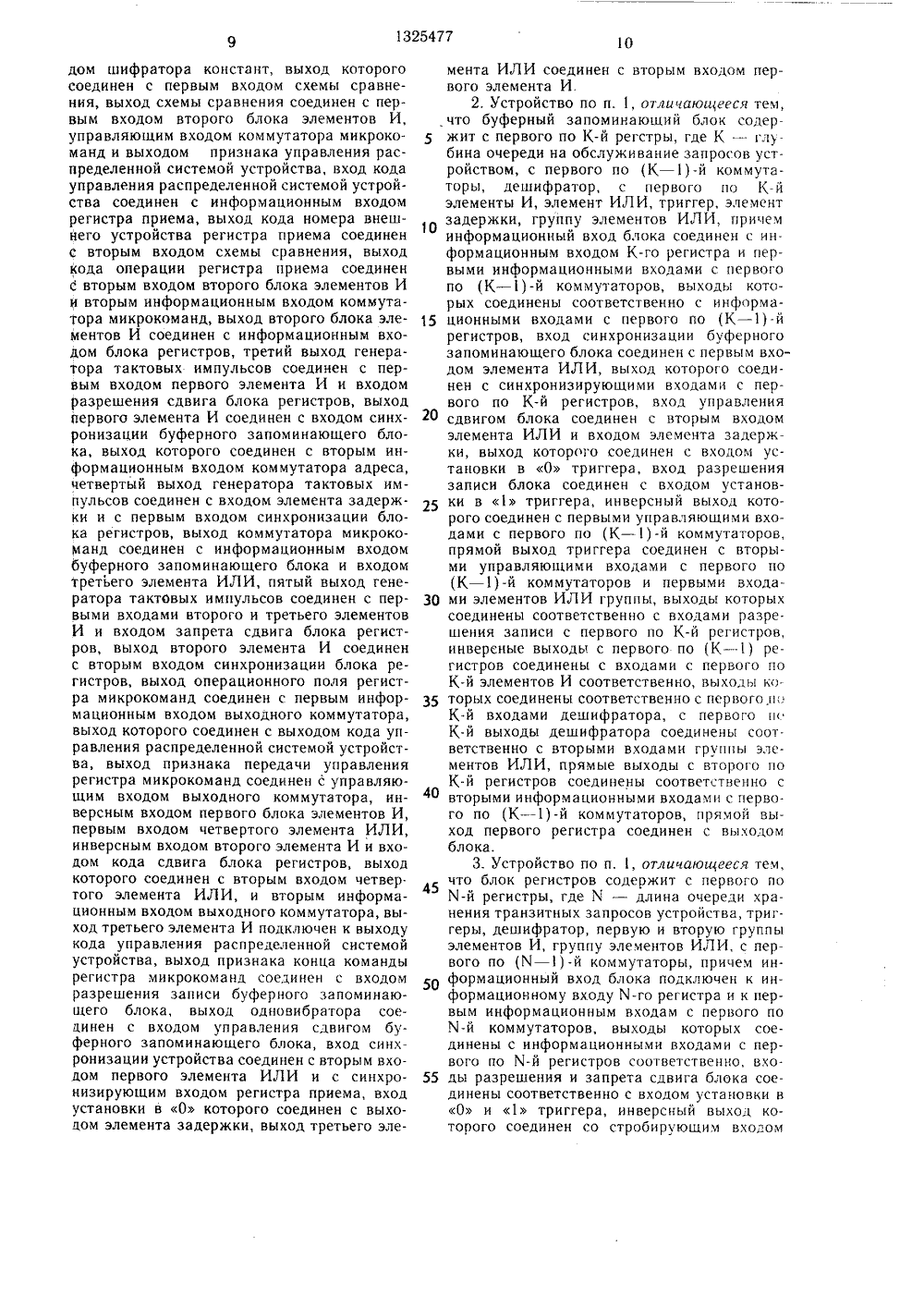

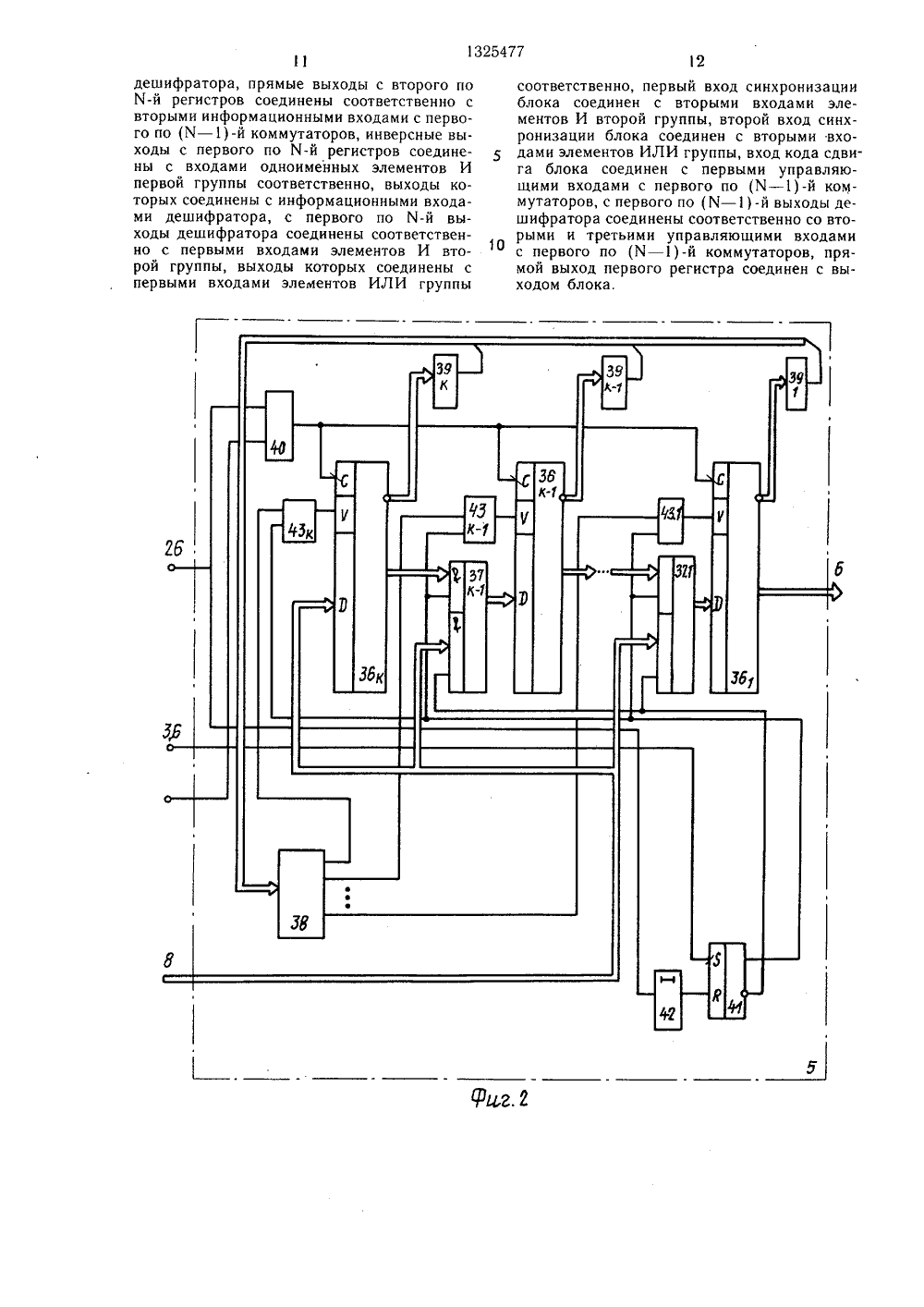

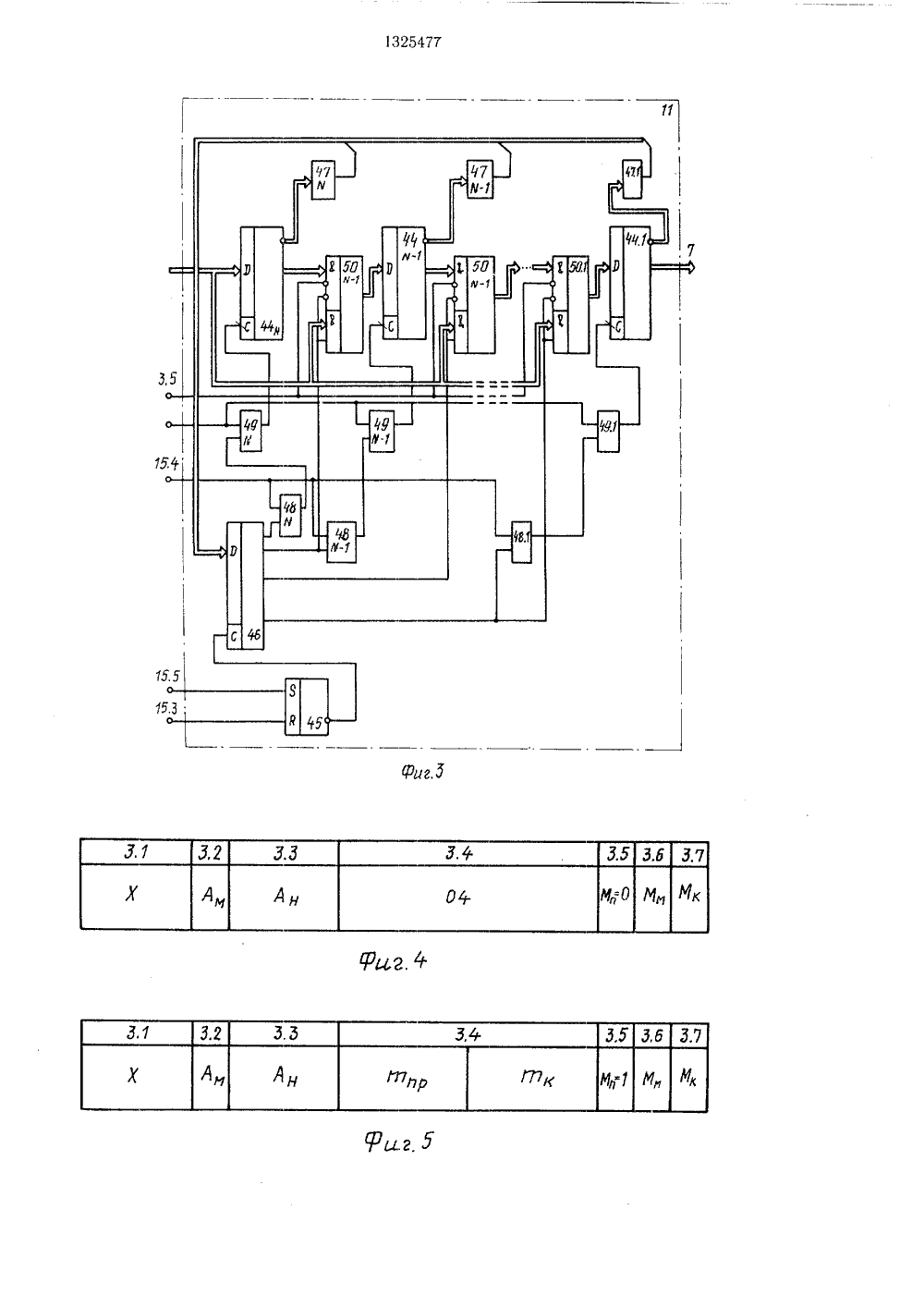

(54) МИКРО СТВО ДЛЯ УП РАВЛЯЮЩЕЙ ПРЕДЕЛЕННО (57) Изобретен ной технике и при построении тельных систем ти, в частности управления в Цель изобретен ПРОГРАММНОЕРАВЛЕНИЯ ОБМЕ ИНФОРМАЦИИ Й СИСТЕМЕие относится к вы может быть исп управляющих и высокой произво при организации систолических с ия - расширени УСТРОЙ НОМ УП В РАС числительользовано вычисли- дительноспроцедур труктурах. е области СУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ,8013254 применения устройства за счет реализации транзитной передачи микрокоманд управления. Микропрограммное устройство для управления обменом управляющей информации в распределенной системе содержит блок 1 памяти микропрограмм, регистры адреса 2, микрокоманд 3 и приема 4, буферный запоминающий блок 5, коммутаторы адреса 6, выходной 7 и микрокоманд 8, генератор 9 констант, схему сравнения 10, блок 1 регистров, мультиплексор 12 логических условий, триггер 13 запуска, генератор 4 тактовых импульсов, третий 15.1, первый 15.2, второй 15,3, четвертый 15.4 и пятый 15.5 выходы генератора 14 тактовых импульсов, элемент 16 задержки, элементы И 7, 18 и 19, блоки 20 и 21 элементов И, первый 22, второй 23, третий 24, четвертый 25 элемен-ты ИЛИ, одновибратор 26. Новыми в устройстве являются шифратор 9 констант, регистр 4 приема, схема 10 сравнения, блок 11 регистров, элемент 16 задержки и выходной коммутатор 7, что позволяет достигнуть цели изобретения. 2 з.п. ф-лы, 8 ил. ф1325477 ачальн ас а ась агв Р гого нпгу с иг ии ма иа 8 ыдача начапьнсго аЗ еаза Р йгоЮ ИПУУ витель В. Крид И, Вересж 672а СССР по дел35, Раушскаяредприятие, г. Редактор Н. ЕгороваЗаказ 31 О/44ВНИИПИ Государст113035Производственно-по Сост Техр Тира нного комитет Москва, Ж- - играфическое оручкоКорректор А. ТяскоПодписноеам изобретений и открытийнаб., д. 4/5Ужгород, ул. Проектная, 45 10 15 Изобретение относится к вычислительнойтехнике и может быть использовано при построении управляющих и вычислительныхсистем высокой производительности.Целью изобретения является расширениеобласти применения устройства за счет реализации транзитной передачи микрокомандуправления.На фиг. 1 представлена функциональная схема микропрограммного устройствадля управления и обмена управляющей информацией в распределенной системе; нафиг. 2 - функциональная схема буферного запоминающего блока; на фиг. 3 - функциональная схема блока регистров; нафиг. 4 и 5 - формат микрокоманды обработки; на фиг. 6 - пример организациимультимикропрограммной управляющей системы на основе однотипных устройств; нафиг. 7 и 8 - временная диаграммафункционирования устройства в различныхрежимах работы.Микропрограмма (программа), выполняемая устройством, состоит из двух подмножеств микрокоманд М и Мг. Первыйтип микрокоманд - М предназначен непосредственно для управления операционным устройством, например, арифметико-логическим блоком. Во время выполнения микропрограммы устройство может выдавать нааналогичное микропрограммное устройствоуправления микрокоманды второго типа(Мг), образующие микрокоманды передачиуправления. Формат данной микрокомандыпредставляется в видеМг= шпротгде п 4 Р - номер (код) устройства-приемника информации;гп - номер (код) микропрограммы, которую должно выполнить устройство-приемник;ф - знак контаденации (сцепления).Каждому устройству, входящему в мультимикропрограммную управляющую системуприсваивается свой номер (идентификатор).Устройства, образующие систему, объединяются в кольцевую структуру. Поэтому микрокоманда передачи управления с -го устройства ( = 1,п) поступает на ( + 1) -е,которое определяет, ему ли предназначенапоступившая информация. Определение принадлежности информации происходит путемсравнения кода устройства-приемника информации с кодом-идентификатором устройства.При несовпадении этих кодов поступившаяинформация отправляется к (+2) -му устройству и т.д. до совпадения кодов. Присовпадении кодов информация о номере микропрограммы заносится в буферный запоминающий блок, В данный блок заносится управляющая информация как от аналогичных устройств, так и от супервизорного устройства (например, центрального процессора). Обработка информации из буферного 20 25 30 35 40 45 50 55 запоминающего блока осуществляется в соответствии с правилом: первым пришел - первым обслужен (организация типа Р 1 РО) .На фиг. 7 показано прохождение кода операции от центрального процессора (ЦП) и реализации микропрограммы, после окончания которой осуществляется сдвиг информации (нулевых кодов) в буферном запоминающем блоке. Кроме того, представлено поступление начального адреса микропрограммы (МП) от другого микропрограммного устройства управления (МПУУ). На фиг. 8 показана реализация микропрограммы, во время которой производится выдача начального адреса МП аналогичному МПУУ при одновременной транзитной передаче двух начальных адресов МП через микропрограммное устройство управления. Микропрограммное устройство для управления и обмена управляющей информацией в распределенной системе (фиг. 1) содержит блок 1 памяти микропрограмм, регистр 2 адреса, регистр 3 микрокоманд с полями: 3.1 - логических условий, 3.2 - модифицируемого разряда адреса, 3,3 - немодифицируемой части адреса, 3.4 -- операционным полем, 3.5признака передачи управления, 3,6 - признака окончания микропрограммы, 3.7признака конца работы устройства, регистр 4 приема, буферный запоминающий блок 5, коммутатор 6 адреса, выходной коммутатор 7, коммутатор 8 микрокоманд, генератор 9 констант, схему 10 сравнения, блок 11 регистров, мультиплексор 12 логических условий, триггер 13 запуска, генератор 14 тактовых импульсов, третий 15.1 первый 15.2, второй 15.3, четвертый 15.4 и пятый5.5 выходы генератора 14 тактовых импульсов, элемент 16 задержки, элементы И 17 - 19, блоки элементов И 20, 21, первый - четвертый элементы ИЛИ 22 - 25, одновибратор 26, первый 27 и второй 28 управляющие входы устройства, вход 29 настройки устройства, информационный вход 30 устройства, вход 31 кода операции устройства, вход 32 логических условий устройства, первый управляющий выход 33 устройства, информационный выход 34 устройства, второй управляющий выход 35 устройства.Буферный запоминающий блок 5 (фиг. 2) содержит с первого 36.1 по К-й 36.К регистры, с первого 37.1 по (К - 1).й 37. К - 1 коммутаторы, дешифратор 38, с первого 39,1 по К-й 39. К - 1 элементы И, элемент ИЛИ 40, триггер 41, элемент 42 задержки, группу 43.1 - 43.К элементов ИЛИ.Блок 11 регистров (фиг. 3) содержит с первого 44.1 по М-й 44. М регистры, триггер 45, дешифратор 46, первую 47.1 - 47.М и вторую 48.1 - 48.Л группы элементов И, группу 49.1 - -49.Х элементов ИЛИ, с первого 50.1 по (1 - 1)-й 50.Х - 1 коммутаторы.О 50 55 Формат микрокоманды обработки, определяемый полями регистра 3 микрокоманд (фиг. 4 а), содержит поле, проверяемое логическими условиями (Х), поле модифицируемого разряда адреса очередной микрокоманды (А ), поле немодифицируемой части адреса (Ам) очередной микрокоманды, поле операционной части 04) микрокоманды, поле признака передачи микрокоманды управления (М=О), поле признака конца микропрограммы (М.), поле признака конца работы устройства (М)Формат микропрограммы передачи управления (фиг. 4 б) отличается тем, что поле операционной части разбито на два сегмента, первый из которых несет информацию о коде устройства приемника управляющей информации (гпдр), а второй - информацию о коде номера выполняемой микропрограммы (команды) - (гп). Кроме того, в данном формате метка - признак передачи управления М= 1.При организации системы (фиг. 5) 1-е микропрограммное устройство управления (МПУУ) (1 = 1, п) имеет следующие входы - выходы; Х; - вход логических условий; Ч; - входы пуска - оста нова; Н; - вход настройки;- вход кода операции; У; - управляющий выход.Работа микропрограммного устройства возможна в трех режимах; режиме обработки собственных микрокоманд; режиме выдачи микрокоманд управления; режиме приема и анализа микрокоманд управления.В исходном состоянии элементы памяти устройства находятся в нулевом состоянии (за исключением разряда регистра 3 микрокоманд, определяющего признак конца команды - поле 3.6) (цепи установки исходного состояния не показаны).Перед началом функционирования устройства производится его настройка путем подачи на вход 29 кода номера устройства. Данный код определяет местоположение устройства в мультимикропрограммной управляюшей системе, построенной в виде кольца (фиг. 5) на основе однотипных устройств. Этот код является идентификатором устройства и формируется на выходе генератора 9 констант (фиг. 1). Работа устройства в режиме обработки собственных микрокоманд.Работа устройства в этом режиме функционирования начинается путем подачи на вход 31 кода операции, определяюшего адрес первой микрокоманды микропрограммы управления. Этот код на вход 31 устройства подается, например, от центрального процессора, Одновременно с подачей кода операции на вход 27 устройства подается сигнал пуска. Данный сигнал через элемент ИЛИ 22 устанавливает триггер 13 запуска в единичное состояние и разрешает тем самым формирование имульсов синхро 15 20 25 30 35 40 45 низации работы устройства с выходов генератора тактовых импульсов (фиг. 6).Так как на выходе схемы 10 сравнения имеется сигнал логического нуля, то этот сигнал разрешает прохождение кода операции со входа 31 устройства через коммутатор 8 микрокоманд (фиг. 1) на информационный вход буферного запоминаюшего блока 5. На выходе элемента ИЛИ 24 имеется сигнал логической единицы, который разрешает прохождение тактового импульса с выхода генератора 15.1 на управляющий вход буферного запоминающего блока 5 (фиг. 6). Тактовый импульс через элемент ИЛИ 40 (фиг. 2) поступает на синхронизирующие входы регистров 37.1 - 36.К. Регистры 36.1 - 36,К находятся в нулевом состоянии и поэтому на выходе элементов И 39.1 - 39.К присутствуют сигналы логической единицы. Эти сигналы образуют управляющий код, который определяет тот регистр, в который необходимо записать код операции (адресную микрокоманду, определяюшую номер выполняемой микропрограммы). Единичный управляющий код определяет для записи выходной (первый) регистр 36.1. Поэтому информация с информационного входа буферного запоминающего блока 5 через коммутатор 37.1 по тактовому импульсу заносится в регистр 36.1. Второй тактовый импульс с выхода генератора 15,2 поступает на синхронизируюший вход регистра 2 адреса, и информация с регистра 36.1 буферного запоминающего блока 5 (фиг. 2) через коммутатор 6 адреса заносится в регистр 2 (фиг. 1). Из блокапамяти микропрограмм будет считана микрокоманда, которая по очередному тактовому импульсу с выхода . генератора 15.3 заносится в регистр 3 микрокоманд. Формат считанной микрокоманды представлен на фиг. 4. Операционная часть микрокоманды с поля 3.4 регистра 3 поступает на выход 33 устройства для управления операционным блоком, например, арифметико-логическим устройством.Поля 3 1, 3 2 и 3 3 регистра 3 микрокоманд формируют адрес очередной микро- команды с использованием мультиплексора 12 логических условий. Последний предназначен для формирования значения модифицируемого разряда адреса очередной микрокоманды и реализует логическую функцию видау 1 = х 1 а + хг 1 + хзгФ.+х.121 где у 1 - выходной сигнал мультиплексора 12логических условий;х 1 - конъюкция а 1, аа 1, соответствующая комбинации с выхода 3.1 кода логических условий, разре 1 паюшей прохождение модифицируемого адресного разряда а без изменений;Х 2 = аЯ 2 а 1,лВахз = а 1 аазах 4 = а 1 а 2 аза 1 - конъюкции, соот 1325477ветству ющие кодам, определяющим прохождение на выход мультиплексора 12 одного из сигналов логических условий 21, 2 ъ,2 со входа 32 логических условий устройства.В процессе выполнения микропрограммы со входа 31 кода операции через коммутатор 8 микрокоманд в регистры, 36.1 - 36,К могут заноситься по тактовому импульсу с выхода 15.1 генератора 4 коды номеров очередных микропрограмм (коды операции).По тактовому импульсу с выхода 15,2 , генератора 14 происходит занесение сформированного адреса очередной микрокоманды в регистр 2 и обращение к блоку 1 памяти микропрограмм. По тактовому импульсу с выхода 15.3 генератора 14 происходит занесение считанной из блока 1 памяти информации в регистр 3 микрокоманд. Одновременно с выдачей последней микрокоманды выполняемой микропрограммы в поле 3,6 регистра 3 микрокоманд заносится метка-признак окончания команды. Эта метка, во-первых, поступает на вход коммутатора 6 адреса и разрешает прохождение через него информации из буферного запоминающего блока 5. Во-вторых, метка конца команды устанавливает триггер 41 буферного запоминающего блока 5 (фиг. 2) в единичное состояние, разрешаюгцее тем самым сдвиг информации в регистрах 36.1 - 36.К путем коммутации выходов последующих регистров с информационными входами предыдущих регистров через соответствующие коммутаторы 37.1 - 37.К. В-третьих, метка-признак конца команды поля 3.6 регистра 3 микрокоманд формирует на выходе одновибратора 26 импульс. Этот импульс через элемент ИЛИ 40 буферного запоминающего блока 11 (фиг. 2) поступает на синхронизирующие входы регистров 36.1 - 36,К и производит сдвиг информации. После сдвига информации в регистрах 36.1 - 36.К буферного запоминаюгцего блока 5 на выходе элемента 42 задержки формируется импульс, устанавливающий триггер 41 управления в нулевое состояние (фиг. 6). Далее устройство функционирует аналогично рассмотренному.Работа устройства в режиме выдачи микрокоманд управления осуществляется следующим образом.В процессе обработки собственных микрокоманд устройство может выдавать микро- команды управления аналогичным устройствам, образующим кольцевую мультимикропрограммную систему. Формат микрокоманды передачи управления представлен на фиг. 5, В этом случае с поля 3.4 регистра 3 микрокоманд выдается микрокомандаМ = гп,рф гпту где гпр - код (номер) приемника управляю. щей информации; 5 1 О 5 го 25 30 35 40 45 50 55 гп - код (номер) микропрограммы, которую должно выполнить гп,-е микропрограммное устройство управления;ф - знак конкатенации (сцепления).Одновременно с кодом М передачи управления с выхода поля 3.5 регистра 3 мнкрокоманд выдается метка, определяющая признак передачи микрокоманды управления аналогичному устройству. Эта метка поступает на управляющий вход выходного коммутатора 7 и разрешает тем самым прохождение микрокоманды передачи управления с поля 3.4 регистра 3 микрокоманд на выход 34 устройства для обработки аналогичным устройством. Кроме того, метка- признак передачи (М = 1) управления поступает на управляющий вход блока элементов И 21 и запрегцает тем самым прохождение кода на выход 33 устройства. Метка-признак передачи управления через элемент ИЛИ 25 поступает на элемент И 19 (фиг. 6) и разрешает прохождение через него тактового импульса с выхода генератора 15,5. Тактовый импульс вместе с кодом М передачи управления выдается на выход 34 устройства. Далее микропрограммное устройство управления или выдает очередную микрокоманду (код) передачи управления, или обрабатывает собственные микрокоманды, аналогично рассмотренному,Работа устройства в режиме приема и анализа микрокоманд управления.Микрокоманда передачи управления М от аналогичного устройства поступает на вход 30 устройства, Одновременно с этим кодом со входа 30 устройства поступает также тактовый импульс, Данный импульс поступает на синхронизирующий вход регистра 4 приема и производит в него запись информации. Если устройство не производило обработку некоторой микропрограммы, то тактовый импульс через элемент ИЛИ 22 установит триггер 13 запуска в единичное состояние и разрешит тем самым формирование импульсов с выхода генератора 14.Код, занесенный в регистр 4 приема, состоит из двух частей: кода-номера устройства приемника информации гпи кода-номера микропрограммы, которую необходимо выполнить в, Код номера приемника информации с поля регистра 4 приема поступает на вход схемы 10 сравнения, где происходит сравнение с кодом номера данного устройства, поступающего с выхода генератора 9 констант,Если поступившие на схему 10 сравнения коды не равны, то на выходе схемы будет сигнал логического нуля. Нулевой сигнал с выхода 3.5 регистра 3 поступает на вход элемента И 17 и разрешает прохождение через него тактового импульса с выхода 15.5 генератора 4 для организации сдвига информации в блоке 11 регистров. Сигнал логического нуля на выходе схе 1325477мы 10 сравнения идентифицирует то обстоятельство, что поступившая в устройство информация должна быть передана транзитом другому устройству управления, По тактовому импульсу с выхода генератора 15.4 информация с выхода регистра 4 приема через блок элементов И 20 будет занесена в блок 11 регистров (фиг. 8). По тактовому импульсу с выхода 15.5 генератора 14 информация с выхода блока 11 ре. гистров через выходной коммутатор 7 поступает вместе с тактовым импульсом на выход 34 устройства.Если код номера устройства, которому предназначена управляющая информация, совпадает с кодом номера данного устрой. ства, то на выходе схемы 10 сравнения появляется сигнал логической единицы. Этот сигнал поступает на выход 35 устройства для организации работы мультимикропрограммной системы, например, для учета работы отдельных устройств, диспетчеризации заявок на обслуживание запросов между устройствами центральным процессором. Этот же сигнал запрещает запись информации через блок элементов И 20 в блок 11 регистров.Сигнал логической единицы с выхода схемы 1 О сравнения поступает на управляющий вход коммутатора 8 и разрешает прохождение через него информации о коде гп микропрограммы с поля регистра 4 приема на информационный вход буферного запоминающего блока 5. По тактовому импульсу с выхода 15.1 генератора 14, поступающему через элемент И 18 на управляющий вход буферного запоминающего блока 5, информация заносится в соответствующий регистр 36.1 (1 = 1, К) (фиг.2) в зависимости от длины существующей очереди. Далее устройство функционирует аналогично рассмотренному.Окончание процесса функционирования устройства может быть осуществлено по сигналу от центрального процессора, поступающему на вход 28 устройства, или по метке конца работы, выдаваемой в последней микрокоманде множества микропрограммы М с поля 3.7 регистра 3 микрокоманд. Сигнал признака конца работы устройства через элемент ИЛИ 23 поступает на нулевой вход триггера 13 запуска и обнуляет его. На этом работа микропрограммного устройства управления заканчивается и устройство готово к приему очередного кода микропрограммы от центрального процессора со входа 31 устройства или от соседнего аналогичного устройства управления со входа 30 устройства.Формула изобретения1. Микропрограммное устройство для управления обменом управляющей информации в распределенной системе, содержащее блок, памяти микропрограмм, коммутатор адреса, регистр адреса, регистр микрокоманд, буферный запоминающий блок, коммутатормикрокоманд, мультиплексор логическихусловий, триггер запуска, генератор тактовых импульсов, первый и второй блоки элементов И, первый, второй, третий и четвертый элементы ИЛИ, первый, второй, третийэлементы И, одновибратор, причем выход коммутатора адреса соединен с информационным входом регистра адреса, выход которого соединен с адресным входом блока памяти микропрограмм, выход блока памяти микропрограмм соединен с информационным входом регистра микрокоманд, выход поля кода, логических условий ре гистра микрокоманд соединен с управляющим входом мультиплексора логических условий, выход модифицируемого разрядаадреса регистра микрокоманд соединен спервым информационным входом мультиплексора логических условий, выход поля (и - 1) немодифицируемых разрядов адреса регистра микрокоманд, где п - разрядность адреса, соединен с первого по (и - 1)-й разрядами первого информационного входа коммутатора адреса, выход мультиплексора 25 логических условий соединен с и-ым разрядом первого информационного входа коммутатора адреса, прямой выход триггера запуска соединен с входом пуска генератора тактовых импульсов, вход логических условий устройства соединен с вторым информацион ным входом мультиплексора логических условий, вход кода операции устройства соединен с первым информационным входом коммутатора микрокоманд, вход запуска устройства соединен с первым входом первого элемента ИЛИ, выход которого соеди нен с входом установки в единицу триггера запуска, первый и второй выходы генератора тактовых импульсов соединены соответственно с синхронизирующими входами регистра адреса и регистра микрокоманд, выход признака конца команды регистра микрокоманд соединен с входом одновибратора и управляющим входом коммутатора адреса, вход сброса устройства соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом установки в О 45 триггера запуска ВыхОд признака конца работы регистра микрокоманд соединен с вторым входом второго элемента ИЛИ и первым входом первого блока элементов И, выходы операционного поля регистра микрокоманд соединены с вторым входом пер вого блока элементов И, выход которогосоединен с выходом кода микроопераций устройства, отличающееся тем, что, с целью расширения области применения устройства за счет реализации транзитной передачи микропрограмм управления, устройство содер жит шифратор констант, регистр приема,блок регистров, схему сравнения, элемент задержки, выходной коммутатор, причем вход настройки устройства соединен с вхо 1325477 10дом шифратора констант, выход которого соединен с первым входом схемы сравнения, выход схемы сравнения соединен с первым входом второго блока элементов И, управляющим входом коммутатора микрокоманд и выходом признака управления распределенной системой устройства, вход кода управления распределенной системой устройства соединен с информационным входом регистра приема, выход кода номера внешнего устройства регистра приема соединен с вторым входом схемы сравнения, выход кода операции регистра приема соединен с вторым входом второго блока элементов И и вторым информационным входом коммутатора микрокоманд, выход второго блока элементов И соединен с информационным входом блока регистров, третий выход генератора тактовых импульсов соединен с первым входом первого элемента И и входом разрешения сдвига блока регистров, выход первого элемента И соединен с входом синхронизации буферного запоминающего блока, выход которого соединен с вторым информационным входом коммутатора адреса, четвертый выход генератора тактовых импульсов соединен с входом элемента задержки и с первым входом синхронизации блоКа регистров, выход коммутатора микрокоманд соединен с информационным входом буферного запоминающего блока и входом третьего элемента ИЛИ, пятый выход генератора тактовых импульсов соединен с первыми входами второго и третьего элементов И и входом запрета сдвига блока регистров, выход второго элемента И соединен с вторым входом синхронизации блока регистров, выход операционного поля регистра микрокоманд соединен с первым информационным входом выходного коммутатора, выход которого соединен с выходом кода управления распределенной системой устройства, выход признака передачи управления регистра микрокоманд соединен с управляющим входом выходного коммутатора, инверсным входом первого блока элементов И, первым входом четвертого элемента ИЛИ, инверсным входом второго элемента И и входом кода сдвига блока регистров, выход которого соединен с вторым входом четвер. того элемента ИЛИ, и вторым информационным входом выходного коммутатора, выход третьего элемента И подключен к выходу кода управления распределенной системой устройства, выход признака конца команды регистра микрокоманд соединен с входом разрешения записи буферного запоминающего блока, выход одновибратора соединен с входом управления сдвигом буферного запоминающего блока, вход синхронизации устройства соединен с вторым входом первого элемента ИЛИ и с синхронизирующим входом регистра приема, вход установки в О которого соединен с выходом элемента задержки, выход третьего элемента ИЛИ соединен с вторым входом первого элемента И.2. Устройство по п. 1, отличающееся тем,что буферный запоминающий блок содержит с первого по К-й регстры, где К - глубина очереди на обслуживание запросов устройством, с первого по (К - 1) -й коммутаторы, дешифратор, с первого по К-й элементы И, элемент ИЛИ, триггер, элемент 10 задержки, группу элементов ИЛИ, причеминформационный вход блока соединен с информационным входом К-го регистра и первыми информационными входами с первого по (К - 1) -й коммутаторов, выходы которых соединены соответственно с информа ционными входами с первого по (К - 1)-йрегистров, вход синхронизации буферного запоминающего блока соединен с первым входом элемента ИЛИ, выход которого соединен с синхронизирующими входами с первого по К-й регистров, вход управления 20 сдвигом блока соединен с вторьм входомэлемента ИЛИ и входом элемента задержки, выход которого соединен с входом установки в О триггера, вход разрешения записи блока соединен с входом установ ки в 1 триггера, инверсный выход которого соединен с первыми управляющими входами с первого по (К - 1) -й коммутаторов, прямой выход триггера соединен с вторыми управляющими входами с первого по (К - 1)-й коммутаторов и первыми входа ми элементов ИЛИ группы, выходы которыхсоединены соответственно с входами разрешения записи с первого по К-й регистров, инверсные выходы с первого по (К - 1) регистров соединены с входами с первого по К-й элементов И соответственно, выходы коЗ 5 торых соединены соответственно с первого иоК-й входами дешифратора, с первого п К-й выходы дешифратора соединены соответственно с вторыми входами группы элементов ИЛИ, прямые выходы с второго по К-й регистров соединены соответственно с вторыми информационными входами с первого по (К - 1)-й коммутаторов, прямой выход первого регистра соединен с выходом блока.3. Устройство по п. 1, отличающееся тем,что блок регистров содержит с первого по М-й регистры, где М - длина очереди хранения транзитных запросов устройства, триггеры, дешифратор, первую и вторую группы элементов И, группу элементов ИЛИ, с первого по (М - 1)-й коммутаторы, причем ин формационный вход блока подключен к информационному входу 1 Ч-го регистра и к первым информационным входам с первого по М-й коммутаторов, выходы которых соединены с информационными входами с первого по М-й регистров соответственно, вхо ды разрешения и запрета сдвига блока соединены соответственно с входом установки в О и 1 триггера, инверсный выход которого соединен со стробирующим входом1325477 12 ЧЬ 2. 2 дешифратора, прямые выходы с второго по И-й регистров соединены соответственно с вторыми информационными входами с первого по (М - 1) -й коммутаторов, инверсные выходы с первого по И-й регистров соединены с входами одноименных элементов И первой группы соответственно, выходы которых соединены с информационными входами дешифратора, с первого по Я-й выходы дешифратора соединены соответственно с первыми входами элементов И второй группы, выходы которых соединены с первыми входами элементов ИЛИ группы соответственно, первый вход синхронизации блока соединен с вторыми входами элементов И второй группы, второй вход синхронизации блока соединен с вторыми входами элементов ИЛИ группы, вход кода сдвига блока соединен с первыми управляющими входами с первого по (М - 1)-й коммутаторов, с первого по (Я - 1) -й выходы дешифратора соединены соответственно со вторыми и третьими управляющими входами с первого по (1 Ч - 1)-й коммутаторов, прямой выход первого регистра соединен с выходом блока.

СмотретьЗаявка

4017608, 05.02.1986

ПРЕДПРИЯТИЕ ПЯ Г-4651

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, МЕЛЬНИКОВ ВЛАДИМИР АЛЕКСЕЕВИЧ, НИКОЛЬСКИЙ СЕРГЕЙ БОРИСОВИЧ, УЛИТЕНКО ВАЛЕНТИН ПАВЛОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, СПЕРАНСКИЙ БОРИС ОЛЕГОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: информацией, микропрограммное, обменом, распределенной, системе, управляющей

Опубликовано: 23.07.1987

Код ссылки

<a href="https://patents.su/10-1325477-mikroprogrammnoe-ustrojjstvo-dlya-upravleniya-obmenom-upravlyayushhejj-informaciejj-v-raspredelennojj-sisteme.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе</a>

Предыдущий патент: Микропрограммное устройство для контроля и управления

Следующий патент: Устройство для приоритетного подключения источников информации к общей магистрали

Случайный патент: Регулятор давления газа