Табличный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1108446

Автор: Мелехин

Текст

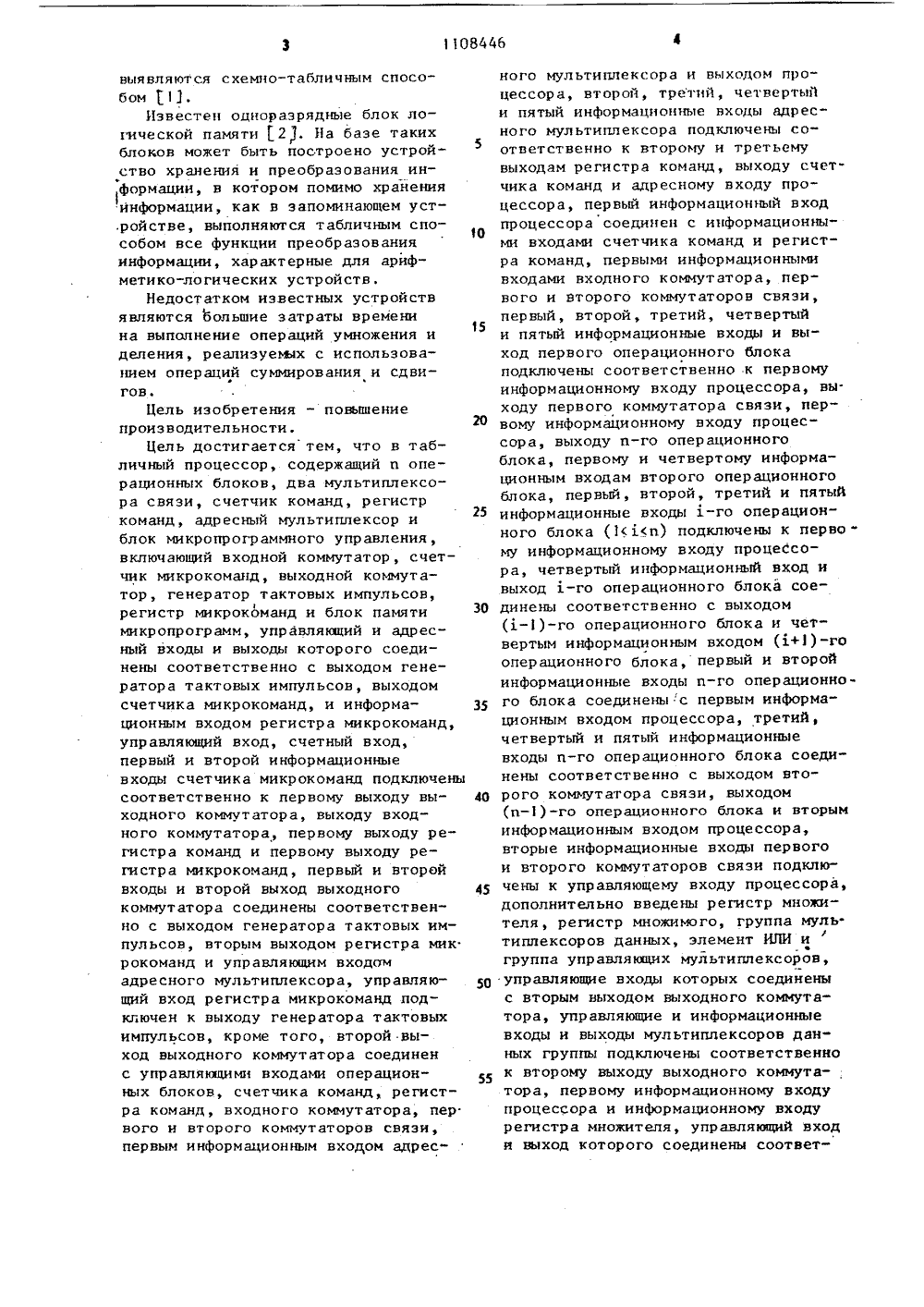

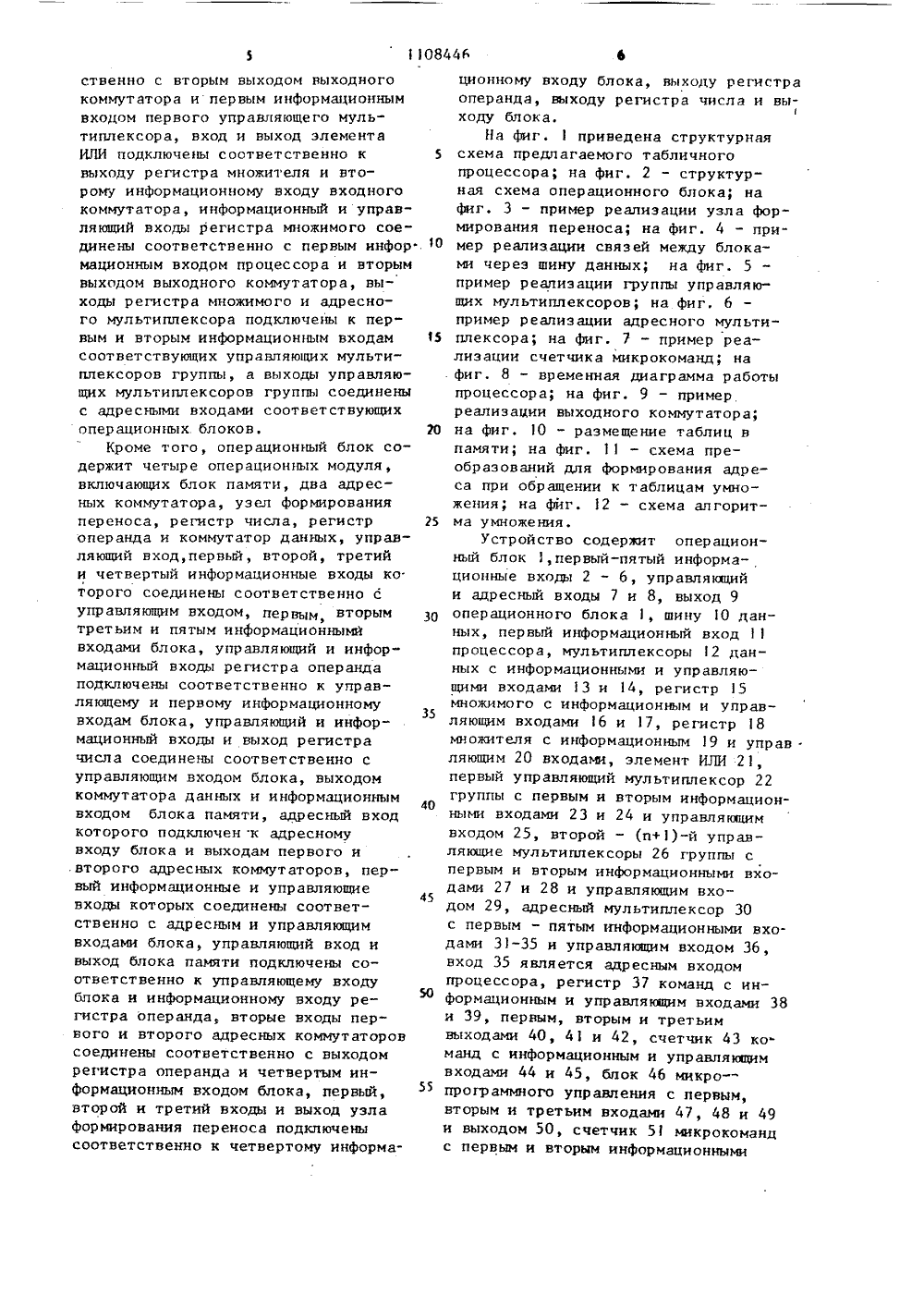

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН зшС 06 Г/00,ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬТИЙ(54)(57) 1. ТАБЛИЧНЫ ПРОЦЕССОР,содержащийоперационных блоков,два мультиплексора связи, счетчиккоманд, регистр команд, адресныймультиплексор и блок микропрограммного управления, включающий входнойкоммутатор, счетчик микрокоманд, выходной коммутатор, генератор тактовых импульсов, регистр микрокоманди блок памяти микропрограмм, управляющий и адресный входы и выходыкоторого соединены соответственнос выходом генератора тактовых импульсов, выходом счетчика микрокоманд и информационным входом регистра микрокоманд, управляющий входсчетный вход, первый и второй информационные входы счетчика микрокоманд подключены соответственнок первому выходу выходного комму-.татора, выходу входного коммутатора,первому выходу регистра команд ипервому выходу регистра микрокоманд,первый и второй входы и второй выходвыходного коммутатора соединены соответственно с выходом генераторатактовых импульсов, вторым выходом.801108446 А регистра микрокоманд и управляющим входом адресного мультиплексора, управляющий вход регистра микрокоманд подключен к выходу генератора тактовых импульсов, кроме того, второй выход выходного коммутатора соединен с управляющими входами операционных блоков, счетчика команд, регистра команд, входного коммутатора, первого и второго коммутаторов связи, первым информационным вхо дом адресного мультиплексора и выходом процессора, второй, третий, четвертый и пятый информационнье входы адресного мультиплексора под-ключены соответственно к второму итретьему выходам регистра команд, выходу счетчика команд и адресному входу процессора, первый информацион - ный вход процессора соединен с инфор мационными входами счетчика команд и Ф регистра команд, первыми информационными входами входного коммутатора,первого и второго коммутаторов свя-зи, первый, второй, третий, четвертыйи пятый информационные входы и выходпервого операционного блока подключены соответственно к первому информационному входу процессора, выходупервого коммутатора связи, первомуинформационному входу процессора,выходу и -го операционного блока,первому и четвертому информационнымвходам второго операционного блока,первый, второй, третий и пятый инфор.мационные входы 1-го операционного блока (1 ( 1( и ) подключены к первому информационному входу процессора, четвертый иформационньп входи выход-го операционного блокасоединены соответственно с выходом:П 52 Отдельные (З-е),шестнадцатиричные разряды чисел П и Б полностью определяются значением четырехразрядного кода П и соответствукицего. четырехразрядного кода Х и могут быть представлены как системы логических функций/П 4:1 = Р(П;4:13, Х 4:11); Б Г 4:33 = Р (13;Г 4 й 31, Х Г 4:1 Д), где 3=1,п;Г , Р - системы иэ четырех восьмиместных логических функцийСистемю функций Р 1 и Р могут быть реализованы табличным способомгс использованием последовательности преобразований х ). ДП3( оУ)Д, - "ь 5 ю где 3 1,п;Хо О,.- множество восьми- О разрядных кодов Х фПФР д 3 д - функции отображениямножества кодов на множество адре"сов Аблоков памяти, реализуеиие независимо во всех четверках 5 разрядов;Гч . - стандартная операциячтения из блоков памяти, соответствующая отображению множества ад"ресов в множество кодов на восходе 20 блоков памяти. В блоках памяти должны храниться таблицы преобразованийхи, - и)и хо о, - Б,соответствующие таблице умножениячетырехразрядных двоичных кодов. д Поясним составление таблиц, используя для удобства чтения представление кодов как в двоичной (дв.,так и в десятичной (дес.) системесчисления. Преобразования определены на 2 наборах значений кодаХ. о 0; и могут быть представленыХо 0П Здес, дв. дв. 18 00000010 0000 0010(приписывания) кодов Х и Р 1, Х еР. в десятичной системе счйслея соответствует десятичному номеру ячейки (адресу) в сегменте из 256 ячеек, столбцы П и Бсоотнетству. ют таблицам сист м Г и Г из четырех 8-местных Логических функций.Для размещения таблиц Г отведен . первый сегмент накопителя блоков 87 памяти с адресами (0255), а для размещения таблиц Г - второй сегмент с адресами (256,511). В выделенных сегментах таблицы преобразований периодически повторяются в каждой четверке разрядов. Размещение таблиц поясняет фиг. 10.На фиг. ) приведена схема преобразований для формирования адреса обращения к таблицам систем функцийГ и Г независимо в каждом операционном блоке 1, содержащий четыреразряда. Она соответствует выражениюФА 1 шз Я А 12 ф 13 =С 2 з 1 ЯЧ 21 ф,:203 ф Х 4; 1 о Р 14: Ц,где код С =ОО определяет областьпамяти объемом 1 К слов, к которойимеется доступ на микропрограммномуровне;Ч 21:20- два разрядан управляющем коде на выходе 50 блока 46 микропрограммного управления,которые в выделенной области памяти задают адрес сегмента из 256ячеек;код Х ОР,; , соответстнуетчетырем разрядам множимого и четыремразрядам множителя, этот код определяет адрес ячейки в выбранном еегменте памяти.Рассмотрим реализацию преобразований, показанных на фиг, 11. Для обра.щения к таблицам используется четвертый канал (В 4) адресного мультиплексора 30. За счет соответствующихсоединений информационных-входов 35и 31, образующих четвертый канал,реализуется операция конкатенацииВ ш 13 В 4 12:щСу 2 ф 1 оХ 1 О: 13=00 Щ;,21:123.При Ч11 - У 5 ьВ 400ьЧ, 121: 23Старшие ш 8 " 4 разряда кода У3 Ь фполученного на выходе адресного муль. типлексора 30, лоступают. на старшиешразрядов адресных входов 8всех операционных блоков 1. На мпадшие четыре разряда адресных входов 8через Управляющий мультиплексор 22поступает код Р -"У с выходон ре 1 1 Вгистра 8 множителя. Для этого навход 25 подается управляющий сигны 025=0 На разряды 5, ",8 вхо 1 О дов 8 н каждом 1-м операционном блоке 1 подается код Х с соответствующих выходов регистра 15 множимого через управляющие мультиплексоры 26. Дпя этого на управлякицие вхо 5 ды 29 подается сигнал Б =О.29Рассмотрим функциональную микропрограмму операции умножения. Поскольку число шагов алгоритма уменьшено в четыре раза, с целью повьве 20 ния производительности следует использовать микропрограмму без циклов. С целью упрощения записей микропрограмму рассмотрим применительно к случаю умножения двух восьг 5 .миразрядных чисел, На фнг, 12 приведена укрупненная схема алгоритмамикропрограммы умножения.Микропрограмма умноженияНачало,Зо М 1. Р 1 6 Х, на М 2;(ю чтение из памяти по адресу А = Умножимого Хи запись его в регистр 15 ЯР 18 Р 1 Н (42) ф 131(Р дО то на МЗ, иначе на М 4;( чтение из памяти по адресу АУ4 гмножителя Р, выделение четырех мпадших разрядов (Р ) и запись их в,регистр 18, проверка содержимого наравенство нулю Ф ).МЗ. РЧ ф ОО, на М 9; (+ запись врегистр 104 числа нуля +).М 4, РЧ - Гг(Х,Р), на М 51 (ю вычисленне Б табличным способом, записьрезультата в регистр 04 числа РЧ )М 5. ОЯ + РЧ, на М 6:, (Ф запись Воперативную ячейку памяти содержимого регистра 104 числа РЧ + ).М 6, РЧ+.(ОЯ 1 2, на М 7; (.чтение-4числа из оперативной ячейки ОЯ изапись со сдвигом на четыре разряда вправо в регистр числа Ф),М 7. РО - Г(Х, Р,),на М 8; (вычисление П табличным способом изапись в регистр 107 операнда ).53М 8. РЧ+.РЧ + РО, на М 9 ( Ф сумЭ Фмирование чиселиз регистров числа104 и операнда 107, и зались результата в регистр числа; результат соответствует. частичному произведению(Ф чтение иэ памяти множителя Р,выделение четырех разрядов 58(Р ) и запись их в регистр 8, проверка содержимого на равенство нулю 1)М 10, ОЯ 4- РЧ, на М 15; (Ф запись числа из регистра числа в оперативную ячейку памяти м),М 11. РО е. Р 2 (Х, 02), на М 12; (+ вычисление 82 табличным способом,запись результата в регистр операнда 107).М 12 РЧ е-(РЧ + РО) 2 ф, на М 13;( % сложение чисел из регистровчисла и операнда и запись результата со сдвигом на четыре разряда вправо в регистр числа Ф).М) 3. РО 4-Р(Х, Р 2), на М 14; (Ф вычисление П табличнйм способом и записьв регистр 107 операнда ).М 14. РЧ+.РО + РЧ, на М 16; (+ суммирование чисел иэ регистров операнда107 и числа 104 с записью резуль,тата в регистр числа; результатсоответствует произведению С = СПф + (С .л 81) 2-4 У)М 15. РЧ ф.(ОЯ) 2 4, на М 16;./(.Ф чтение ОЯ памяти и запись считанногочисла со сдвигом на четыре разрядавправо в регистр числа, записанное число соответствует произведениюС = С 2%).М 16 Н (У%2) -РЧ 1 ( СК 43 1СК 43 1 +1; (я запись результата в накопитель памяти по адресуА = У 42, модификация содержимогосчетчика 43 команд прибавлениемединицы) .Конец.Для иллюстрации алгоритма рассмотрим пример умножения двух чи.сел Х = (О), 1111111 и Р "+ 0000000 = 1100000.Конец,24Рассмотрим выполнение в табличномпроцессоре операции суммированияРЧ 4- РО + РЧ, которые используютсяи в алгоритме умножения,Сразу после записи слагаемых в ре"гистры 104 и 107 в узлах 100 формирования переносов возникает переходный процесс, связанный с распространением "волны" переносов,О Этот переходный процесс должен закончиться до;начала следующего циклаработы процессора (фиг.9). Суммирование выполняется за один цйкл обращения к блокам 87 памяти. При этом настаршие шразряда адресных входов89 через входы 8 поступает одинаковыйкод адреса, определяющий адрес сегментиз воСьми ячеек, которому соответствуют, например, ячейки с адреса"ми 528535 (фиг, О). В каждомразряде этого сегмента записанатаблица трехместной логической функции у = х 1 (+) х 20+ х 5, как показа"но на фиг. 1 О.25 АдреСация к ячейкам сегмента привыполнении суммирования осуществляется независимо в каждом разряде.На третий разряд адресного входа 89подается сигнал с входа 82 черезкоммутатор 96. Этот сигнал соответствует переносу из соседнего младшего разряда операционного модуля 78,На первый и второй разряды адресного входа, 89 подаются сигналы с выходов регистров 104 и 107 через ком"35мутатор 92. На управляющие входы 95и 99 подаются единичные сигналы.Рассмотренная таблица трехмест"ной логической функции может быть ис.польэована как две таблицы при вы 40полнении операций реализации пораз-.рядных двухместных логических функций:У,= х, Д+ Ч = хДГх 2,В ячейках 536, размещаютсятаблицы других двухместных логических функций. Так, на фиг. О показано размещение во всех разрядахячеек 536539 таблиц функции5 О У-х 1 х При реализации двухместныхлогических функций на управляющиевходы коммутаторов 92 и 96 подаютсяуправлянзцие сигналы Уз=1, Пзз=0.При этом на третий разряд адрес 55ного входа 89 подается сигнал треть"его разряда с выхода адресного мультиплексора 30, а на первый и второйразряды входа 89 подаются сигналы свыходов регистров 104 .и 07, соот308446 26, О ООО ООО 000, ЧОО, Ч 10,О 1 ао-О, В 3 оэ=о, О 3=1, О,3 =О, 09М 2.Ч, у=о, О, О, 1,09 йо ОУ О, Ч 132 00, О 1=0 О 0Ч-ао, О-О 1, Х-ОООООООООО.,Чь =Ооэ Ч 9=10; Ооь 0 О =О,О,-а, о,-1, О 9,=О, У=О 1,МЭ,Чьц 010 Урт О Оу 9 1ОЪ 1О=о, 0=0, Ч 31,=00, О=О, О=о,Ч 4 00 ЧЯ 4О О, О-.О О О, ЧФ 00 (Ф считывается код 0 0 иэ ячейки с адресом 528, фиг. 30 ф).МФ.Ч=1 О 1 О, У,-О, О,-О, ОО,09 О, 099=0 9.3=00 ОУ що О щоЧ =ОО, Ч =11, Х 3 О 1 ОООООООО,Чь =00 Чфф 10 Оща =1 ОЦьуоо-О о,=о о=о, ч,-оо,М 5Чф 010 у-о, ОфОа 1Оээ 0 О 19 0 У .3 00 0 уао ООЧ -ОО,. У.-11, 2, -1 ООО 1 ОО 1 ОО,Ч-оо, Ч-Ц, О-о, Ц-О,ветствующие аргументам реализуемых функций. Тип реализуемой функции определяется адресом сегмента и запи санными в нем таблицами. Адрес сегмента формируется с использованием четвертого канала адресного мультиплексора 30. Соответствующая информа ция записывается в 34. 21 разрядах микрокомандыАщфЗ)щА 1233"00 Ф Ч Я 23:141, При реализации функции т =х 3 х таблица которой размещена в ячейках 536, ,539, Ч 923:143=3000030,При суммировании адресация к сегмейту с таблицей функции 33 хфх 29 х 9 осуществляется через четвертый канал адресного мультиплексора 30 (О 9 ь 31). При этом в 1521 разрядах микрокоманды должен быть записан код Ч 23:353 = 1000010.Определим последовательности упраапяющих сигналов, которые должны быть сформированы в блоке 46 микропрограммного управления при выполнении команды умножения: О 1=0 Оффо 090 Ч 4900 (Ф запись производится в ячейку с адресомА = 548001000300100-%).336,У 010, у =О, О =1, 0 =1,О 99 О О 9-0 Ъ,11 =11 Оь О, 07 -О,Ч,-ОО, Ч, Х =1 ООО 1 ОО 1 ОО,У-ОО, У=10, О, О,=О,011 ойо =О, 09=0 Ч 49=00.И 7,У 4=010, у =о, О=1, О 9=1,О=О, О=О, Ъ,-ОО, О=О, О,=О,Ч-ОО, Ч =11, Х=ОООООООООО,"35ЧЦ =00, Чэ =1 О, О =О, 01 О =1,Н 0 Ого 0 ОИ =О, ЧМ=ОО.М 8,Уды=010, У=о, 0=3, О =1,О 1, О 99 -1, / -00, О - О, О -О,Ч + ОО, Ч -11, Х -ОООООООО,У =00, Ч =10, О =1, 036 У=О,1 0 О 3 О 0 ЧффИ 9ф 11 оф Ут 3 О О 1 ОффОэ09 - О У=00 О то Оу 01+ О 1 Чэф О 1 9 0(3003333(3007 0 Оф 1 Озф О Чф - (3И 10.= 0000000000, Ч а =00, Ч э =11,О 1 =О, Ооэ =О, 01 =О, О - - О,39После выполнения последней микрокоманды в микропрограмме (в данномслучае М 6) осуществляется переходк микрокоманде, например17,при выполнении которой производитсячтение из памяти новой команды поадресу, код которого берется изсчетчика команд, запись команды врегистр 37 команд и запись кода операции в счетчик 51 микрокоманд повходу 47. При этом формируютсяследукзцие управляющие сигналы:М 17Ч 001 у 7 =О, Оу=1 О =1,)-О, П=О, Ч=00, О=О,Ъ=О,4 00Ч 1 О Х 00(100011 При 4 п ) 8 в схеме апгоритма на фиг. 12 следует увеличить число фраг ментов, соответствукщих умножению на четыре разряда множителя(М 9,М 15). В общем случае при умножении 4 п-разрядных чисел для времени умножения 1 получим следующую среднюю оценку, полагая, что О ив каждом разряде равновероятны:15 1 е = 2 +5 + - + (и-) 16 16 5 2(2,875 + 4,88 и) ТСоставив соответствующую микропрограмму, можно показать, что при использовании известного наиболее распространенного в ЭВМ метода умножения двоичных чисел с мпадших разрядов потребуется в среднеи времяе = (26 п+6) Те Определим относительное уменьшение времени умножения при использовании таблично-алгоритмического метода:4 п у /Ть у/То(ч М"ч МЙу8 58 2 6 О 78 4 616 11 О 22, 4 0,80 4,9 О32 214 41,9 0,805 5,64 422 81 0,81 5,25Таким образом, вфемя умноженияуменьшается в среднем, в 5 раз, Этодостигается как за .счет уменьшениячисла щагов в апгоритме (в 4 раза), .так и за счет исключения циклов.Рассмотрим способ деления в таблич -ном процессоре Т " Х: Р, где Хделимое, Р - делитель Т " частное.Представим операцию деления последовательностью. двух операций - обращения и умноженияТ (1/Р) ХДля операции обращения У " 1/Р воспользуемся итерационной процедурой30 2У 1=2 У; - У Р,где У, - 1-е приближение результата,Процедура имеет квадратичную сходимость, т.е. при очередном (д-м)35 шаге числО верных разрядов в результате У удваивается.Рассмотрим способ определения на"чапьного приближения Уо =/Р.В общем случае 4 п-разрядное чис 40 ло Р, представленное в форме с фиксированнойй запятой, может содержатьБ нулей в старших разрядах, 0 4 8 и.Будем рассматривать число Р 2, встаршем разряде которого единица,45 Приближенно представим его числомК, пять старших разрядов которогосовпадают со старшими разрядами5числа Р 2, а остальные равны нулкКФР2 . Числа К расположены в350 интервале (2 ", 1-2 5).Рассмотрим число 2пропорциональное обратному значению К:2 - - . 2 (:( 2 ).1о К55Поскольку старший разряд числа Квсегда равен единице, может быть всегдашестнадцать различных значений К,10 30 35 Ее " Р (К) и разместим ее в ячейках, памяти с адресами 512521. (фиг,10) таким образом, чтобы четы-ре младших двоичных разряда адреса совпадали с 4 п, 4 п, 4 п-З, 4 празрядами соответствующих значений К. Для выделения требуемых разрядов число К сдвигается влево на один разряд, иэ сдвинутого числа мультиплексорами 12 выделяются четыре старших разряда и записываются в регистр 18.Для обращения к таблицам Р адрес требуемого сегмента памяти поступает иэ блока 46 микропрограммного управ ления через адресный мультиплексор 30, а адрес требуемой ячейки в сегменте (четыре младших разряда кода адреса на входах 8) - с выхода Р 18 через управляющий мультиплексор 22. 20 При этом Ч 11, О О, П щ 1. Таким образом, для определенйя Е, табличным способом используются те же технические средства, которые были введены для ускорения уьжоже НИЯ еВ Оценим погрешность представлениячисел ,Р 2 числами КРг 2 -К 2Э ф-фУ - - - 22-1 При этом погрешность определенияначал ьного приближенияУ Еь 2 +"1 Р- а и фРТаким образом, в Е ь (1,2) можно считать достоверными четырестарших разряда, остальные разрядын числах, янляющихся элементаьвтаблицы преобразования ЕР(К),следует принять равными йулю (фиг,10).(1/Р) 2 911 будем испольэовать итерационную процедуруЕ (Е, (Р г )Е Е )2где 1 О,1В этой процедуре используется число Р, сдвинутое на Б разрядов влево при вычислении К, и число Ео,полученное с использованием таблицы.После вычисления Е с требуемойточностью для определения частногоТ следует выполнить операцию Т =Е Х 2 зф".Анализ соответствующей микропрограмэ 1 показывает, что времяделения указанным способом н сравнении с распространенным методомделения многократным вычитаниемделителя и сдвигов уменьшено нсреднем на 203.Таким образом, за счет уменьшениявремени умножения и деления обеспечивается повышение производительности процессора.11084 6 -1)-го операционного блока и четвер тым информационным входом (1+1)-го операционного блока, первый н второй информационные входы и -го операционного блока соединены с первым информационным входом процессора, третий, четвертый и пятый информационные входы Н-го операционного блока соединены соответственно с выходом второго коммутатора связи, выходом 9)-1)-го операционного блока и вторым информационным входом процессора, вторые информационные входы первого и второго коммутаторов связи подключены к управляющему входу процессора, о т л и ч а ю щ и й с я тем, что, с целью повышения производительности; он содержит регистр множителя, регистр множимого, группу мультиплексоров данных, элемент ИЛИ и группу управлякщих мультиплексоров, управляющие входы которых соединены с вторым выходом выходного коммутатора, управляющие и информационные входы и выходы мультиплексоров данных группы подключены соответственно к второму выходу выходного коммутатора, первому информационному входу процессора и информационному входу регистра множителя, управляющий вход и выход которого соединены соответственно с вторым выходом выходного коммутатора и первым информационным входом первого управляющеего мультиплексора, вход и выход элемента ИЛИ подключены соответственно к выходу регистра множителя и второму "информационному входу входного коммутатора, информационный и, управляющий входы регистра множимого соединены соответственно с первым информационным входом процессора и вторым выходом выходного коммутатора выходы регистра множимого и адресно. го мультиплексора подключены к первым и вторым информйционнык входам соответствующих управляющих мультиплексоров группы, а выходы управляющих мультиплексоров группы соединены с адресными входами соответствукицих операционных блокЬв.2. Процессор по и. 1, о т л и ч а ю щ и й с я тем, что операционный блок содержит четыре операционных модуля, включающих блок памяти, два адресных коммутатора, узел формирования переноса, регистр числа, регистр операнда и коммутатор данных, управляющий вход, первый, второй, третий и четвертый информационные входы которого соединены соответственно с управляющим входом, первый, вторым, третьим и пятым информационными входами блока, управлякнций и информационный входы регистра операнда подключены соответственно к управляющему и первому информационному входам блока, управляющий и информационный входы и выход, регистра числа соединены соответственно с управляющим входом блока, выходом коммутатора данных и информационным входом блока памяти, адресный вход которого подключен к адресному входу блока и выходам первого и второго адресных коммутаторов, первые информационные и управляющие входы которых соединены соответственно с адресным и управляющим входами блока, управлякиций вход и выход блока памяти подключены соответственно к управляющему входу блока и информационному входу регистра операнда; вторые входы первого и второго адресных коммутаторов соединены соответственно с выходом регистра операнда и четвертым ин-, формационным входом блока, первый, второй и третий входы и выход узла формирования переноса подключены соответственно к четвертому информационному входу блока, выходу регистра операнда, выходу регистра числа и выходу блока.Изобретение относится к вычислительной технике.Известно логическое запоминающее устройство, основными компонентами которого являются одноразрядные блокипамяти, в которых табличным способомвыполняются логические преобразоваия, а переносы при сумьырованиивыявляются схемно-табличным способом 11Известен одноразрядные блок логической памяти2. На базе таких блоков может быть построено устройство хранения и преобразования информации, в котором помимо хранения информации, как в запоминающем уст.ройстве, выполняются табличным спо - собом все функции преобразования информации, характерные для арифметико-логических устройств.Недостатком известных устройств являются большие затраты времени на выполнение операций умножения и деления, реализуемых с использованием операций суммирования и сдвигов.Цель изобретения - повышение производительности.Цель достигается тем, что в табличный процессор, содержащий и операционных блоков, два мультиплексора связи, счетчик команд, регистр команд, адресный мультиплексор и блок микропрограммного управления, включающий входной коммутатор, счетчик микрокоманд, выходной коммутатор, генератор тактовых импульсов, регистр микрокоманд и блок памяти микропрограмм, управляющий и адресный входы и выходы которого соединены соответственно с выходом генератора тактовых импульсов, выходом счетчика микрокоманд, и информационным входом регистра микрокоманд, управляющий вход, счетный вход, первый и второй информационные входы счетчика микрокоманд подключены соответственно к первому выходу выходного коммутатора, выходу входного коммутатора, первому выходу регистра команд и первому выходу регистра микрокоманд, первый и второй входы и второй выход выходного коммутатора соединены соответственно с выходом генератора тактовых импульсов, вторым выходом регистра мик рокомавд и управляющим входом адресного мультиплексора, управляющий вход регистра микрокоманд подключен к выходу генератора тактовых импульсов, кроме того, второй выход выходного коммутатора соединен с управляющими входами операционных блоков, счетчика команд, регистра команд, входного коммутатора, пер вого и второго коммутаторов связи, первым информационным входом адрес 50 управляющие входы которых соединены 55 5 10 15 20 25 30 35 40 45 ного мультиплексора и выходом процессора, второй, третий, четвертыйи пятый информационные входы адрес"ного мультиплексора подключены соответственно к второму и третьемувыходам регистра команд, выходу счет"чика команд и адресному входу процессора, первый информационный входпроцессора соединен с информационны"ми входами счетчика команд и регистра команд, первыми информационнымивходами входного коммутатора, первого и второго коммутаторов связи,первый, второй, третий, четвертыйи пятый информационные входы и выход первого операционного блокаподключены соответственно к первомуинформационному входу процессора, вы.ходу первого коммутатора связи, первому информационному входу процессора, выходу п-го операционногоблока, первому и четвертому информационным входам второго операционногоблока, первый, второй, третий и пятыйинформационные входы -го операционного блока (1(1(п) подключены к перво"му информационному входу процессора, четвертый информационный вход ивыход 1-го операционного блока соединены соответственно с выходом(д)-го операционного блока и четвертым информационным входом (1+1) -гооперационного блока, первый и второйинформационные входы и-го операционного блока соединены с первым информа"ционным входом процессора, третий,четвертый и пятый информационныевходы и-го операционного блока соединены соответственно с выходом второго коммутатора связи, выходом(и) -го операционного блока и вторыминформационным входом процессора,вторые информационные входы первогои второго коммутаторов связи подключены к управляющему входу процессора,дополнительно введены регистр множителя, регистр множимого, группа мульУтиплексоров данных, элемент ИЛИ и группа управлянюцих мультиплексоров,с вторым выходом выходного коммутатора, управляющие и информационныевходы и выходы мультиплексоров дан"ных группы подключены соответственнок второму выходу выходного коммутатора, первому информационному входупроцессора и информационному входу регистра множителя, управляющий входи выход которого соединены соответ 1108446ственно с вторым выходом выходного коммутатора и первым информационным входом первого управляющего мультиплексора, вход и выход элемента ИЛИ подключены соответственно к выходу регистра множителя и второму информационному входу входного коммутатора, информационный и управляющий входы регистра множимого соединены соответственно с первым инфор мационным входом процессора и вторым выходом выходного коммутатора, выходы регистра множимого и адресного мультиплексора подключены к первым и вторым информационным входам соответствующих управляющих мультиплексоров группы, а выходы управляющих мультиплексоров группы соединены с адресными входами соответствующих операционных блоков.Кроме того, операционный блок содержит четыре операционных модуля, включающих блок памяти, два адресных коммутатора, узел Формирования переноса, регистр числа, регистр операнда и коммутатор данных, управляющий вход, первый, второй, третий и четвертый информационные входы ко. торого соединены соответственно с управляющим входом, первым вторым третьим и пятым информационнымй входами блока, управляющий и информационный входы регистра операнда подключены соответственно к управляющему и первому информационному входам блока, управляющий и информационный входы и выход регистра числа соединены соответственно с управляющим входом блока, выходом коммутатора данных и информационным входом блока памяти, адресный вход которого подключен к адресному входу блока и выходам первого и .второго адресных коммутаторов, первый информационные и управляющие входы которых соединены соответственно с адресным и управляющим входами блока, управляющий вход и выход блока памяти подключены соответственно к управляющему входу блока и информационному входу регистра операнда, вторые входы первого и второго адресных коммутаторов соединены соответственно с выходом регистра операнда и четвертым информационным входом блока, первый, второй и третий входы и выход узла формирования переноса подключены соответственно к четвертому информа 50 55 дами 31-35 и управляющим входом 36, вход 35 является адресным входом процессора, регистр 37 команд с информационным и управляющим входами 38 и 39, первым, вторым и третьим выходами 40, 41 и 42, счетчик 43 команд с информационным и управляющим входами 44 и 45, бпок 46 микро - программного управления с первым, вторым и третьим входами 47, 48 и 49и выходом 50, счетчик 51 микрокомандс первым и вторым информационными ционному входу блока, выходу регистраоперанда, выходу регистра числа и выходу блока.Иа фиг. 1 приведена структурная5 схема предлагаемого табличногопроцессора; на фиг, 2 - структурная схема операционного блока; нафиг. 3 - пример реализации узла формирования переноса; на фиг. 4 - при- .О мер реализации связей между блоками через шину данных; на фиг. 5пример реализации группы управляю"щих мультиплексоров; на фиг, 6пример реализации адресного мульти плексора; на фиг. 7 - пример реализации счетчика микрокоманд; на. Фиг. 8 - временная диаграмма работыпроцессора; на фиг. 9 - примерреализации выходного коммутатора;20 на фиг, 10 - размещение таблиц впамяти; на фиг. 1 - схема преобразований для формирования адреса при обращении к таблицам умножения; на Фиг. 12 - схема алгорит ма умножения.Устройство содержит операционнья блок 1,первый-пятый информационные входы 2 - 6, управлякяцийи адресный входы 7 и 8, выход 9 щ операционного блока 1, шину 10 данных, первый информационный вход 1процессора, мультиплексоры 12 данных с информационными и управляющими входами 13 и 14, регистр 15множимого с информационным и управляющим входами 16 и 17, регистр 8множителя с информационным 19 и управ .ляющим 20 входами, элемент ИЛИ 21,первый управляющий мультиплексор 22 40группы с первым и вторым информационными входами 23 и 24 и управляккцимвходом 25, второй - (и+1)-й управляющие мультиплексоры 26 группы спервым и вторым информационными входами 27 и 28 и управляющим входом 29, адресный мультиплексор 30с первым - пятым информационными вхо08446 7 11 входами 47 и 52, счетным и управляю. щим входами 53 и 54, блок 55 памяти микропрограмм с адресным и управляющим входами 56 и 57, регистр 58 микрокоманд с информационным и упрйвляющим входами 59 и 60, первым и вторым выходами 61 и 62,генератор 63 тактовых импульсов, выходной коммутатор 64 с первым и вторым входа ми 65 и 66, первым и вторым выходами 54 и 50, выход 50 коммутатора 64 является выходом блока 46 микропрограммного управления, входной коммутатор 67 с информационными входами 48, 49 и управлякюцим входом 68, первый коммутатор 69 связи с первым и вторым информационными входами 70 и 71 и управляющим входом 72, второй коммутатор 73 связи с первым и вторым информационными входами 74 и 75 и управляющими входами 76,. выход 77 процессора, операционный модуль 78 (фиг. 2), первый - пятый информационные входы 79-83, управляющий и адресный входы 84 и 85, выход 86 модуля 78, блок 87 памяти (одноразрядный) с информационным, адресным и управляющим входами 88, 89 и 90 и выходом 91, первый адресный,коммутатор 92 с первым и вторым информационными входами 93 и 94 и управляющим входом 95, второй адресный комму. татор 96 с первым и вторым информационными входами 97 и 98 и управляющим входом 99, узел 100 формирования переноса с первым, вторым и третьим входами 101, 102 и 103, регистр 104 числа с информационным и управляющим входами 105 и 106, регистр 107 операнда с информационным и управляющим входами 108 и 109, коммутатор 110 данных с первым, вторым, третьим и четвертым информационными входами 111, 80, 81 и 83 и управляацим входом 112, элемент 2 И-НЕ 113 (фиг,З), элемент ЗИ-НЕ 114, селектор-мультиплексор 115 на четыре канала (фиг. 4 и 6), элемент 2 ИИИЛИ 116 (фиг,5), элемент НЕ 117, счетчик 118 (фиг.71 со счетным и информационным входами 119 и 120 и входом 121 синхронизации, элемент 2 И 122 с входами 5.3 и 125, мультиплексор 123 на два канала с информационными входами 47 и 52 и управляющим входом 124, эле" мент И 126 (фиг. 9), элемент ИЛИ 127. 8Рассмотрим работу блоков операционного модуля 78 (фиг.2). Одноразрядный блок 87 памяти работаетв трех режимах в зависимости от кода7 О 2: 1 на управляющем входе 90при 7 О = 00 - режим хранения инфор"мации, при этом у =К; при 7 =10 - режим чтения, при этомУ у : =Н (А), А = Х цр 1 при у рорежим записи, при этом Н(А): хэ,А = Хэ, где Н(А) - содержимоеячейки накопителя с адресом А;х э - переменная на входе 88,Х - код на входе 89; у - переменная на выходе 91 (может приниматьтри значения - О, 1 и К, где К - со.стояние большого выходного сопротивления) .Код адреса Х имеет ш разрядов20и получается из трех кодовХ шф 13 Х ш 4 фу У 2 ф 1,где Х ш:4 - старшие шразряда кода, подаваемого навход 8;25У - сигнал на выходе второ 96го адресного коммутатора 96;У 2 2:13- код на выходе первогоадресного коммутато 30ра 92ф - знак конкатенации.Первым адресный коммутатор 92 переключает на выход код Х 2:1 либо код Х 4 2:1 в эавйсимости от35 сигнапа Б на управляющем входе 95: при Ц ф 0 - У 2 й 1 Д =Х 2 й 1 Д=Уэ 2:1,при П1 - У 2:1=Х 231 У У409 .Э 2ЭФ1 о 104где ур усигналы на Выходах регистра 104 числа и регистра 107операнда,Работой втброго адресного коммму 45 татора 96 управляет сигнал на управляющем входе 99: при Б = - у:х Х 1.3,ПМ=- УЭЬ:"хэ=хЕ 2 50где х - сигнал переноса из соседнего младшего разряда, поступающийна вход 82.Адресные коммутаторы 92 и 96 позволяют осуществлять независимую ад" 55 ресацию ячеек накопителя в различныхразрядах в пределах сегмента иэ четырех либо иэ восьми ячеек, что ис"пользуется при табличной реализации1 08номер 1 переключаемого разрядасоответствует двоичному коду Ч на управляющем входе 14 : 1 = Ч , НаИфиг. 4 приведен пример реализации мультиппексоров 12 данных для 4 п=16 (4 п - число разрядов в шине 10 данных). Они работают следующим образом:приЧ =00-Х . =У 4;1,3 офпри Ч 4 = 01 - Х . = У 1 Г 8:53,при Ч,+= 10 - Х.. = У 1 О 12:97,при Ч, = 11 - Х : = У 6:13,Регистры множимого 15 и множителя 18 работают в двух режимах: хранения информации - при нулевых значениях управляющих сигналов и записи - при единичных значениях управляющих сигналов. 20Первый управляющий мультиплексор 22 группы предназначен для формирования четырех младших разрядов кода ад" реса Х 4:1, подаваемых на все и операционных блоков 1 и в них на вхо ды 85 всех 4 п операционных модулей 78 Мультиплексором 22 управляет сигнал 0 на управляющем входе 25: при Б =0 на выход переключается код, подаваемый на первый информационный30 вход 23, ему соответствует код на выходе регистра 18У 4:3:=Х, С 4:13=У, Г 4:13, при П =1 на выход переключается код, подаваемый на второй информационный вход 24, ему соответствуют четыре мпадших разряда на выходе мультиплексора 30 адресных кодовУ 2 4:1: =ХУ 44: 11 =УЗР 4:140 .деУ ь 30 ь Уд дах мультиплексоров 22, 30 и регистра 18.Второй - (п+1)-й управляющие мультиплексоры 26 группы предназначены для формирования пятого-восьмого разрядов кода адреса независимо в п операционных блоках. Для этого четырехразрядные выходы мультиплексоров 26 подключены к пятому-вось мому разрядам щ-разрядных входов 8 соответствующих операционных блоков. Выход регистра 15 множимого, содер-. жащий 4 п разрядов (по четыре разряда соответственно) подключен к входам 27 мультиплексоров 26, а входы 28 у всех мультиплексоров 26 объ. единены и подключены к пятому-вось"при Ч =00 при Ч =01 при Ч ь =10 У щ 1 В ХУуоВ Хуэ 446 12мому разрядам выхода адресного муль"типлексора 30, Работой мультиплексоров 26 управляет сигнал П на29 объединенных управляющих входах 29при П = 0 - Уь 4:13: Ху .4:1при этом на пятый-восьмой разрядывходов 8 во все и операционных блоков 1 подаются коды, соответствующие 1, 2, , и-й четверкам разрядов кода на выходе регистра 15 множимого 15; при Б =1 - У 4:1 = У 18:5, на пятый-восьмой разряды входов 8 во все и операционных бло"ков 1 подается одинаковый код У 8:51 с выхода адресного мультйплексора 30.На фиг. 5 приведен пример реализации управляющих мультиплексоров 22 и 26. Адресный мультиплексор 30 предназначен для формирования щ-разрядныхладресных кодов с использованием информации от различных источников:регистра 37 команд, счетчика 43 команд и блока 46 микропрограммногоуправления. Мультиплексор 30 имеетчетыре щ-разрядных информационныхканала, Первому информационному ка"налу В 1 щ:1соответствует второйинформационный вход 32, второму каналу В- вход 33, третьему В3вход 34, четвертому В - два вхо"Фда 31 и 35, При этомВ 1 13 "Хщ:1 ",Ищ:11.Вщ:3 = Х,щ;13 = Х щ:11В,щ:3 = Х щ 3 = 4,щ:13,В щ:11 = С щ:11 ф Х 10: 11, где У+1, У 4, УЬЗ - коды на выходах 41 и 42 регистра 37 команд и на выходе счетчика 43 команд; С щ: 11-(щ- О) - разрядный фикси. рованный код 00 на входе 35; Х 110: 1 - 1 О - разрядный код, подаваемый на вход 31 из блока 46 микропрограммного управления.Код С = 00 соответствует адресу начального сегмента накопителя, содержащего 1024 ячейки, к которым возможна адресация от блока 46 микропрограммного управления.Работой адресного мультиплексора 30 управляет код Ч на управляэьющем входе 36:13 1Ч 1 -у; В ХцприЧ 11-У . -ВНа фиг, 6 приведен пример реализации адресного мультиплексора 30 при ше 2;Регистр 37 команд работает в двух режимах: хранения (при 0 0) и записи (при 05). На информационный вход 38 поступает и-разрядный код иэ шины О данныхСчетчик 43 команд работает в трех режимах: при 0 4ОО - хранение информации; при 0 щ 01 - запись, ш-разрядного кода, поступающего на информационный вход 44," при 0" 10модификация кода в счетчике 43 прибавлением единицы, Информационный вход подключен к ш разрядам шины 10 данных соответствующим положению адреса перехода в командах безусловного перехода.Первый коммутатор 69 связи предназначен для управления передачей информации в первый (младший) раэ" ряд при сдвиге на один разряд: 25 при 0 = 0 - уэ: хопри 0.ф= 1 указ ф хя фВход 7 б подключен к 4 п-му разряду шины 10 данных, выходной сигнал учерез вход 3 первого операционного блока 1 поступает на вход 80 коммутатора 110 в первом операционном модуле 78 и далее на вход 105 регистра 104 числа. С использованием этих связей в регистр числа передается с циклическим сдвигом на один разряд влево число, считан- ное из памяти в шину О данных.Вход 71 коммутатора 69 является управляющим входом процессора, на который подается О. Сигнал х 071 используется при арифметическом сдви ге влево и записывается по описанным связям в первый разряд регистра 104 числа.Второй коммутатор 73 связи предназначен для управления передачей информации в старший разряд при сдвиге вправо на один разряд: при 0 " 0 - у 1 щх.,при 0- у х,1 хт О.Вход 74 подключен к первому разряду шины О данных. Выходной сигнал у- через вход 4 п-го операцион 3 Фного олока 1 поступает на вход 81 08446 14коммутатора 1 О данных в 4 п-м опера-ционном модуле 78 и далее на вход 105регистра 104 числа. С использованиемэтих связей, в регистр числа передается с циклическим сдвигом на одинразряд вправо число, считанное изпамяти в шийу 10 данных. Сигналхщ 0 используется при арифметическом сдвиге вправо и записывает"1 О ся по описанным связям в 4 п-й разряд регистра числа.Счетчик 51 микрокоманд работаетследующим образом:115 ф 4при У 3:1 000 режим хранения информации;при Ч щ 001 - запись в счетчик 5164кода, подаваемогона вход 47;при Ч =010 - запись в счетчик 514кода, подаваемого. на вход 52;при Ч =ИО - запись в счетчик ко 4да, подаваемого навход 52 из регистрамнкрокоманд, и последующее прибавлениек содержимому счетчика 5 одноразрядного кода 0 е0,1.30На фиг. 7 приведен пример реализации счетчика 51, При этом 0ЧР 1, 0 1, Ч 4 23, 0ш Ч 4 Д 33. Мультиплексор 123 работает следующим образом.35при 014 1 - 7: Х,юпри 0 ,4 0 У,1Х 2,Блок 55 памяти микропрограмм при400=1 осуществляет чтение содержимого ячейки накопителя по адресуА = Х. Считанный код микрокоманды поступает на вход 59.Регистр 58 микрокоманд работа 45ет в двух режимах: при 0= 0 - режим хранения информации; при 0 = 1 режим записи кода микрокоманды, подаваемого на вход 59.Входной коммутатор 67 предназначен для выбора одного из осведоми 50 тельных сигналов, в зависимости отзначения которого выполняется модификация содержимого счетчика 51 микрокоманд при реализации условныхпереходов в микропрограммах, Коммутатор 67 имеет четыре информационных канала, Первому каналу соответствует сигнал х+ на входе 49,поступающий с выхода элемента ИЛИ 2 1,при ЧЕ - 00 - у 67 = хпри ЧЬЭ = 01 - 67 фзпри ЧЬЬ 10 - у 67 Х 462при ЧЬ = 1 - у = Х 33.Микрокоманда имеет два поля: адреса перехода к следующей микроко маиде и управляющих сигналов. Код адреса следующей микрокоманды с первого выхода 61 регистра 58 микрокоманд поступает на второй информационный вход 52 счетчика 51 20 микрокоманд. Код управляющих сигналов с второго выхода 62 поступает на второй вход 66 выходного коммутатора 64, в котором осуществляется синхронизация управляющих сигналов тактовыми импульсами в соответствии с требуемой временной диаграммой. Тактовые импульсы вырабатываются генератором 63 и подаются на первый вход 65 выходного комму татора 64.В процессоре используется синхронная организуя работы, при которой выборке и выполнению каждой микрокоманды соответствует один цикл,35 разбитый на такты. Требования к временной диаграмме внутри цикла определяются в основном особенностями элементов, используемых в качестве блоков 87 памяти (фиг. 2), а также элементов, используемых в блоке 55 памяти микропрограмм. На фиг. 8 приведен пример временной диаграмж работы процессора. Каждый цикл Тв разбит на три тактаарве тактисполь 4 зуется для считывания очередной микрокоманды из блока 55 по адресу, поступающему на вход 56 из счетчика 5 микрокоманд. Считанная микро- команда в первом же такте записыва ется в регистр 58 микрокоманд, Длительность такта с должна превышать время переходных процессов в блоках 55 и 58. Второй и третий такты (С 2 и Сз) используются для обращения к блокам 87 памяти. Сигнал Ч 1,2. разрешения обращения к блоку 87 памяти имеет длительность О 25 15 1108 второму, третьему и четвертому каналам соответствуют сигналы Х 3:13, поступающие с выхода 9 старшего п-го операционного блока, а также иэ 4 п-го и первого разрядов шины5 10 Данных. Коммутатор 67 работает следующим образом: 446 16двух тактов С и ТЭ , он иницииру" ет работу встроенных в блоки 87 узлов управления. Длительность второго такта Т должна превышать время переходных процессов в узлах управления, дешифраторах адреса и коммутирующих ключах, встроенных в блоки 87 памяти (БИС, ОЗУ), В третьем тактеосуществляется запись кода на выходах регистра 104 числав блоки 87 памяти, в этом же такте осуществляется модификация содер" жимого счетчиков команд и микроко" манд. На фиг. 8 показана иаграммасигналов, используемых для синхроии" зации различных управляющих сигналов в табличном процессоре. Часть сигналов (Ч 14 ф П 2 ф 0Х ю Ч 1, ЧЬ П,5, 099, Ч требует синхронизации. Эти сигналы изменяются в момент записи считовной иэ блока 55 информации в регистр 58 микрокоманд, что отмечено на времен"ной диаграмме.Распределим положение управляющих сигналов в формате микрокоманды (Ч 62) и в коде управляющих сигналов Чо на выходе выходного коммутатора 64.Для кода Ч 1 на управляющем входе 7 операционного блока (фиг, 2) примемЧ 7 .8: 1, =Ч.зо 1,2:1 в 010 о 0105 о 095 фБ 9 о Ч,2 21,Для кода Ч на выходе 50 выходного коммутатора 64Ч34;13 =Ч 34;1030 Чвв Г 911- (У;,ф 029 о 0 ОЧ 4: 1 о Ц 7 о П 72 о Щ Г 13 о Ч, 2 11 о Х,О 13 юоЧьВ .2:11) (7 8:53017 П 20ф 1 взоЧ 45 2:1,)В коде Чу выделены две части: старшие двадцать пять разрядов соответствуют несинхронизированным сигналам, а девять младших - синхронизированным. Сигнал Ч341 соот ветствует сигналу "Переполнение" и поступает на выход 77 процессора, Установим соответствие между кодом Ч 1, . на выходе регистра 58, кодами Ч 4, и . Ч 0 на выходах 54 и 50 и тактовымй импульсами ЧВ 5 3:13 на выходе генератора 63 тактовых импульсов.Согласно временной диаграмме (фиг.8) на управляющие входы 57 и 60 подается первый тактовый им

СмотретьЗаявка

3457102, 24.06.1982

ЛЕНИНГРАДСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. М. И. КАЛИНИНА

МЕЛЕХИН ВИКТОР ФЕДОРОВИЧ

МПК / Метки

МПК: G06F 9/00

Опубликовано: 15.08.1984

Код ссылки

<a href="https://patents.su/24-1108446-tablichnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Табличный процессор</a>

Предыдущий патент: Интегро-дифференциальный вычислитель

Следующий патент: Микропрограммное устройство управления модуля вычислительной системы

Случайный патент: Уплотнение вала насоса