Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1252775

Авторы: Колесников, Никольский, Сперанский, Тимонькин, Ткаченко, Улитенко, Харченко

Текст

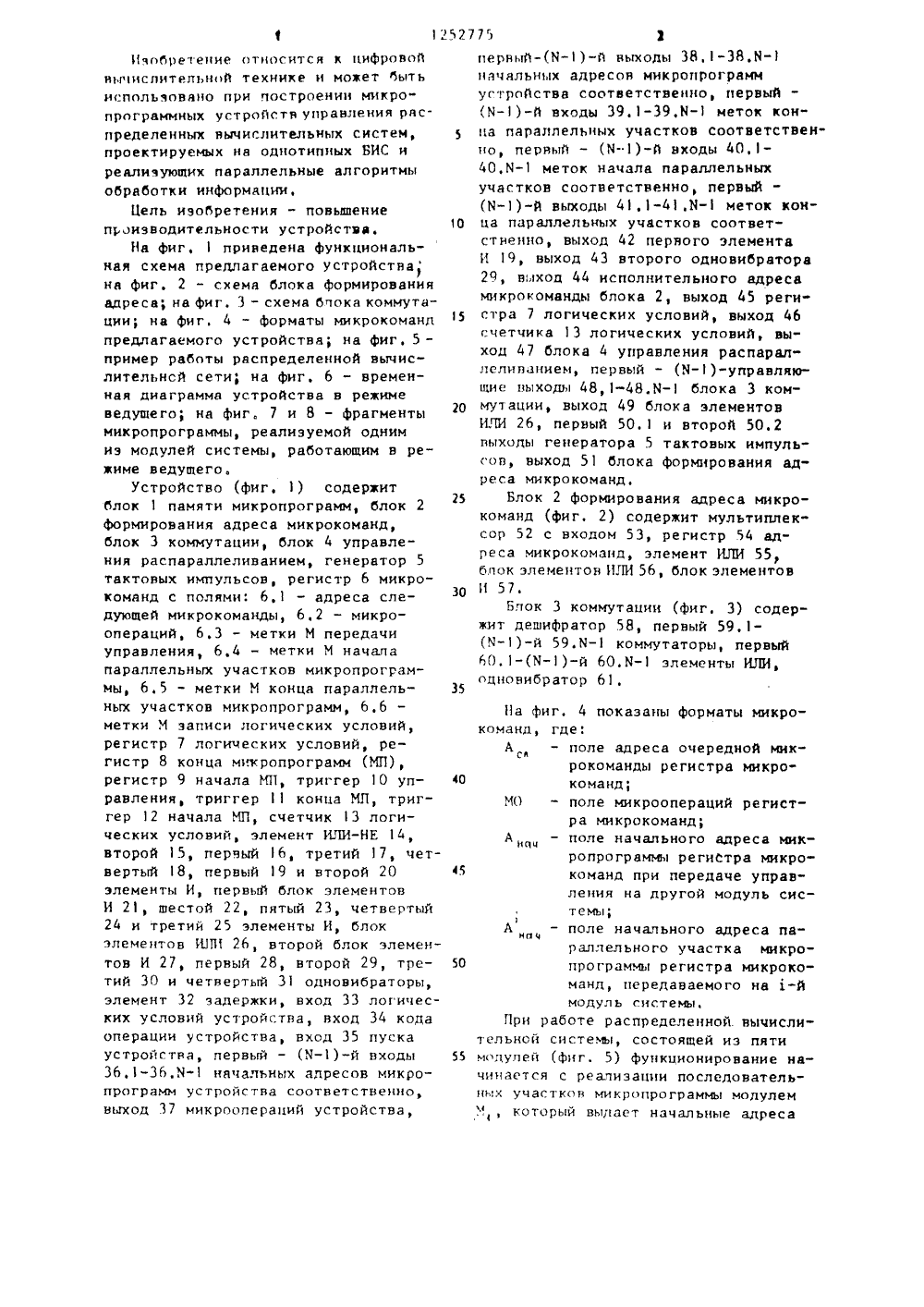

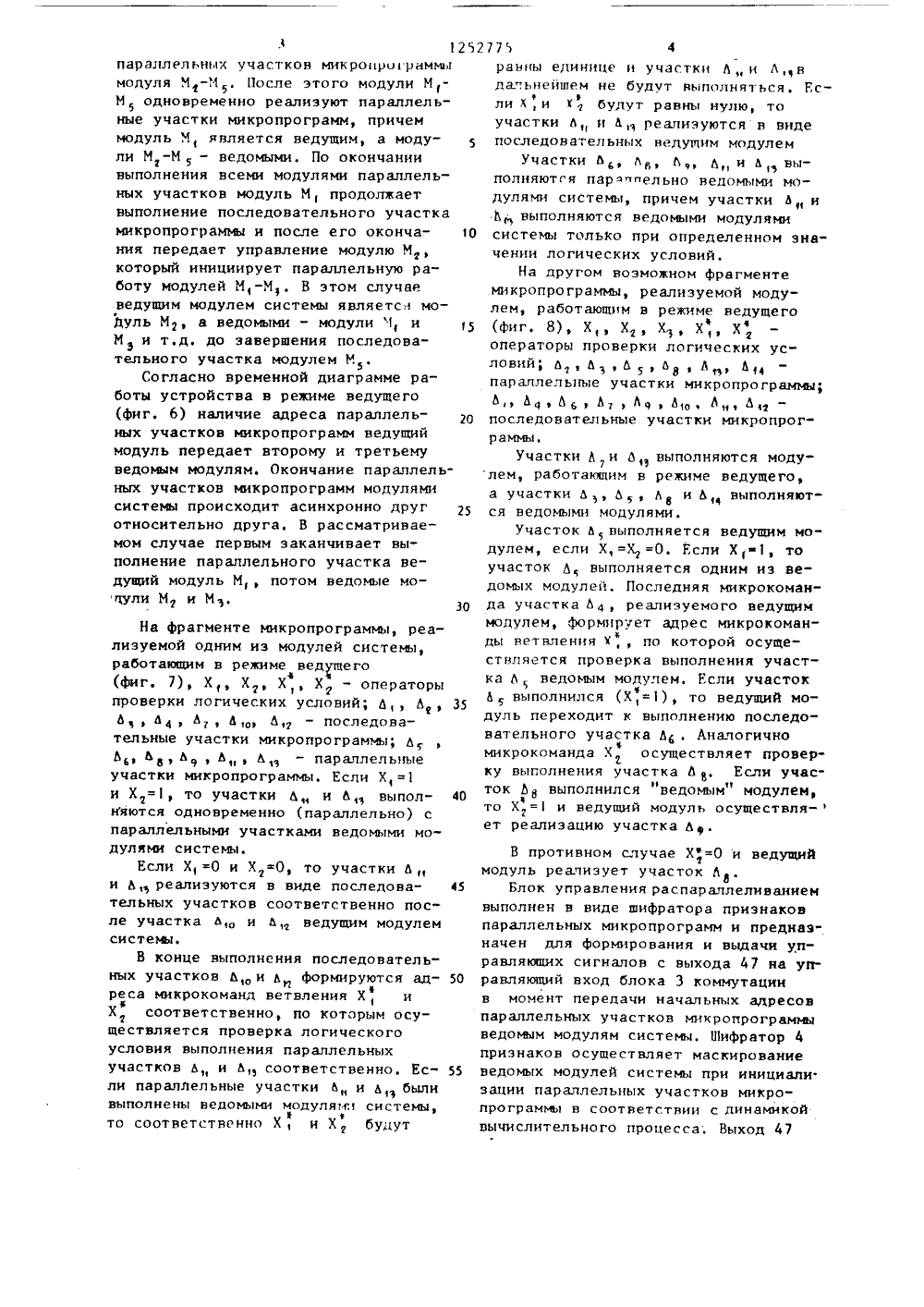

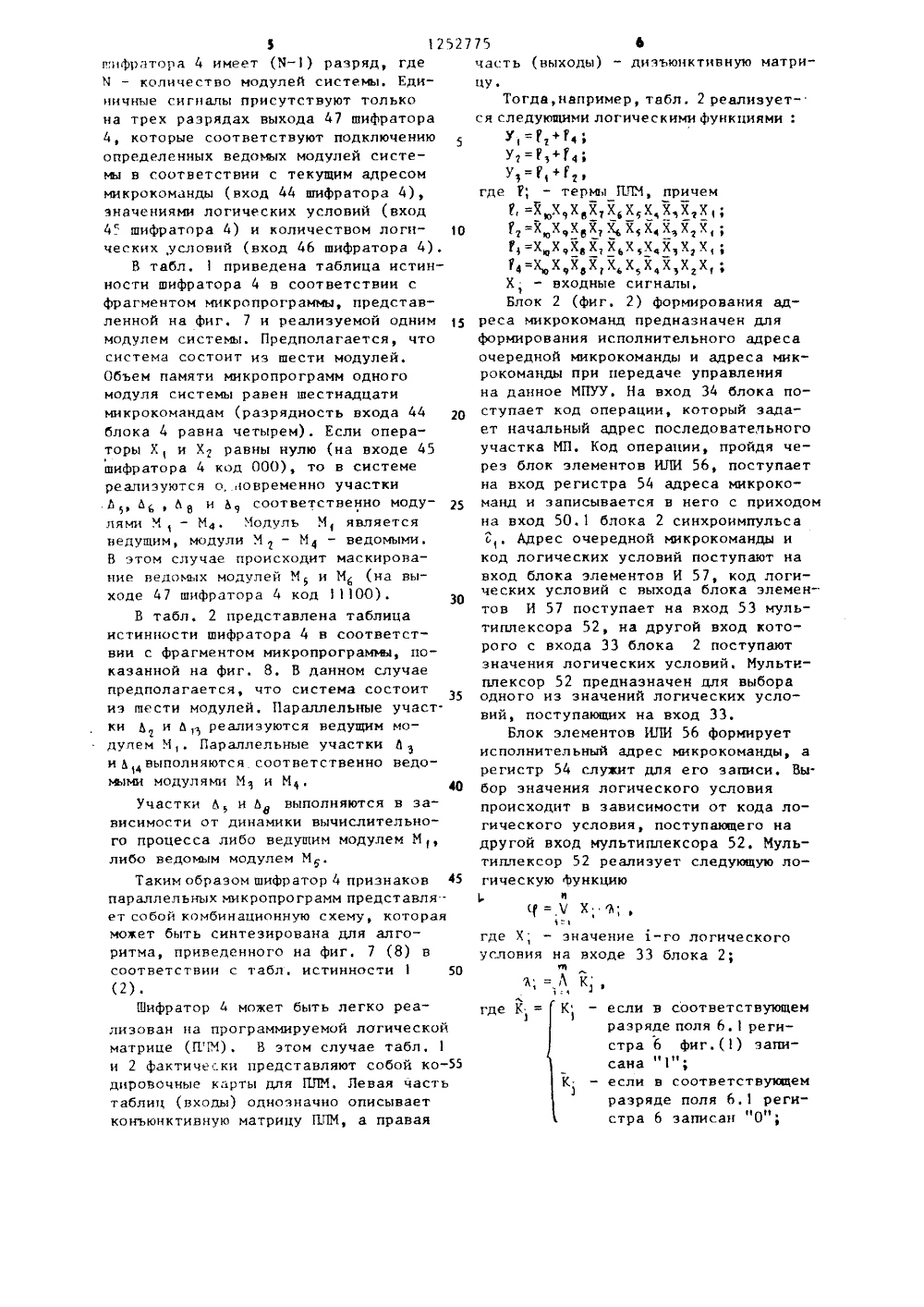

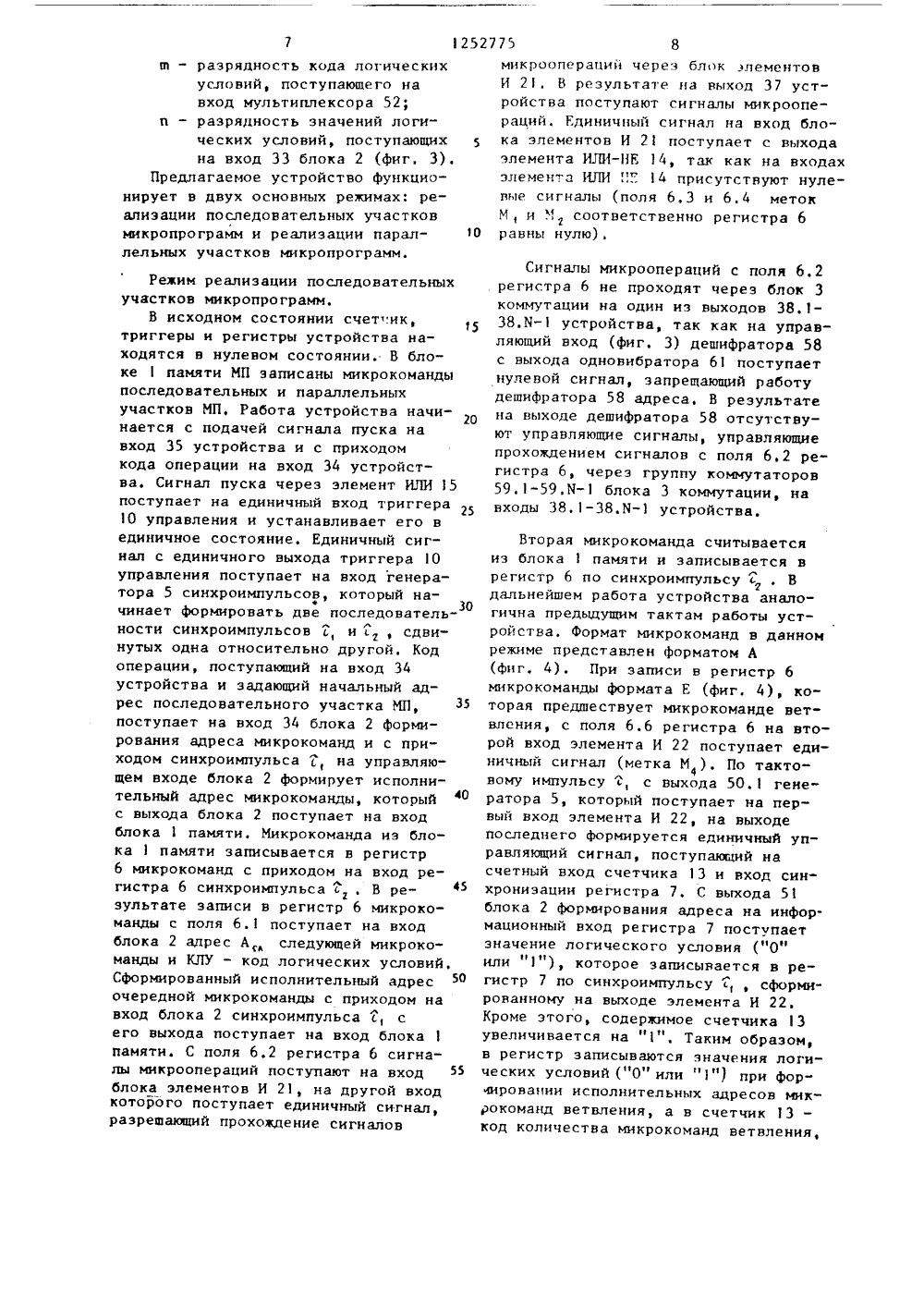

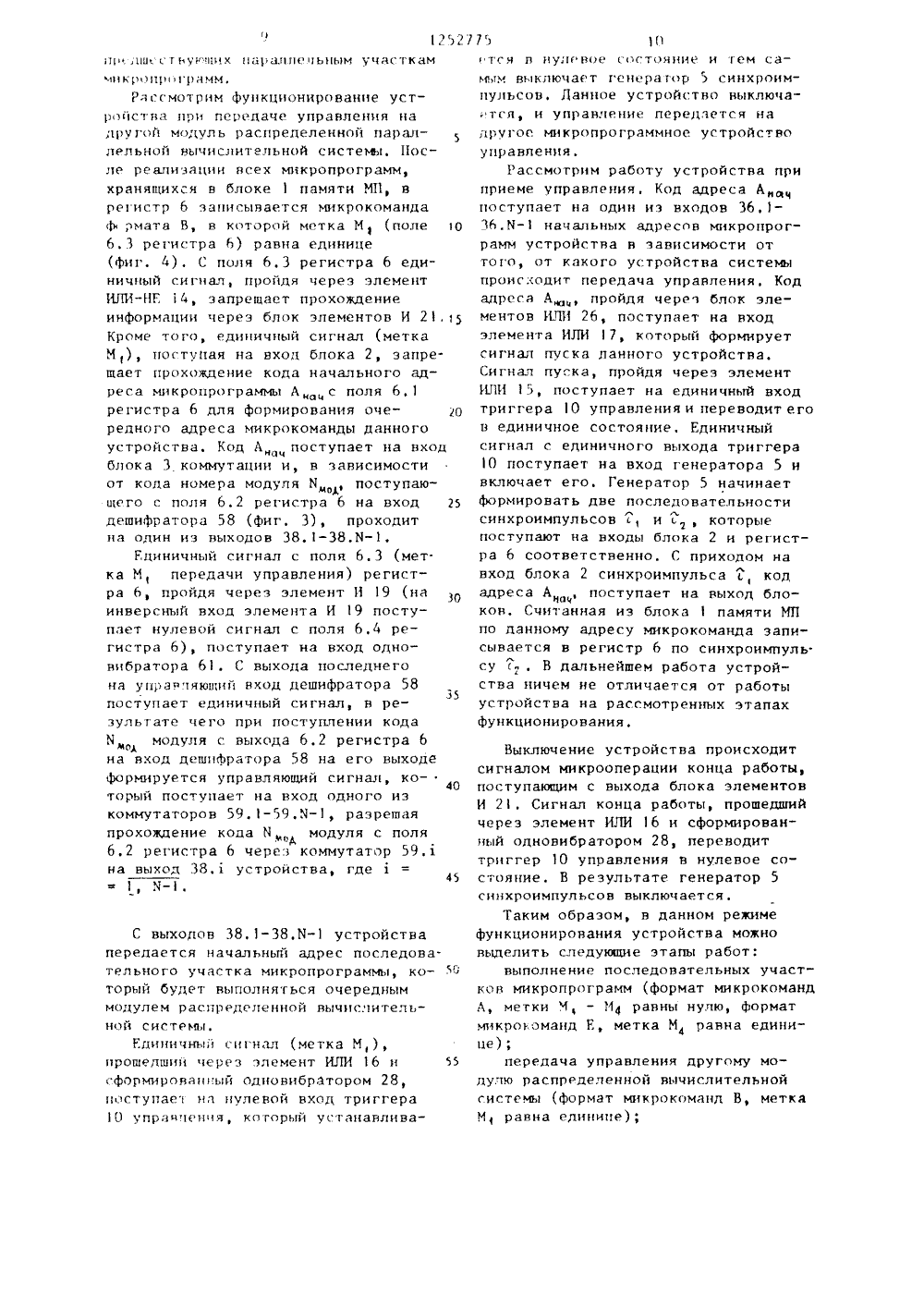

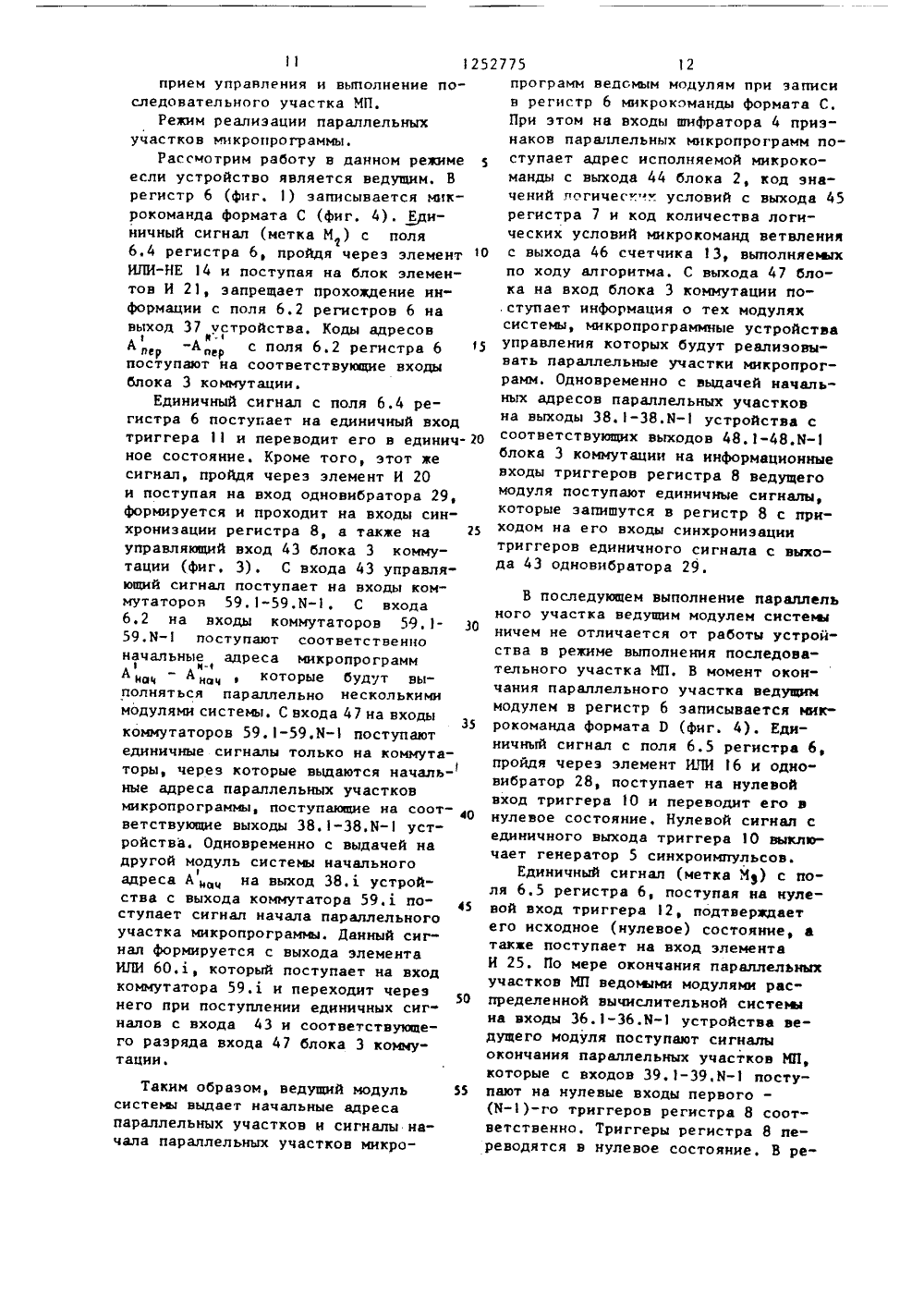

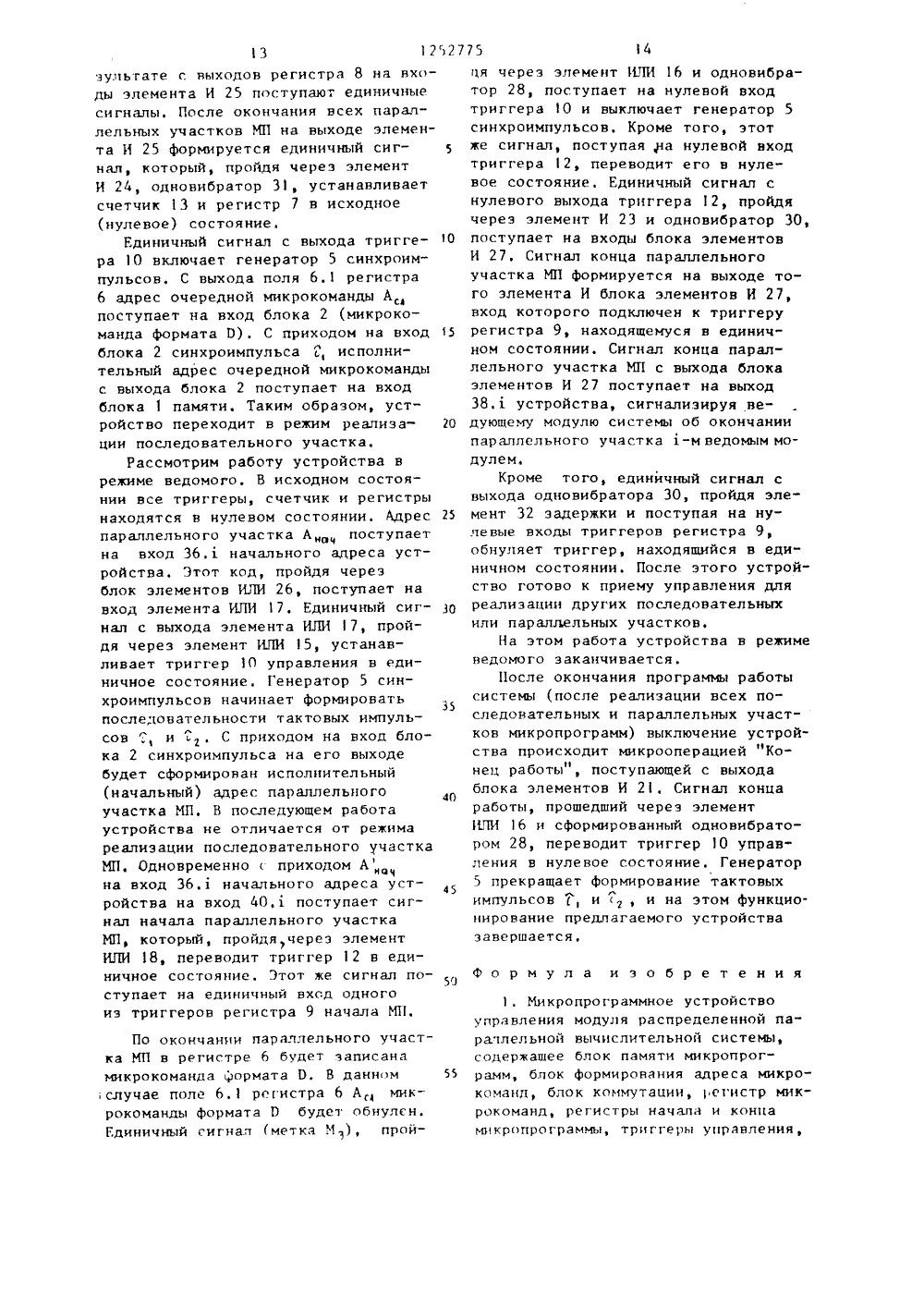

(50 4 С 06 Р 9 ДАРСТВЕННЫЙЕЛАМ ИЗОБРЕТ ЕТ СССРОТНРЫТЮ 1 НИЕ ИЗОБРЕТЕНИ ВУ ВТОРСКОМ И ТЕЛ еленй сис ачалаинкророй-.(56) Авторское свидетельство СССР В 959080, кл, С 06 Р 9/22, 1982,Авторское свидетельство СССР В 1168936, кл. С 06 Г 9/221983, (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ МОДУЛЯ РАСПРЕДЕЛЕННОЙ ПАРАЛЛЕЛЬНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕ(57) Изобретение относится к облас ти цифровой вычислительной техники и может быть использовано при построении микропрограммных устройст управления распределенных вычислительных систем, проектируемых на одиотиповых БИС и реализующих параллельные алгоритмы обработки информации. Целью изобретения являет ся повышение производительности устройства. Микропрограммное уст ство управления модуля распредной параллельной вычислительнотемы содержит блок памяти микропрограмм, блок формирования адресамикрокоманд, блок коммутации,регистр микрокоианд, регистр нмикропрограммы, регистр концапрограммы, триггер управления,триггер конца микропрограммы, триггер начала микропрограммы, генератор тактовых импульсов, первый, второй, третий и четвертый элементыИЛИ, блок элементов ИЛИ, элементИЛИ-НЕ, первый, второй, третий, четвертый и пятый элементы И, первыйи второй блоки элементов И, элементзадержки, первый, второй, третийи четвертый одновибраторы, регистрлогических условий, счетчик логических условий, шестой элемент И,шифратор признаков параллельныхмикропрограмм. Введение регистралогических условий, счетчика логических условий, шестого элемента Ии шифратора признаков параллельныхмикропрограмм обеспечивает достижение цели. 1 з.п. ф-лы, 8 ил,1252775 17 18 Таблица 1 тВход 45 Вход 46 Выход 47 Вход 44 ХХХХХХХ 011 11111 010 0100 010 Г) 000 010 11100 выход которого соединен с входомчетвертого одновибратора, выход которого соединен с входом установкив 0 триггера конца микропрограммыи третьим входом второго элементаИЛИ, с первого по (М)-й выходы вто.рого блока элементов И соединены спервого по (М)-й выходами признаков конца параллельных участков микропрограмм устройства соответственно, с первого по (М)-й выходыпервой группы блока коммутации соединены соответственно с первого по(М)-й информационными входами регистра конца микропрограмм, инверсные выходы с первого по (М)-й которого соединены соответственно с второго по М-й входами третьего элемента И, с первого по (М)-й выходывторой группы блока коммутации соединены соответственно с первого по(М)-й выходами начальных адресовмикропрограмм ведомых модулей устройства, выход признака конца работыпервого блока элементов И соединен 25с третьим входом первого элементаИЛИ, о т л и ч а ю щ е е с я тем,что, с целью повышения производительности, оно дополнительно содержитшифратор признаков параллельных мик- Оропрограмм, регистр логических условий, счетчик логических условий,шестой элемент И, причем выход признака режима работы блока формирования адреса соединен с информационным Звходом регистра логических условий,выход поля записи логического условия регистра микрокоманд соединенс первым входом шестого элемента И,первый выход генератора тактовыхимпульсов соединен с вторым входомшестого элемента И, выход которогосоединен с входом синхронизации регистра логических условий и счетнымвходом счетчика логических условий,выход регистра логических условийсоединен с первым информационнымвходом шифратора признаков параллельных микропрограмм, выход четвертого одновибратора соединен с входамиустановки в 0" регистра логическихусловий и счетчика логических условий, выход которого соединен с вторым информационным щсодом шифраторапризнаков параллельных микропрограмм, информационный выход блокаформирования адреса соединен с третьим управляющим входом шифраторапризнаков параллельных микропрограмм, выход которого соединен стретьим управляющим входом блокакоммутации.2, Устройство по и. 1, о т л и ч а ю щ е е с я тем, что блок ком,мутации содержит шифратор адреса, с первого по (М)-й элементы ИЛИ, с первого по (М)-й элементы И, с первого по (М)-й элементы 2 И-ИЛИ, одновибратор, причем первый вход блока соединен с первыми входами с первого по (М)-й элементов 2 ИИЛИ, выходы которых соединены соответственно с первого по (М)-й выходами первой группы блока, второй вход блока соединен с вторыми входами с первого по (М)-й элементов 2 И-ИЛИ, с информационным входом дешифратора адреса и с входами с первого по (М)-й элементов ИЛИ, выходы которых с первого по (М)-й соединены с выходами второй группы блока и с первыми входами с первого по (М-)-й элементов И, выходы которых соединены с первого по (М-)-Я выходами первой группы блока, третий вход блока соединен с вторыми входами с первого по (М)-й элементов И и с четвертыми входами с первого по (М)-й элементов 2 И-ИЛИ, четвертый вход блока соединен с входом одновибратора, выход которого соединен со стробирующим входом дешифратора, пятый вход блока соединен с третьими входами с первого по (М)-й элементов И и с.пятыми входами с первого по (Ч)-й элементов 2 И-ИЛИ.20 2527 Таблица 2 ХХХХ ХХХ щЧВ 7 УУУУУ,00100 00 0110 00101 000 000 0110 00010 00011 011 011 1100 011 010 100 Вход 44 Вход 45 Вход 46 Выход 47Составитель А Техред В.Када анасьевКоррект Саиборская Редактор В. Пет Тираа 671 Подпи НИИПИ Государственного комитета СССР по делан изобретений и открытий 035, Москва, Ж, Рауаская наб., д. 4/512527 30 Изобретение относится к цифровойвычислительной технике и может бытьиспользовано при построении микропрограммных устройств управления ряс.пределенных вычислительных систем,проектируемых на однотипных БИС иреализующих параллельные алгоритмыобработки информации,Цель изобретения - повышение10производительности устройства.Иа фиг. 1 приведена функциональная схема предлагаемого устройстнана фиг, 2 - схема блока формированйяадреса, на фиг, 3 - схема бока коммутации; на фнг. 4 - форматы микрокоманд5предлагаемого устройства; иа фиг. 5 -пример работы распределенной вычислительнсй сети; на фиг, 6 - временная диаграмма ус.тройства в режимеведущего; на фиг, 7 и 8 - фрагменты20микропрограммы, реализуемой однимиз модулей системы, работающим в режиме ведущего.Устройство (фиг. 1) содержит25блок 1 памяти микропрограмм, блок 2формирования адреса микрокоманд,блок 3 коммутации, блок 4 управления распараллеливанием, генератор 5тактовых импульсон, регистр 6 микрокоманд с полями: 6,1 - адреса следующей микрокоманды, 6,2 - микроопераций, 6,3 - метки М передачиуправления, 6,4 - метки М началапараллельных участков микропрограммы, 6.5 - метки М конца параллельных участков микропрограмм, 6.6метки М записи логических условий,регистр 7 логических условий, регистр 8 конца микропрограмм (МП),регистр 9 начала МП, триггер 10 управления, триггер 11 конца МП, триггер 12 начала МП, счетчик 13 логических условий, элемент ИЛИ-НЕ 14,второй 15, первый 16, третий 17, четвертый 18, первый 9 и второй 20 45элементы И, первый блок элементовИ 21, шестой 22, пятый 23, четвертый24 и третий 25 элементы И, блокэлементов ИП 26 второй блок элементов И 27, первый 28 второй 29, третий 30 и четвертый 31 однонибраторы,элемент 32 задержки, вход 33 логических условий устройства, вход 34 кодаоперации устройства, вход 35 пускаустройства первый - (М-)-й входы 5536,1-36,3- начальных адресов микропрограмм устройства соответственно,выход 37 микроопераиий устройства,15 2первый-(К- )-й выходы 38,1-38.К начальньх адресов микропрограммустройства соответственно, перный(1-)-й входы 39,1-39,Н- меток кон"ца параллельных участков соответственно, первый - (1-1)-й входы 40,140,1-1 меток начала параллельныхучастков соответственно, первый(Н)-Я выходы 41,1-41,11- меток конца параллельных участков соответственно выход 42 первого элементаИ 19, выход 43 второго одновибратора29, выход 44 исполнительного адресамикрокоманды блока 2, выход 45 регистра 7 логических условий, выход 46счетчика 13 логических условий, выход 47 блока 4 упранления распарал"леливанием первый - (1-1)-управляющие цыходь 481-48,1-1 блока 3 коммутации, выход 49 блока элементовИЛИ 26 первый 50,1 и второй 50.2выходы генератора 5 тактовых импульов выход 51 блока формирования ад"реса микрокоманд,Блок 2 формирования адреса микрокоманд (фиг. 2) содержит мультиплек"сор 52 с входом 53, регистр 54 адреса микрокоманд элемент ИЛИ 55блок элементов ИЛИ 56, блок элементовИ 51,Блок 3 коммутации (фиг, 3) содержит дешифратор 58, первый 59,1(1-1)-й 59.1-1 коммутаторы, первый60.1-(1-)-й 60.1-1 элементы ИЛИ,однонибратор 61,Иа фиг. 4 показаны форматы микро- команд где:А - поле адреса очередной миксрокоманды регистра микрокоманд;МО - поле микроопераций регистра микрокоманд;А- поле начального адреса микропрограммы региСтра микрокоманд при передаче управ"ления на другой модуль системы;А - поле начального адреса параллельного участка микропрограммы регистра микрокоманд, переданаемого на 1-ймодуль системы.При работе распределенной нычислнтельной систеж состоящей иэ пяти модупей (фиг. 5) функционирование начинается с реализации последовательных участков микропрограммы модулемкоторый выдает начальные адреса277 125 параллельных участков микропрограммы модуля М 1-М . После этого модули М- М одновременно реализуют параллель 5ные участки микропрограмм, причем модуль М является ведущим, а модули М-М- ведомыии. По окончании выполнения всеми модулями параллельных участков модуль М, продолжает выполнение последовательного участка микропрограммы и после его оконца- О ния передает управление модулю М, который инициирует параллельную работу модулей М,-М , В этом случае ведущим модулем системы являетси моДуль М, а ведомыми - модули 1, и 15 М з и т.д. до завершения последовательного участка модулем Мэ.Согласно временной диаграмме работы устройства в режиме ведущего (фиг. 6) наличие адреса параллельных участков иикропрограмм ведущий модуль передает второму и третьему ведомым модулям. Окончание параллельных участков микропрограмм модулями систеиы происходит асинхронно друг относительно друга, В рассматриваемом случае первым заканчивает выполнение параллельного участка ведущий модуль М потом ведомые мопули М и Мэ.30На фрагменте микропрограммы, реализуемой одним иэ модулей систеж, работающим в режиме ведущего (фиг. 7), Х Х 2, Х Х - операторы проверки логических условий; Л Л, 35Э Лз э Ь 4 в ЬЬ 1 ою Л 1 д - последовательные участки микропрограмм; Ь Лю ЛЬЬЭЬ, Ь, - параллельные участки микропрограммы. Если Х, =1 и Х 2=1, то участки Л и д выпол няются одновременно (параллельно) с параллельными участками ведомыми модулями системы.Если Х О и Х О, то участки Ьи д, реализуются в виде последова тельных участков соответственно после участка ь,о и д, ведущим модулем система.В конце выполнения последователь" ных участков д, н Ь формируются ад2Ф реса микрокоманд ветвления Х, иФХ соответственно, но которым осуществляется проверка логического условия выполнения параллельных участков Ь и Ь, соответственно. Ес ли паралЛельные участки Ь и Ь, были выполнены ведомыми модулялю системы,В Фто соответственно Х, и Хбудут равны единице и участки Ли Л,вдальнейшем не будут выполняться. ЕсФ )ли Х,и Х будут равны нулю, тоучастки ди д,э реализуются в видепоследовательных ведущим модулемУчастки Л 4, Ль, ЛЛ н Ь, выполняются пардпельно ведомыми модулями системы, причем участки Ьнвыполняются ведомыми модулямисистемы только при определенном значении логических условий.На другом возможном фрагментемикропрограммы, реализуемой модулем, работающим в режиме ведущего(фиг. 8), Х, Х 2, ХЭ, Х Х доператоры проверки логических условииф дд 1 д ф Ь ф Ь ф Ьипараллельные участки микропрограммы;Ь Ь 4 Ь 61 Ьч ) ЛэЬое Ля 1 Ле 2последовательные участки микропрограммыы,Участки Ь,и Ь, выполняются модулем, работающим в режиме ведущего,а участки д , Ь, Ь и Ьвыполняются ведомыми модулями.Участок Ь выполняется ведущим модулем, если Х, =Х =О. Если Х 1, тоучасток Л, выполняется однии из ведомых модулей. Последняя микрокоманда участка Ь 4, реализуемого ведущиммодулем, формирует адрес микрокоман%ды ветвления Х по которой осущестнляется проверка выполнения участка Л ведомым модулеи. Если участокЬ . выполнился (Х,=1), то ведущий модуль переходит к выполнению последовательного участка Л 6Аналогичномикрокоманда Х осуществляет провер 2ку выполнения участка Л 1. Если участок Л выполннлся "ведомым" иодулеи,%то Х 2= и ведущий модуль осуществля-ет реализацию участка Л. В противном случае Х=О и ведущий модуль реализует участок ЛЬ.Блок управления распараллеливанием выполнен в виде шифратора признаков параллельных микропрограмм и предназначен для формирования и выдачи управляющих сигналов с выхода 47 на управляющий вход блока 3 коммутации в момент передачи начальных адресов параллельных участков микропрограммы ведомым модулям системы, Шифратор 4 признаков осуществляет маскирование ведомых модулей системы прн инициали. эации параллельных участков микропрограмлв 1 в соответствии с динамикой вычислительного процесса. Выход 473 12527 г:ифратора 4 имеет (И) разряд, где Ч - количество модулей системы. Единичные сигналы присутствуют только на трех разрядах выхода 47 шифратора 4, которые соответствуют подключению определенных ведомых модулей системы в соответствии с текущим адресом микрокоманды (вход 44 шифратора 4), значениями логических условий (вход 4 шифратора 4) и количеством логи О ческих,услоний (нход 46 шифратора 4).В табл, 1 приведена таблица истинности шифратора 4 в соответствии с фрагментом микропрограммы, представленной на фиг. 7 и реализуемой одним 15 модулем системы. Предполагается, что система состоит из шести модулей. Объем памяти микропрограмм одного модуля системы равен шестнадцати микрокомандам (разрядность входа 44 70 блока 4 равна четырем). Если операторы Х и Хг равны нулю (на входе 45 шифратора 4 код 000), то в системе реализуются о, повременно участки ,Л, ЬЛ 8 и Ь соответстненно моду лями М, - М 4 Модуль М, является ведущим, модули М г - М 4 - ведомыми. В этом случае происходит маскирование ведомых модулей Ми М (на выходе 47 шифратора 4 код 11100).30В табл. 2 представлена таблица истинности шифратора 4 в соответствии с фрагментом микропрограюю показанной на фиг. 8. В данном случае предполагается, что система состоит иэ шести модулей. Параллельные участ. ки Ь и 6, реализуются ведущим модулем М,. Параллельные участки аз и Ь, выполняются соответственно ведомыми модулями Мз и М.40Участки Ь, и А выполняются в зависимости от динамики вычислительного процесса либо ведущим модулем М 7 либо ведомым модулем М.Таким образом шифратор 4 признаков 45 параллельных микропрограмм представляет собой комбинационную схему которая может быть синтезирована для алгоритма, приведенного на фиг7 (8) в соответствии с таблистинности 1 50(2).Шифратор 4 может быть легко реализован на программируемой логической матрице (П 1 М), В этом случае табл, 1 и 2 фактически представляют собой кодироночные карты для ПЛМ, Левая часть таблиц (входы) однозначно описывает конъюнктивную матрицу ПЛМ, а праваягде К К - если в соотнетствующемразряде поля 6. 1 регистра 6 фиг.(1) записана "1";К - если в соответствующемразряде поля 6.1 регистра 6 записан "0"; 75 Ьчасть (выходы) - дизъюнктивную матрицуеТогда,например, табл. 2 реализуется следующими логическими функциями:У, =Р,+Г ,У 741+ггде Г; - термы ПГИ причемХ Х Х 7 Х ХХ ХХ 7 ХХ, - входные сигналы,Блок 2 (фиг2) формирования адреса микрокоманд предназначен дляформирования исполнительного адресаочередной микрокоманды и адреса микрокоманды при передаче управленияна данное МПУУ. На вход 34 блока поступает код операции, который задает начальный адрес последовательногоучастка МП. Код операции, пройдя через блок элементов ИЛИ 56, поступаетна вход регистра 54 адреса микрокоманд и записывается в него с приходомна вход 50.1 блока 2 синхроимпульсаГ, Адрес очередной микрокоманды икод логических условий поступают навход блока элементов И 57, код логических условий с выхода блока элементов И 57 поступает на вход 53 мультиплексора 52, на другой вход которого с входа 33 блока 2 поступаютзначения логических условий. Мультиплексор 52 предназначен для выбораодного из значений логических условий, поступающих на вход 33.Блок элементов ИЛИ 56 формируетисполнительный адрес микрокоманды, арегистр 54 служит для его записи. Вы.бор значения логического условияпроисходит в зависимости от кода логического условия, поступающего надругой вход мультиплексора 52. Мультиплексор 52 реализует следующую логическую функциюс=,Ч Х,я,1где Х; - значение 1-го логическогоуслония на входе 33 блока 2;А;=Ь К;,1лш - разрядность кода логическихусловий, поступающего навход мультиплексора 52;п - разрядность значений логических условий, поступающихна вход 33 блока 2 (фиг3).Предлагаемое устройство функционирует в двух основных режимах: реализации последовательных участков микропрограмм и реализации параллельных участков микропрограмм. 1 О 15 Режим реализации последовательных участков микропрограмм.В исходном состоянии счет.ик, триггеры и регистры устройства находятся в нулевом состоянии. В блокепамяти МП записаны микрокоманды последовательных и параллельных участков МП. Работа устройства начи 20 нается с подачей сигнала пуска на вход 35 устройства и с приходом кода операции на вход 34 устройства. Сигнал пуска через элемент ИЛИ 15 и ступает на единичный вход триггера 10 управления и устанавливает его в единичное состояние. Единичный сигнал с единичного выхода триггера 10 управления поступает на вход генератора 5 синхроимпульсов, который на 30 чинает формировать две последователь- КОсти синхроимпульсов с 1 и сгсдви нутых одна относительно другой, Код операции, поступающий на вход 34 устройства и задающий начальный адрес последовательного участка МП, поступает на вход 34 блока 2 формирования адреса микрокоманд и с приходом синхроимпульса Г на управляющем входе блока 2 формирует исполнительный адрес микрокоманды, который 40 с выхода блока 2 поступает на вход блока 1 памяти. Микрокоманда иэ блока 1 памяти записывается в регистр 6 микрокоманд с приходом на вход регистра 6 синхроимпульса , В результате записи в регистр 6 микрокоманды с поля 61 поступает на вход блока 2 адрес А, следующей микрокоманды и КЛУ - код логических условий, Сформированный исполнительный адрес очередной микрокоманды с приходом на вход блока 2 синхроимпульса с, с его выхода поступает на вход блока 1 памяти, С поля 6.2 регистра 6 сигналы микроопераций поступают на вход блока элементов И 21, на другой вход которого поступает единичный сигнал, разрешающий прохождение сигналов микроопераций через блок элементов И 21, В результате на выход 37 устройства поступают сигналы микроопераций. Единичный сигнал на вход блока элементов И 2 поступает с выхода элемента ИЛИ-ИЕ 14, так как на входах элемента ИЛИ П" 4 присутствуют нулевые сигналы (поля 6,3 и 6.4 меток М, и М г соответственно РегистРа 6 равны нулю),Сигналы микроопераций с поля 6.2 регистра 6 не проходят через блок 3 коммутации на один из выходов 38,1- 38.Хустройства, так как на управляющий вход (фиг. 3) дешифратора 58 с выхода одновибратора 61 поступает нулевой сигнал, запрещающий работу дешифратора 58 адреса, В результате на выходе дешифратора 58 отсутствуют управляющие сигналы, управляющие прохождением сигналов с поля 6,2 регистра 6, через группу коммутаторов 59.1-59.Мблока 3 коммутации, на входы 38.1-38.Иустройства,Вторая микрокоманда считывается из блока 1 памяти и записывается в регистр 6 по синхроимпульсу Г . Вгдальнейшем работа устройства аналогична предыдущим тактам работы устройства. Формат микрокоманд в данном режиме представлен форматом А (фиг. 4). При записи в регистр 6 микрокоманды формата Е (фиг. 4), которая предшествует микрокоманде ветвления, с поля 6.6 регистра 6 на второй вход элемента И 22 поступает единичный сигнал (метка М ). По такто 4вому импульсу , с выхода 50.1 генератора 5, который поступает на первый вход элемента И 22, на выходе последнего формируется единичный управляющий сигнал, поступающий на счетный вход счетчика 13 и вход синхронизации регистра 7. С выхода 51 блока 2 формирования адреса на информационный вход регистра 7 поступает значение логического условия (иОн11 1или 1 ) , которое записывается в реги с тр 7 по си нхрои мпул ьсу с, , сформир о в ан ному на выходе элемента И 2 2 . Кроме этого , содержимое счетчика 1 3 увеличивается на " 1 " . Таким образом9 в регистр записываются значения логических условий ( 0или "1) при фор 4 ировании исполнительных адресов микрокоманд ветвления, а в счетчик 13 - код количества микрокоманд ветвления, 1 52715гп,пц гтьуьцпх паралпе 1 ьным участками к ро ирграмм.Расгмотрим Функционирование устройства при передаче управления ца другой модуль распределенной параллельной вычислительной систем . 11 осле реализации всех микропрограмм,хранящихся н блоке 1 памяти МП нрегистр 6 записывается микрокомацдаф рмата В н которой метка М 1 (поле О6.3 регистра 6) ранна единице(Фиг. 4). С поля 6,3 регистра 6 единичный сигнал, пройдя через элементИЛИ-НЕ 14 запрещает прохождениеинформации через блок элементов И 21 5Кроме того, единичный сигнал (меткаМ,), поступая на вход блока 2 запрещает прохождение кода начального адреса микропрограммы Ас поля 6,1регистра 6 для формирования очередного адреса микрокоманды данногоустройства. Код Апоступает на входблока 3 коммутации и, в зависимостиот кода номера модуля Я, поступающего с поля 6.2 регистра 6 на вход 25дешифратора 58 (фиг. 3), проходитца один из выходов 38.1-38.3-1,Единичный сигнал с поля 6.3 (мет.ка М, передачи управления) регистра 6, пройдя через элемент И 19 (наиннерснъй вход элемента И 19 поступает нулевой сигнал с поля 6.4 регистра 6), поступает на вход однонибратора 61. С выхода последнегоца управяюццй вход дешифратора 5835поступает единичный сигнал, н результате чего при поступлении кодаХ модуля с выхода 6.2 регистра 6Мц,на вход дешфратора 58 на его выходеФормируется управляющий сигнал который поступает на вход одного изкоммутаторов 59.1 - 59.Мразрешаяпрохождение кода 11, модуля с поля6,2 регистра 6 через коммутатор 59.1ца выход 38 устройства, где451, 1-1 . С выходов 38.1-38,Иустройствапередается ачальньп адрес последова.тельного участка микропрограммь, который будет ньполняться очередныммодулем распределенной вычислительной систем.Единичный сигнал (метка М, ),прошедший через элемент ИЛИ 16 ц 55сформированный одцовибратором 28,оступаец на пулевой вход триггера0 управцея, ко горый угтацавлива тс я н нуг вое состояние и тем са - мм выключает геерагор 5 синхроимпульсов. Ланцое устройство выключа; тгл, и управление передается на другое. микропрограммное устройстно управления.Рассмотрим работу устройства при приеме упранпения. Код адреса Ас, поступает на один из входов 36,в 36.Яначальных адресов микропрограмм устройства в зависимости от того, от какого устройства системы проигходит передача управления, Код адреса А , пройдя через блок элементов ИЛИ 26, поступает на вход элемента ИЛИ 1 1, который формирует сигнал пуска данного устройства. Сигнал пуска, пройдя через элемент ИЛИ 15, поступает на единичный вход триггера 10 управления и переводит его н единичное состояние. Единичный сигнал с единичного выхода триггера 10 поступает на вход генератора 5 и включает его. Генератор 5 начинает формировать две последоватепьности синхроимпульсони, которые поступают ца нходы блока 2 и регистра 6 соответстненно. С приходом на вход блока 2 синхроимпульса ь, код адреса АнОМ поступает на Выход блоков, Считанная из блока 1 памяти МП по данному адресу микрокоманда записывается в регистр 6 по синхроимпуль.лсу , . В дальнейшем работа устройства ничем не отличается от работы устройства на рассмотренных этапах функционирования. Выключение устройства происходит сигналом микрооперации конца работы, поступающим с выхода блока элементов И 21, Сигнал конца работы, прошедший через элемент ИЛИ 16 и сформированный одновибратором 28, переводит триггер 10 управления н нулевое состояние. В результате генератор 5 сццхроимпульсон выключается.Таким образом, в данном режиме функционирования устройства можно выделить следующие этапы работ:выполнение последовательных участков микропрограмм (формат микрокоманд А, метки М, - М 4 равны нулю, формат микрокоманд Е, метка М 4 равна единице);передача управления другому модулю распределенной вычислительной гистемь (формат микрокомацд В, метка М равна единице);О 5 О Таким образом, ведущий модуль системы выдает начальные адреса параллельных участков н сигналы начала параллельных участков микро 55 прием управления и выполнение последовательного участка МП.Режим реализации параллельныхучастков микропрограммы.Рассмотрим работу в данном режимеесли устройство является ведущим. Врегистр 6 (фиг. 1) записывается микрокоманда формата С (фиг. 4). Единичный сигнал (метка М ) с поля6,4 регистра 6, пройдя через элементИЛИ-НЕ 14 и поступая на блок элементов И 21, запрещает прохождение информации с поля 6.2 регистров 6 навыход 37 устройства, Коды адресов1 й-пер пер с поля 6,2 регистра 6поступают на соответствующие входыблока 3 коммутации.Единичный сигнал с поля 6,4 регистра 6 поступает на единичный входтриггера 11 и переводит его в единичное состояние. Кроме того, этот жесигнал, пройдя через элемент И 20и поступая на вход одновибратора 29,формируется и проходит на входы синхронизации регистра 8, а также науправляющий вход 43 блока 3 коммутации (фиг. 3). С входа 43 управляющий сигнал поступает на входы коммутаторов 59.1-59.М. С входа6.2 на входы коммутаторов 591- 3059.Млостулают соответственноначальные адреса микропрограмм1 Н-А ц - А , которые будут выполняться параллельно несколькимимодулями системы. С входа 47 на входы35коммутаторов 59.1-59.Мпоступаютединичные сигналы только на коммутаторы, через которые выдаются начвльные адреса параллельных участковмикропрограммы, поступающие на состветствующие выходы 38.1-38.Мустройства. Одновременно с выдачей надругой модуль системы начальногоадреса А ц ц на выход 38.1 устройства с выхода коммутатора 59.1 по"ступает сигнал начала параллельногоучастка микропрограмьв 4. Данный сигнал формируется с выхода элементаИЛИ 60.1, который поступает на входкоммутатора 59.1 и переходит через50него при поступлении единичных сигналов с входа 43 и соответствующего разряда входа 47 блока 3 коммутации,программ ведомым модулям при записив регистр 6 микрокоманды формата С.При этом на входы шифратора 4 признаков параллельных микропрограмм поступает адрес исполняемой микрокоманды с выхода 44 блока 2, код значений логичес". условий с выхода 45регистра 7 и код количества логических условий микрокоманд ветвленияс выхода 46 счетчика 13, выполняеиахпо ходу алгоритма. С выхода 47 блока на вход блока 3 коммутации по.ступает информация о тех модуляксистемы, микропрограммные устройствауправления которых будут реализовывать параллельные участки микропрограмм. Одновременно с выдачей начальных адресов параллельных участковна выходы 38.1-38.М- устройства ссоответствующих выходов 48,1-48.М блока 3 коммутации на информационныевходы триггеров регистра 8 ведущегомодуля поступают единичные сигналыкоторые запишутся в регистр 8 с приходом на его входы синхронизациитриггеров единичного сигнала с выхода 43 одновибратора 29В последующем выполнение параллель ного участка ведущим модулем системы ничем не отличается от работы устройства в режиме выполнения последовательного участка МП. В момент окончания параллельного участка ведущим модулем в регистр 6 записывается микрокоманда формата Р (фиг. 4). Единичный сигнал с поля 6.5 регистра 6, пройдя через элемент ИЛИ 16 и одно- вибратор 28, поступает на нулевой вход триггера 1 О и переводит его в нулевое состояние. Нулевой сигнал с единичного выхода триггера 10 выключает генератор 5 синхроимпульсов.Единичный сигнал (метка М 5) с поля 6.5 регистра 6, поступая на нулевой вход триггера 12, подтверздвет его исходное (нулевое) состояние, в также поступает на вход элемента И 25. По мере окончания параллельных участков МП ведомыми модулями рвс" пределенной вычислительной системы нв входы 36.1-36.Мустройства ведущего модуля поступают сигналы окончания параллельных участков ИП, которые с входов 39.-39,Мпоступают нв нулевые входы первого - (М)-го триггеров регистра 8 соответственноТриггеры регистра 8 переводятся в нулевое состояние. В ре 314125277540 По окончании параллельного участка МП в регистре 6 будет записана микрокоманда формата Р. В данном 55 случае поле 6.1 регистра 6 А,4 микрокоманды формата Р будет Обнулсн.Гдиничный сигнал (метка Мз), пройзульгате с выходов регистра 8 на входы элемента И 25 поступают единичные сигналы. После окончания всех параллельных участков МП на выходе элемента И 25 формируется единичный сигнал, который, пройдя через элемент И 24, одновибратор 31, устанавливает счетчик 13 и регистр 7 в исходное (нулевое) состояние,Единичный сигнал с выхода тригге- О ра 10 включает генератор 5 синхроимпульсов. С выхода поля 6.1 регистра 6 адрес очередной микрокоманды А, поступает на вход блока 2 (микрокоманда формата Р). С приходом на вход 15 блока 2 синхроимпульса Г, исполнительный адрес очередной микрокомаиды с выхода блока 2 поступает на вход блока 1 памяти. Таким образом, устройство переходит в режим реализа ции последовательного участка.Рассмотрим работу устройства в режиме ведомого. В исходном состоянии все триггеры, счетчик и регистры находятся в нулевом состоянии. Адрес 25 параллельного участка А ч поступает на вход 36.1 начального адреса устройства. Этот код, пройдя через блок элементов ИЛИ 26, поступает на вход элемента ИЛИ 17, Единичный сиг- о нал с выхода элемента ИЛИ 17, пройдя через элемент ИЛИ 15, устанавливает триггер 10 управления в единичное состояние. Генератор 5 синхроимпульсов начинает формировать последовательности тактовых импульсов ., и 1. С приходом на вход блока 2 синхроимпульса на его выходе будет сформирован исполнительный (начальный) адрес параллельного участка МП, В последующем работа устройства не отличается от режима реализации последовательного участка МП. Одновременноприходом АнаЧ на вход 36.1 начального адреса уст ройства на вход 40,1 поступает сигнал начала параллельного участка МП, который, пройдя через элемент ИЛИ 18, переводит триггер 12 в единичное состояние. Этот же сигнал поступает на единичный вход одного из триггеров регистра 9 начала МП. ця через элемент ИЛИ 16 и одновибратор 28, поступает на нулевой вход триггера 10 и выключает генератор 5 синхроимпульсов. Кроме того, этот же сигнал, поступая на нулевой вход триггера 12, переводит его в нулевое состояние. Единичный сигнал с нулевого выхода триггера 12, пройдя через элемент И 23 и одновибратор 30, поступает на входы блока элементов И 27Сигнал конца параллельного участка МП формируется на выходе того элемента И блока элементов И 27, вход которого подключен к триггеру регистра 9, находящемуся в единичном состоянии. Сигнал конца параллельного участка МП с выхода блока элементов И 27 поступает на выход 38.1 устройства, сигнализируя ведующему модулю системы об окончаниипараллельного участка 1-м ведомым модулем,Кроме того, единичный сигнал свыхода одновибратора 30, пройдя элемент 32 задержки и поступая на нулевые входы триггеров регистра 9,обнупяет триггер, находящийся в единичном состоянии. После этого устройство готово к приему управления дляреализации других последовательныхили параллельных участков,На этом работа устройства в режимеведомого заканчивается.После окончания программы работысистемы (после реализации всех последовательных и параллельных участков микропрограмм) выключение устройства происходит микрооперацией ИКонец работы", поступающей с выходаблока элементов И 21, Сигнал концаработы, прошедший через элементИЛИ 16 и сформированный одновибратором 28, переводит триггер 1 О управления в нулевое состояние. Генератор5 прекращает формирование тактовыхимпульсов 1 ии на этОм функционирование предлагаемого устройствазавершается,Формула изобретения1. Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы, содержащее блок памяти микропрограмм, блок формирования адреса микро- команд, блок коммутации,егистр микрокоманд, регистры начала и конца микропрограммы, триггеры управления,1252775в 1 триггера управления, прямойвыход которого соединен с входомзапуска генератора тактовых импульсов, первый и второй выходы которого5 соединены соответственно с входомсинхронизации блока формирования адреса и входом синхронизации регистрамикрокоманд, с первого по (М-)-йвходы начальных адресов мик 1,опрограммО устройства соединены соответственно ми с первого по (М)-й входами блокаэлементов ИЛИ (где К - число модулей в распределенной системе), о- выход которого соединен с четвертым15 информационным входом блока формирования адреса и с входом третьегоэлемента ИЛИ, выход которого соединен с вторым входом второго элемента ИЛИ, выход элемента задера 20 ки соединен с входами установки вО регистра начала микропрограмм ,выход которого соединен с первымвходом второго блока элементов Иа выход первого элемента И соединен25 с первым управляющим входом блокакоммутации, выход второго элементаИ соединен с входом второго одновибратора, выход которого соединенс вторым управляющим входом блока30 коммутации и с входом синхронизациирегистра конца микропрограмм, спервого по (К)-й входы признаковначала параллельных участков микропрограмм устройства соединены соответственно с первого по (М)-йвходами установки в регистра начала микропрограмм и с первого по(Ч)-й входами четвертого элемента ИЛИ, выход которого соединен с40 входом установки в 1 триггера начала микропрограммы, инверсный выход которого соединен с первым входом пятого элемента И, второй входкоторого соединен с инверсным выходом триггера конца микропрограммвыход пятого элемента И соединен свходом третьего одновибратора, выходкоторого соединен с входом элементазадержки и с вторым входом второго50 блока элементов И, с первого по(М)-й входы признаков конца параллельных участков микропрограмм устройства соединены с входами устанрвки в "О" с первого по (М)-Я конца и начала микропрограммы гене ратор тактовых импульсов, с первого по четвертый элементы ИЛИ, блок элементов ИЛИ, элемент ИЛИ-НЕ, с первого по пятый элементы И, первый и второй блоки элементов И элемент задержки с первого по четвертый одновибраторы, причем входы логических условий и кода команды устройства соединены соответственно с пер вым и вторым информационными входа блока формирования адреса, выход ко торого соединен с адресным входом блока памяти микропрограмм, выход к торого соединен с информационным входом регистра микрокоманд, выходы поля адреса которого соединены с первым информационным входом блока коммутации и третьим информационным входом блока формирования адреса, выход поля микроопераций регистра микрокоманд соединен с вторым информационным входом блока коммутации и с информационным входом первого блок элементов И, выход поля признака передачи управления регистра микрокоманд соединен с управляющим входом блока формирования адреса, первым входом элемента ИЛИ-НЕ, первым входом первого элемента И, инверсным входом второго элемента И и первым входом первого элемента ИЛИ, выход которого соединен с входом первого одновибратора, выход которого соединен с входом установки в "О" триг;ера управления, выход поля признака начала параллельных участков микропрограмм регистра микрокоманд соединен с вторым входом элемента ИЛИ-НЕинверсным входом первого элемента И, прямым входом второго элемента И и входом установки в 1" триггера конца микропрограмм, выход поля признака конца параллельных участков микропрограмм регистра микрокоманд соединен с вторым входом первого элемента ИЛИ, с входом установки вО триггера начала мик р о про г р аммыпервым входом третьего элемента И, выход которогО соединен с первым входом четвертого э л еме н т а И , выход элемента ИЛИ-НЕ соединен с вторым входом первого блока элементов И , выход которого соединен с выходом ми к ро о пе раций устройства, вход пус - 55 к а устройства соединен с первым входом второго элемента ИЛИ , выход к ото ро г о соединен с входом установки регистров конца микропрограммы соответственно, прямой выход триггераконца микропрограммы соединен с вторым входом четвертого элемента И,

СмотретьЗаявка

3854098, 08.02.1985

ПРЕДПРИЯТИЕ ПЯ Г-4651

УЛИТЕНКО ВАЛЕНТИН ПАВЛОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, НИКОЛЬСКИЙ СЕРГЕЙ БОРИСОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, СПЕРАНСКИЙ БОРИС ОЛЕГОВИЧ, КОЛЕСНИКОВ ВАСИЛИЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: вычислительной, микропрограммное, модуля, параллельной, распределенной, системы

Опубликовано: 23.08.1986

Код ссылки

<a href="https://patents.su/13-1252775-mikroprogrammnoe-ustrojjstvo-upravleniya-modulya-raspredelennojj-parallelnojj-vychislitelnojj-sistemy.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы</a>

Предыдущий патент: Устройство для умножения

Следующий патент: Устройство прерывания

Случайный патент: Газовый оптический квантовый генератор