Специализированный процессор обработки данных

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1062715

Авторы: Антонов, Кондратюк, Черкасский

Текст

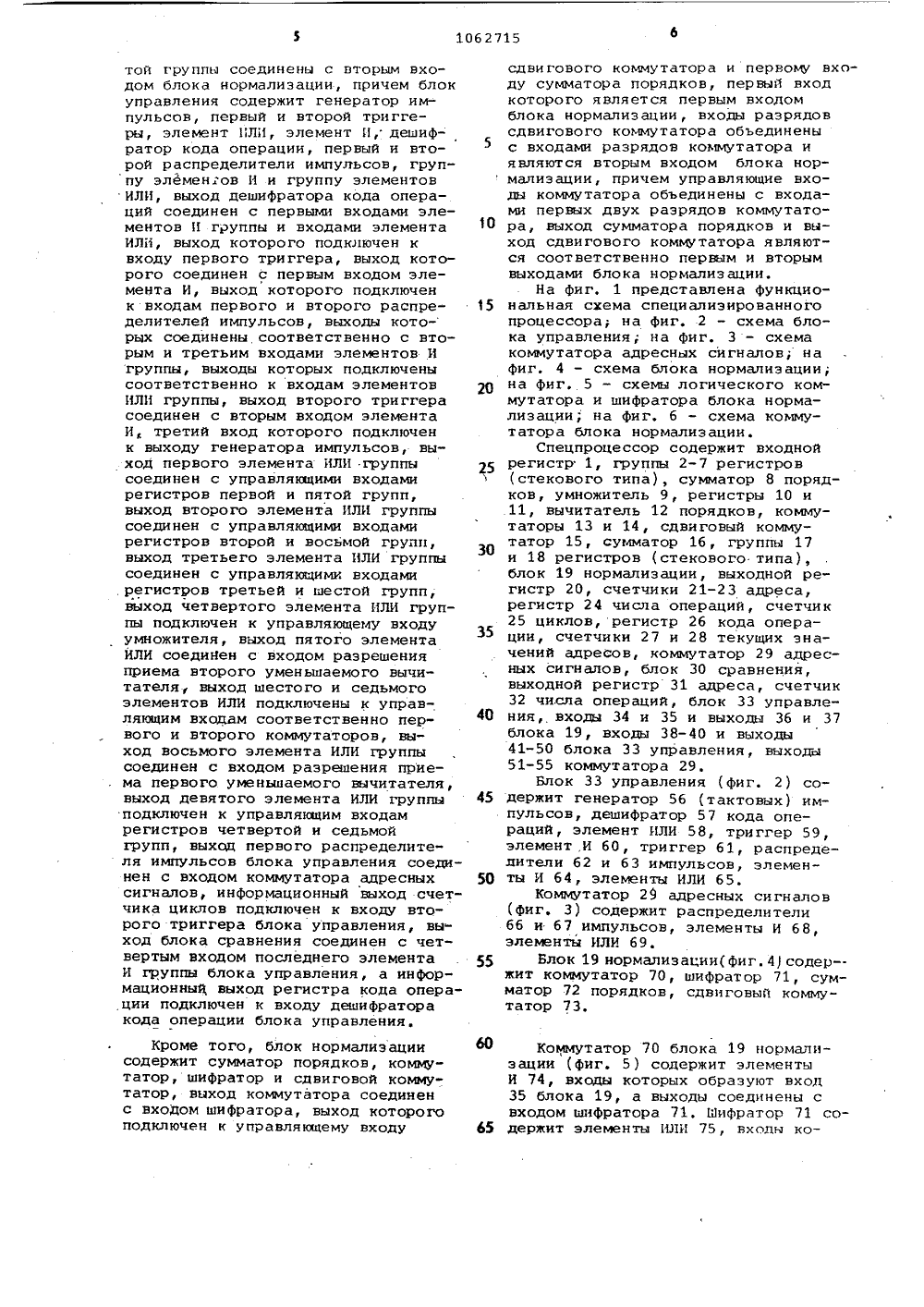

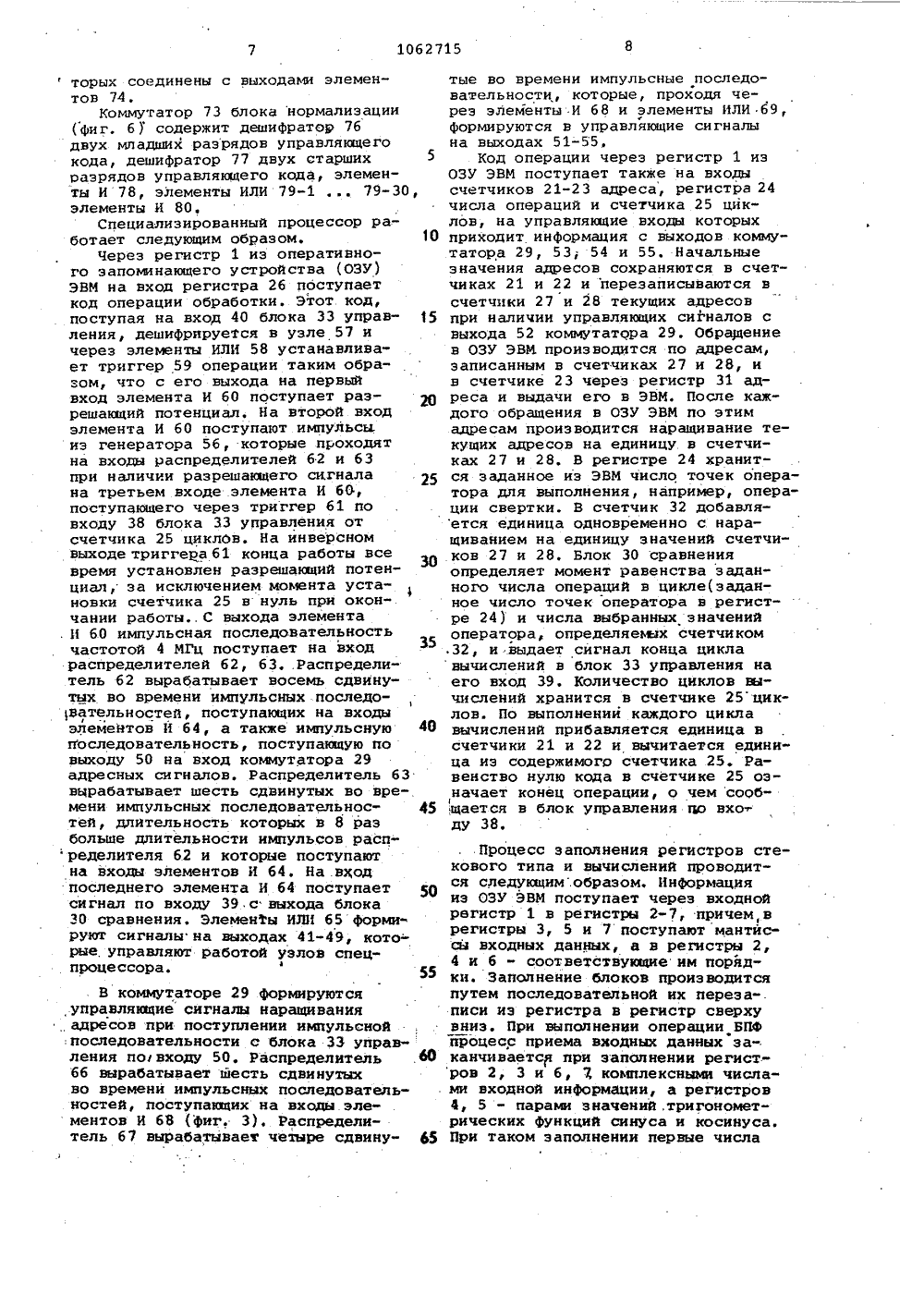

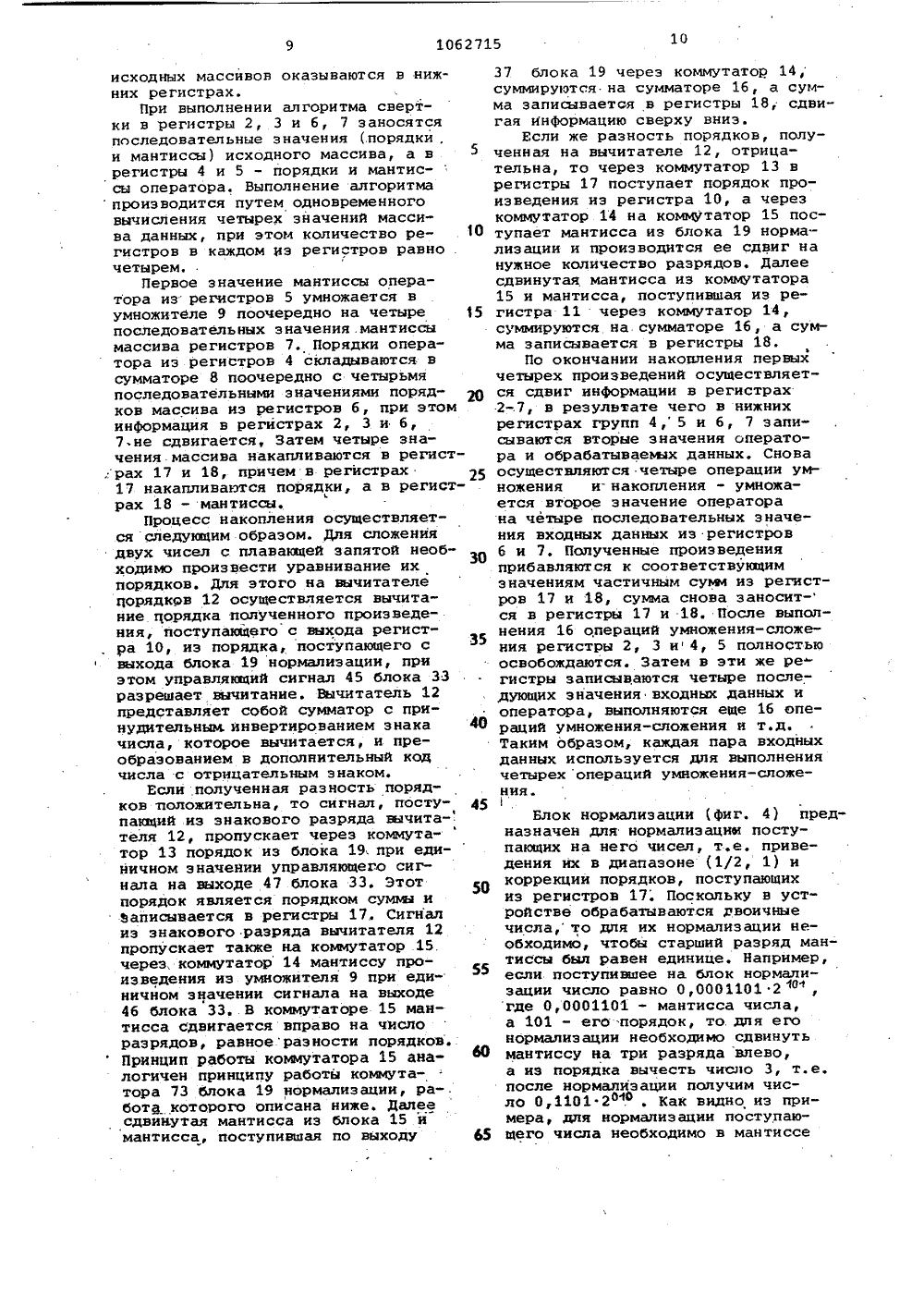

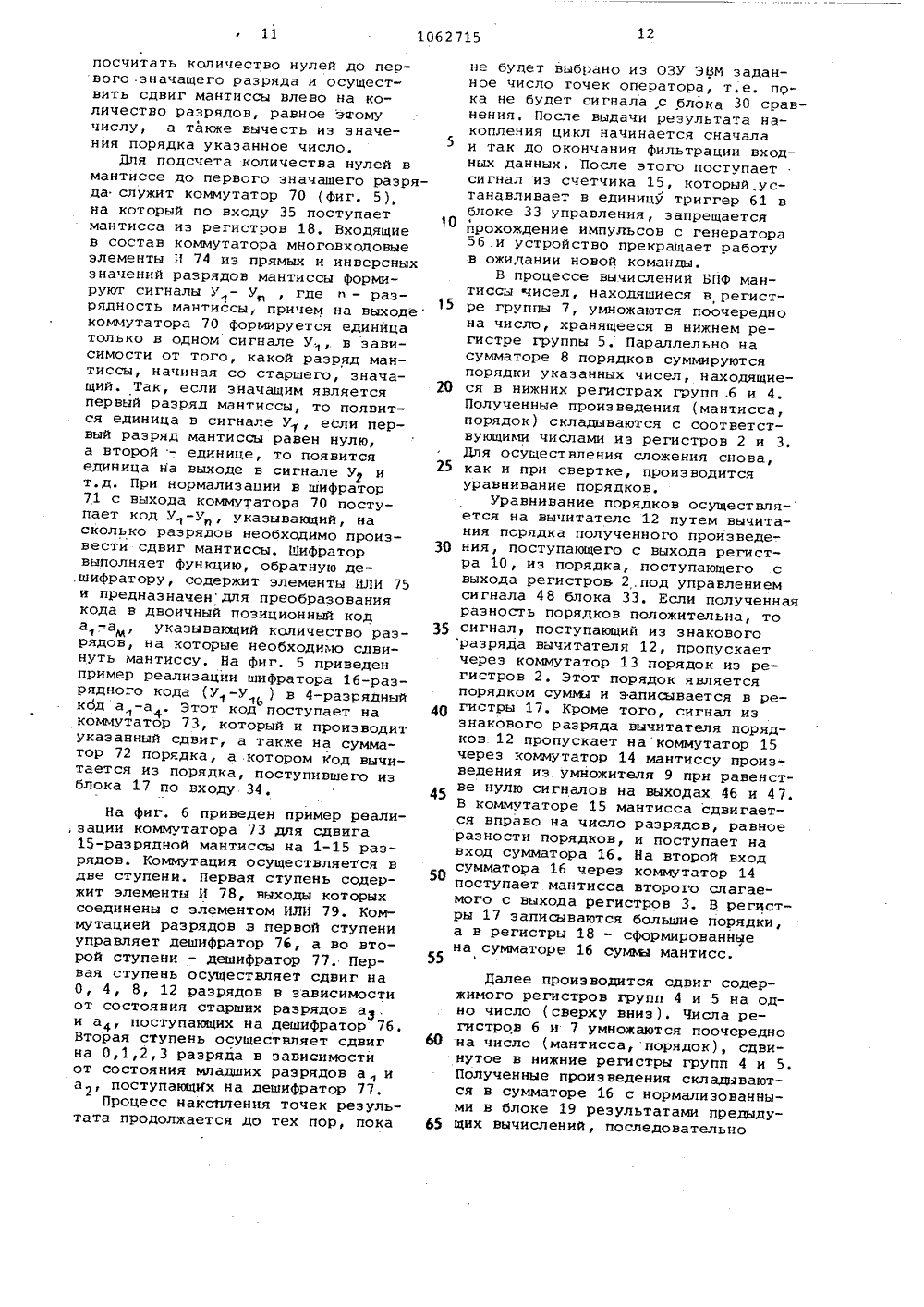

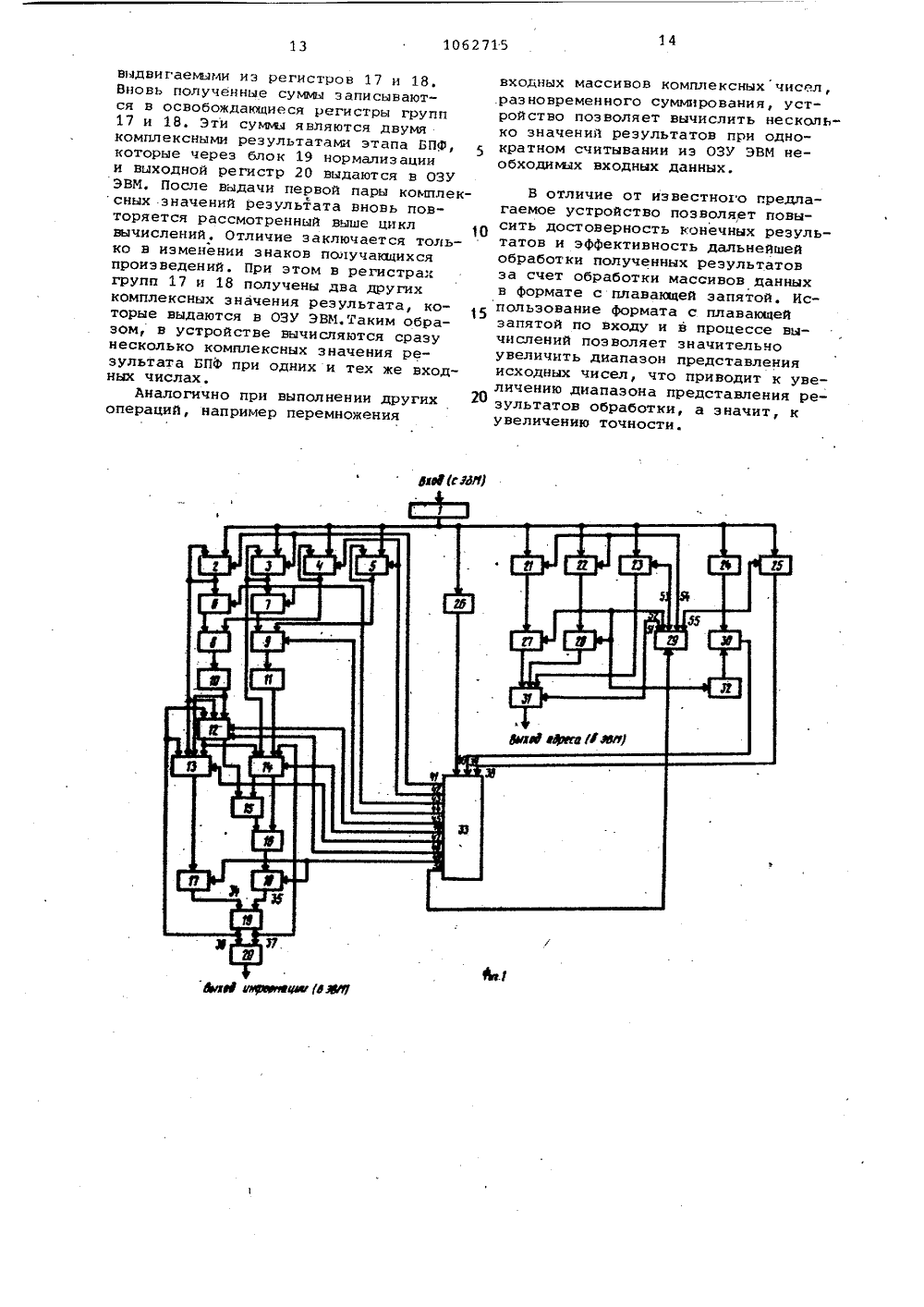

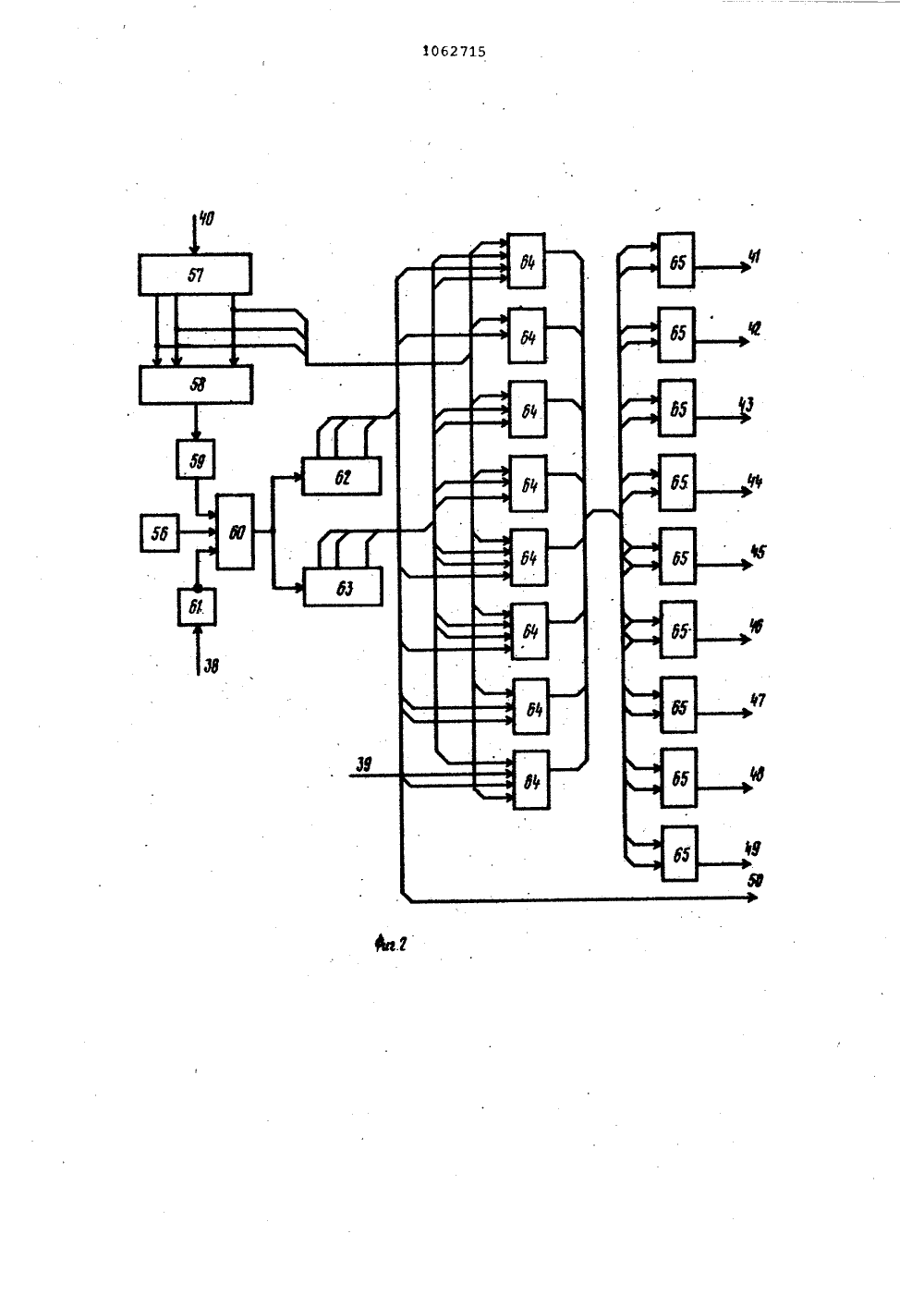

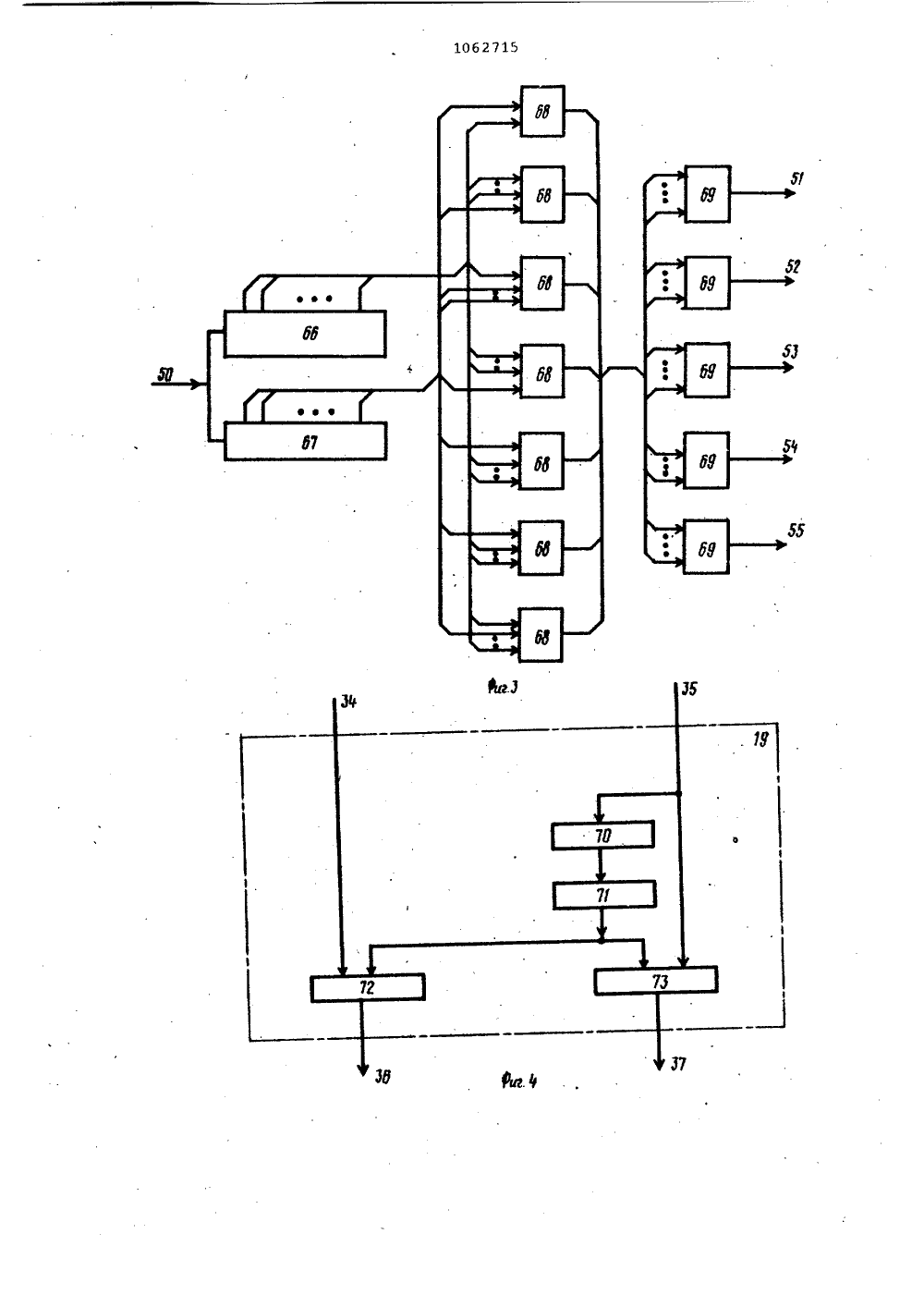

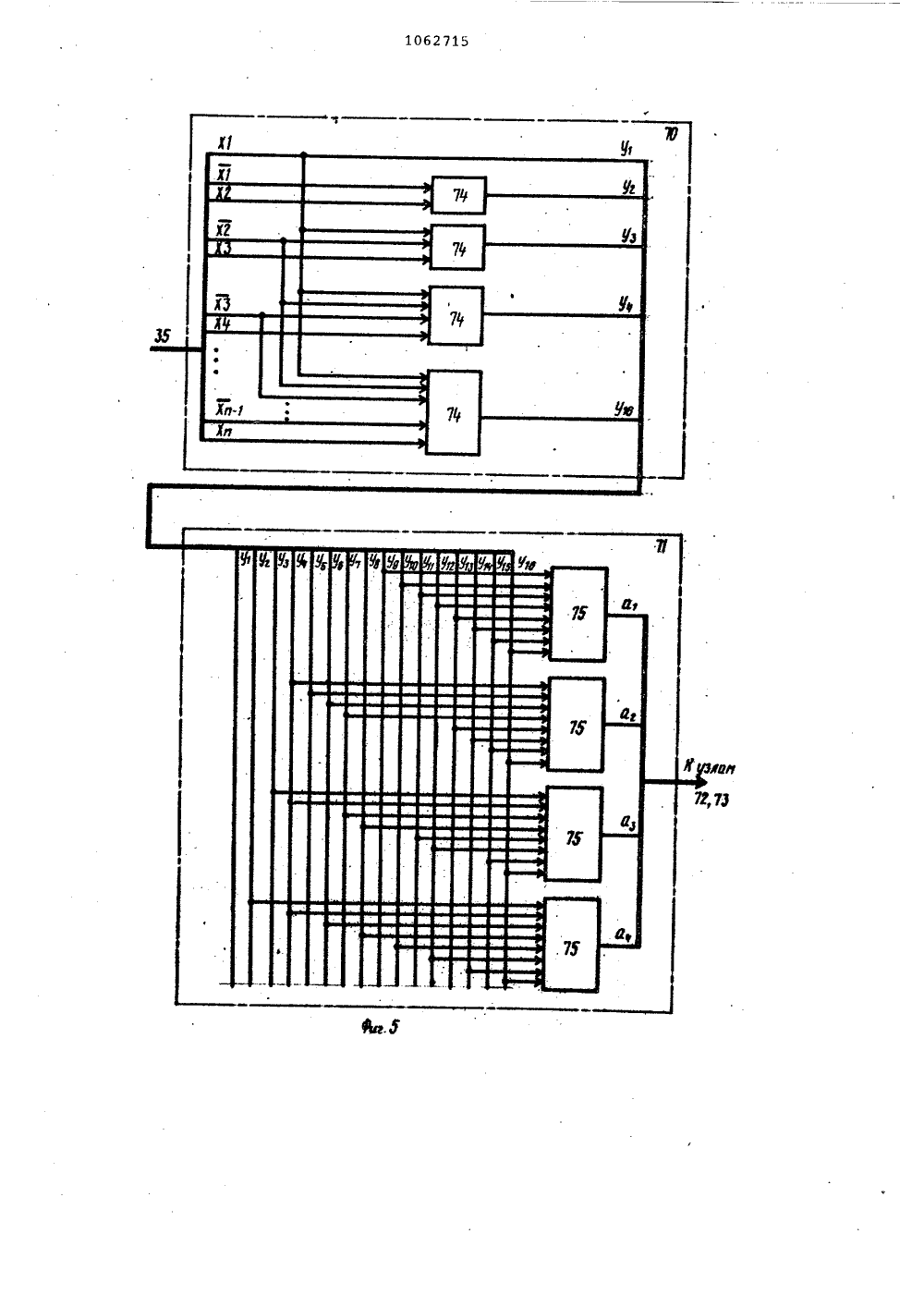

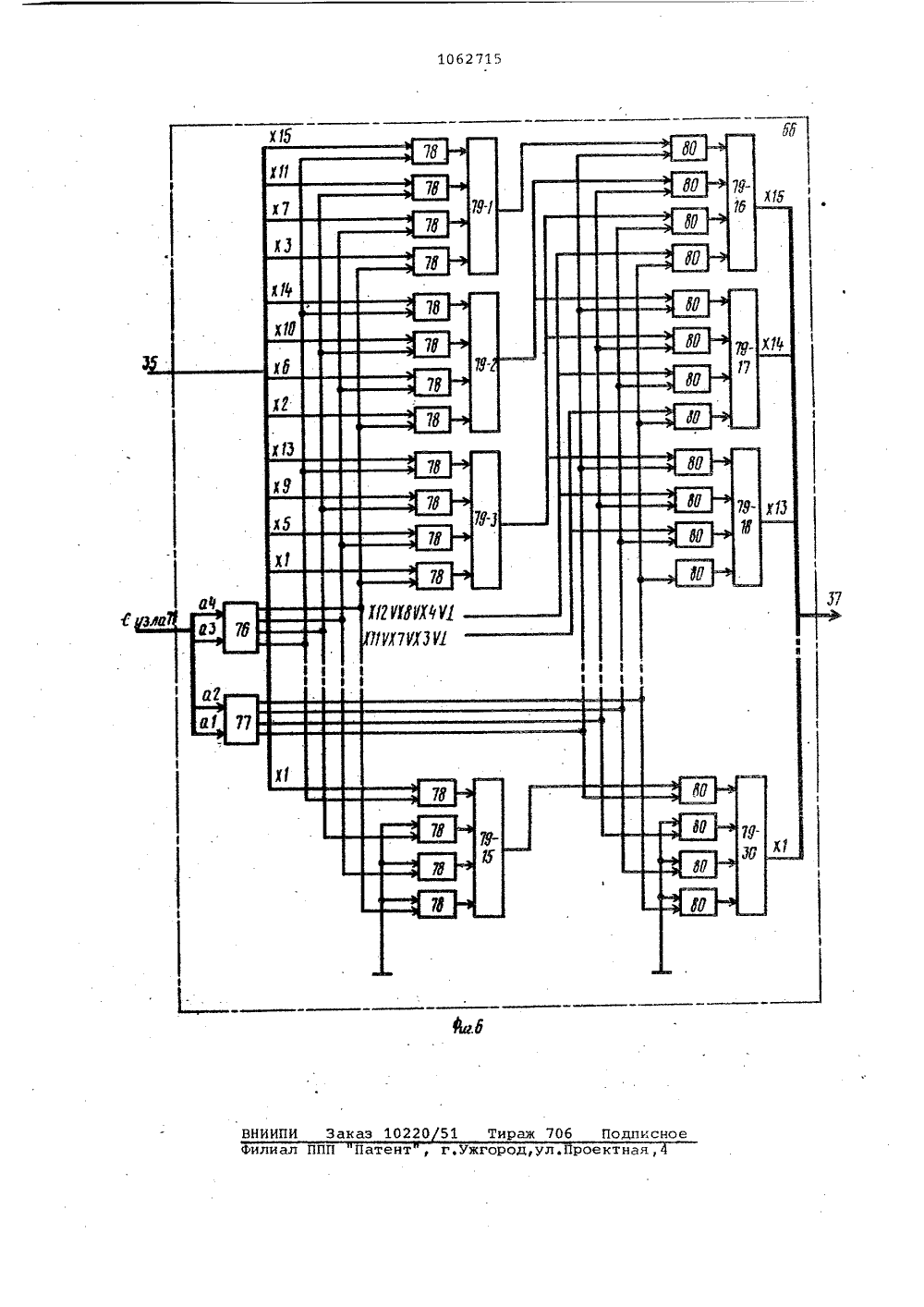

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 6 Р 15/332 ПИСАНИЕ ИЗОБРЕТЕНИ ТОРСИОМЪ( ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(71) Львовский ордена Ленина политехнический институт им. Ленинского комсомола(56) 1. Авторское свидетельство СССРР 598085, кл, 0 06 Р 15/332, 1976.2. Авторское свидетельство СССРУ 558237, кл. 0 01 у 1/28, 1974(54)(57) 1. СПЕЦИАЛИЗИРОВАННЫЙПРОЦЕССОР ОБРАБОТКИ ДАННЫХ, содержащий четыре группы регистров, входной регистр, выходной регистр, умножитель, сумматор, регистр, трисчетчика адреса, первый регистркода операций, регистр числа операций,. счетчик циклов, два счетчикатекущих значений адреса, коммутатор адресных сигналов, блок сравнения, регистр адреса, счетчикчисла операций, блок управления,информационный выход входного регистра соединен с информационными входами, регистров первой и второй групп, информационные выходыкоторых подключены к информационнымвходам регистров соответственнопервой и второй групп, информационные выходы регистров первой группыподключены к информационным выходам регистров третьей группы, информационные выходы которых соединены с первым входом умножителя,выход которого подключен к информационному входу регистра, информационные выходы регистров второйгруппы соединены с вторым входомумножителя, информационный выходвходного регистра подключен к .информационному входу регистра кода опе 801 О 2715 А рации, информационным входам трех счетчиков адреса, информационному входу счетчика циклов и информационному входу регистра числа операций, информационный выход которого подключен к первому входу блока сравнения второй вход которого соединен с информационным выходом счетчика числа операций, информационные выходы первого и второго счетчиков адреса соединены с информационными входами соответственно первого и второго счетчиков текущих значений адреса, информационные выходы которых подключены к информационному входу регистра адреса, информационный выход которого Ж является выходом адреса процессора, ,р первый выход коммутатора адресныхЦ) сигналов соединен с управляющими входами двух счетчиков текущих значений адреса и счетчика числа операций, второй выход коммутатора адресных сигналов подключен к управляющему входу регистра адреса, информационный вход которого соединен . с информационным выходом третьего счетчика адреса, управляющий вход которого подключен к третьему выходу коммутатора адресных сигналов, четвертый выход которого соединен с управляющими входами первого и второго счетчиков адреса, пятый выход коммутатора адресных сигналов подключен к управляющему входу счетчика циклов, информационный вход входного регистра и информационный выход выходного регистра являются соответственно информационным входом и информационным выходом процессора, о т л и ч а ю щ и й с я тем, что, с целью повышения точности, в него введены пятая, шестая, седьмая и восьмая группы регистров, сумф матор порядков, .второй регистр, вычитатель порядков, первый и вто 3062715ИИПИ Заказ 10220илиал ППП Патент краж 706 Подписножгород,ул. роектная, 1062715рой коммутаторы, сдвиговый коммутатор и блок нормализации, первыйвыход .которого соединен с входамиразрядов порядка выходного регистра,первым входом первого коммутатораи входом вычитаемого вычитателя порядков выход знакового разрядакоторого подключен к второму входупервого коммутатора и первому входу второго коммутатора, первый выход которого соединен с входом сдвигового коммутатора, выход которого соединен с первым входом сумматора, второй вход которого подключен к выходу второго коммутатора,второй вход которого соединен с инФормационным выходом первого регистра, информационный, выход входногорегистра подключен к информационным входам регистров пятой группы,информационные выходы которых соединены с информационными входамирегистров пятой группы, входом первого уменьшаемого вычитателя порядков, третьим входом первого коммутатора и информационными входамирегистров шестой группы, информационные выходы которых подключенык первому входу сумматора порядков,выход которого соединен с информационным входом второго регистра,информационный выход которого подключен к входу второго уменьшаемого вычитателя порядков и четвертомувходу первого коммутатора, выходкоторого соединен с информационныьи входами регистров седьмой группы, информационные выходы которыхподключены к первому входу блоканормализации, второй выход которого .соединен с разрядами мантиссывыходного регистра и третьим входом четвертого коммутатора, четвертый вхоц которого подключен к информационным выходам регистров первой группы, информационный выходвходного регистра соединен с инФормационными входами регистроввосьмой группы, информационные выходы которых соединены с вторым входом сумматора порядков, выход разрядов числа вычитателя порядков соединен с управляющим входом сдвигового коммутатора, информационныевыходы регистров четвертой группысоединены с вторым входом блока нормализации, причем блок управлениясодержит генератор импульсов, первый и второй триггеры, элемент ИЛИ,элемент И, дешифратор кода операции, первый и второй распределители импупьсов, группу элементов И игруппу элементов ИЛИ, выход дешифратора кода операций соединен с первыми входами элементов И группыи входами элемента ИЛИ, выход которого подключен к входу первого триггера, выход которого соединен с первым входом элемента И, выход которого подключен к входам первого и второго распределителей импульсов, выходы которых соединены соответственно с вторым и третьимвходами элементов И группы, выходыкоторых подключены соответственнок входам элементов ИЛИ группы, выход второго триггера соединен свторым входом элемента И, третийвход которого подключен к выходугенератора импульсов, выход первого элемента ИЛИ группы соединен суправляющими входами регистровпервой и пятой групп, выход второго элемента ИЛИ группы соединен суправляющими входами регистроввторой и восьмой групп, выход третьего элемента ИЛИ группы соединенс управляющими входами регистровтретьей и шестой трупп, выход четвертого элемента ИЛИ группы подключен к управляющему входу умножителя, выход пятого элемента ИЛИ соединен с входом разрешения приемавторого уменьшаемого вычитателя,выход шестого и седьмого элементовИЛИ подключены к управляющим входам соответственно первого и второго коммутаторов, выход восьмогоэлемента ИЛИ группы соединен с входом разрешения приема первогоуменьшаемого вычитателя, выход девятого элемента ИЛИ группы подключен к управляющим входам регистровчетвертой и седьмой групп, выходпервого распределителя импульсовблока управления соединен с входомкоммутатора адресных сигналов, информационный выход счетчика циклов подключен к входу второго триггера блока управления, выход блока сравнения соединен с четвертымвходом последнего элемента И группы блока управления, информационныйвыход регистра кода операции подключен к входу дешифратора кодаоперации блока управления,2, Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок нормализации содержит сумматор порядков, коммутатор, шифратор и сдвиговый коммутатор, выход коммутато-ра соединен с входом шифратора,выход которого подключен к управляющему входу сдвигового коммутатора и первому входу сумматора порядков, первый вход которого являетсяпервым входом блока нормализации,входы разрядов сдвигового коммутатора объединены с входами разрядов коммутатора и являются вторым входом блока нормализации, причем управляющие входы коммутатора объединены с входами первых двух разрядов комчутатора, выход сумматора1062715 порядков.и выход сдвигового коммутатора являются соответственно 1Изобретение относится к вычислительной технике и предназначено для обработки массивов данных при решении задач спектрального анализа. 5Известно устройство для выполнения быстрого преобразования Фурье, содержащее четыре входных регистра, регистры комплексной весовой функции, коммутатОр сомножителей, блок 10 управления, блок умножения, регистры произведений, коммутатор слагаемых, сумматор, регистры суммя Г 1.Данное устройство не позволяет ,:обрабатывать массивы данных с высокой точностью, т.е. в формате с плавающей запятой.Наиболее близким к предлагаемому является устройство, содержащее входной регистр, вход которого является входом устройства, а выход подключен к первым входам первого и второго блоков регистров стекового типа, йервого, второго и третьего счетчиков адреса, счетчика циклов, к входам регистра кода операции иРегистра числа операции, выход которого подключен к первому входу схеьы сравнения, вторые входы первого и второго счетчиков адреса, первые входы первого и второго счетчиков ЗО текущего адреса, вторые входы третьего счетчика адреса н счетчика циклов, вход счетчика числа операций соединены с выходами коммутатора адресных сигналов, выход счетчика 35 числа операций соединен со вторым входом схеж сравнения, выходы первого и второго счетчиков адреса соединены с вторыми входами первого и второго счетчиков текущего 4 О адреса, выходы которых и выход третьего счетчика адреса подключены к первому, второму и третьему входам регистра адреса, выход которого является адресным выходом устройства, а четвертый вход соединен с выходом коммутатора адресных сигналов, выход первого блока регистров стекового типа соединен со своим вторым входом и с информационным входом третьего блока регистров стекового типа, выход второго блока регистров стекового типа соединен со своим вторым входом и с первым входом перемйожителя, второй вход которого соединен с выходом третьего блопервым и вторым выходами блока нормализации,ка регистров стекового типа, выходперемножителя соединен с входом первого промежуточного регистра, выход сумматора соединен с информационным входом четвертого блока регистров стекового типа, выход выходного регистра является информационным выходом устройства, входы блока управления соединены,с выходомрегистра кода операции и с выходамисхемы сравнения и счетчика циклов,выходы блока управления соединеныс управляющими входами блоков регистров стекового типа и перемножи-теля 21. 1Недостатком этого устройства является то, что в нем массивы данных могут обрабатываться только в формате с фиксированной запятой. В этом случае оно эффективно при обработке однородных массивов, характеризующихся небольшим динамическим диапазоном. Обработка неоднородных массивов данных с большим динамическим диапазоном в формате с фиксированной запятой связана с большими погрешностями. Кроме того, при выполнении алгоритма быстрого: преобразования Фурье в формате с фиксированной запятой результат умножения исходных данных на значения синусно-косинусной матрицы получается двойной длины. Для получения результата той же разрядности, что имеют входные данные, примейяется маскирование - выделение старших разрядов результата, Старший значащий разряд при этом задается програьачистом, Возможны ситуации, при которых значащими разрядами результата будут несколько мпадших разрядов, а остальные разряды будут иметь нулевое значение. Маскирование такого результата и использование его в качестве исходных данных для последукщего этапа БПФ приводит к искажению реаль-, ного массива, который подвергается анализу. Во избежание этого в устройстве при выполнении операции БПФ после каждого этапа обработки необходимо проводить сдвиг результата влево с запоминанием количества сдвигов. Выполнение указанных процедур требует и дополнительногооборудования, и усложнения математического обеспечения.Целью изобретения является повышение точности обработки дацных. Поставленная цель достигаетсятем, что в специализированный процессор обработки данных, содержащийчетыре группы регистров, входнойрегистр, выходной регистр, умножитель, сумматор, регистр, три счетчика адреса, первый регистр кодаопераций, регистр числа операций,счетчик циклов, два счетчика текущих значений адреса, коммутатор адресных сигналов, блок сравнения,регистр адреса, счетчик числа операций, блок управления, информационныйвыход входного регистра соедийенс информационными входами регистров первой и второй групп, Йнформационные выходы которых подключены к информационным входам регистров соответственно первой и второйгрупп, информационные выходы регистров первой группы подключены к информационным выходам регистров третьей группы, информационные выходы которых соединены с первым входом умножителя, выход которого подключен к информационному входу регистра, информационные выходы регистров второй группы соединены с вторым входом умножителя, информационный выход входного регистра подключен к информационному входу регистра кода операции, информационным входам трех счетчиков адреса, информационному входу счетчика циклов, и информационному входу регистра . числа операций, информационный выход которого подключен к первомувходу блока сравнения, второй входкоторого соединен с информационным выходом счетчика числа операций, информационные выходы первого и второго счетчиков адреса соединены с информационными входами соответственно первого и второго счетчиков . текущих значений адреса, информационные выходы которых подключены к информационному входу регистра адреса, информационный выход которого является выходом адреса процессора, первый выход коммутатораадресных сигналов соединен с управляющими входами двух счетчиковтекущих значений адреса и счетчикачисла операций, второй выход коммутатора адресных стгналов подключен к управляющему входу регистраадреса, информационный вход которого подсоединен к информационному выхо. ду третьего счетчика адреса, управляющий вход которого подключен к тре тьему выходу коммутатора адресных сигналов, четвертый выход которого соедийен с управлякщими входами 5 10 15 20 25 30 35 40 45 50 55 60 65 первого и второго счетчиков адреса,пятый выход коммутатора адресныхсигналов подключен к управляющемувходу счетчика циклов, информационный вход входного регистра и информационный выход выходного регистра являются соответственно информационным входом и информационнымвыходом процессора, введены пятая,шестая, седьмая и восьмая группырегистров, сумматор. порядков, второй регистр, вычитатель порядков,первый и второй коммутаторы, сдви-говый коммутатор и блок нормализациипервый выход которого соединен с входами разрядов порядка выходного регистра, первым входомпервого коммутатора и входом вычитаемого вычитателя порядков,,выход знакового разряда которогоподключен к второму входу первогокоммутатора и первому входу второго коммутатора, первый выход которого соединен с входом сдвигового коммутатора, выход которогосоединен с первым входом сумматора, второй вход которого подключен к выходу второго коммутатора,второй вход которого соединен с ин-.формационным выходом первого регистра, информационный выход входного регистра подключен к информационным входам регистров пятойгруппы, информационные выходы которых соединены с информационнымивходами регистров пятой группы,входом первого уменьшаемого вычитателя порядков, третьим входомпервого коммутатора и информационными входами регистров шестой группы, информационные выходы которыхподключены к первому входу сумматора порядков, выход которого соединен с информационным входом второго регистра, информационный выход которого подключен к входувторого уменьшаемого вычитателяпорядков и четвертому входу первого коммутатора, выход которого соединен с информационными входами регистров седьмой группы, информационные выходы которых подключенык первому входу блока нормализации,второй выход которого соединен с,разрядами мантиссы выходного регистра и третьим входом четвертого коммутатора, четвертый вход которогоподключен к информационным выходамрегистров первой группы, информационный выход входного регистра соединен с информационными входамирегистров восьмой группы, информационные выходы которых соединеныс вторым входом сумматора порядков,выход разрядов числа вычитателя порядков соединен с управляющим входом сдвигового коялутатора, информационные выходы регистров четвер1062715 той группы соединены с вторым входом блока нормализации, причем блокуправления содержит генератор импульсов, первый и второй триггеры, элемент ИЛИ, элемент И, дешифратор кода операции, первый и второй распределители импульсов, группу элементов И и группу элементовИЛИ, выход дешифратора кода операций соединен с первыми входами элементов И группы и входами элементаИЛИ, выход которого подключен квходу первого триггера, выход которого соединен с первым входом элемента И, выход которого подключенк входам первого и второго распределителей импульсов, выходы которых соединены соответственно с вторым и третьим входами элементов Игруппы, выходы которых подключенысоответственно к входам элементов 2 ОИЛИ группы, выход второго триггерасоединен с вторым входом элементаИ третий вход которого подключенк выходу генератора импульсов, выход первого элемента ИЛИ группы 25соединен с управляющими входамирегистров первой и пятой групп,выход второго элемента ИЛИ группысоединен с управляющими входамирегистров второй и восьмой групп,выход третьего элемента ИЛИ группысоединен с управляющими входамирегистров третьей и шестой групп,выход четвертого элемента ИЛИ группы подключен к управляющему входуумножителя, выход пятого элементаИЛИ соедийен с входом разрешенияприема второго уменьшаемого вычитателя выход шестого и седьмогоэлементов ИЛИ подключены к управляющим входам соответственно пер Ового и второго коммутаторов, выход восьмого элемента ИЛИ группысоединен с входом разрешения приема первого уменьшаемого вычитателя,выход девятого элемента ИЛИ группы 45подключен к управляющим входамрегистров четвертой и седьмойгрупп, выход первого распределителя импульсов блока управления соединен с входом коммутатора адресных 50сигналов, информационный выход счетчика циклов подключен к входу второго триггера блока управления, выход блока сравнения соединен с четвертым входом последнего элемента . 55И группы блока управления, а информационны выход регистра кода операции подключен к входу дешифраторакода операции блока управлениявходом шифратора 71. Ыифратор 71 со 65 держит элементы ИЛИ 75, входы коКроме того, блок нормализации содержит сумматор порядков, коммутатор, шифратор и сдвиговой коммутатор, выход коммутатора соединен с входом шифратора, выход которого подключен к управляющему входу сдвигового коммутатора и первому входу сумматора порядков, первый вход которого является первым входом блока нормализации, входы разрядов сдвигового коммутатора объединены с входами разрядов коммутатора и являются вторым входом блока нормализации, причем управляющие входы коммутатора объединены с входами первых двух разрядов коммутатора, выход сумматора порядков и выход сдвигового коммутатора являются соответственно первым и вторым выходами блока нормализации.На фиг. 1 представлена функциональная схема специализированного процессора; на фиг. 2 - схема блока управления; на фиг, 3 - схема коммутатора адресных сигналов на фиг. 4 - схема блока нормализации; на фиг, 5 - схемы логического коммутатора и шифратора блока нормализации; на фиг. б - схема коммутатора блока нормализации.Спецпроцессор содержит входной регистр 1, группы 2-7 регистров (стекового типа), сумматор 8 порядков, умножитель 9, регистры 10 и 11, вычитатель 12 порядков, коммутаторы 13 и 14, сдвиговый коммутатор 15, сумматор 16, группы 17 и 18 регистров (стекового типа), блок 19 нормализации, выходной регистр 20, счетчики 21-23 адреса, регистр 24 числа операций, счетчик 25 циклов, регистр 26 кода операции, счетчики 27 и 28 текущих значений адресов, коммутатор 29 адресных сигналов, блок 30 сравнения,выходной регистр 31 адреса, счетчик 32 числа операций, блок 33 управления, входы 34 и 35 и выходы 36 и 37 блока 19, входы 38-40 и выходы 41-50 блока 33 управления, выходы 51-55 коммутатора 29.Блок 33 управления (фиг. 2) содержит генератор 56 (тактовых) импульсов, дешифратор 57 кода операций, элемент ИЛИ 58, триггер 59, элемент,И 60, триггер 61, распредедители 62 и 63 импульсов, элементы И 64, элементы ИЛИ 65.Коммутатор 29 адресных сигналов (фиг. 3) содержит распределители 66 и 67 импульсов, элементы И 68, элементы ИЛИ 69.Блок 19 нормализации(фиг.4 содер жит коммутатор 70, шифратор 71, сумматор 72 порядков, сдвиговый коммутатор 73. Коюмутатор 70 блока 19 нормализации (фиг. 5) содержит элементы И 74, входы которых образуют вход 35 блока 19, а выходы соединены с1 О процессора. 55В коммутаторе 29 формируются управлякщие сигналы наращивания адресов при поступлении импульсиой последовательности с блока 33 управления по входу 50. Распределитель 60 66 вырабатывает шесть сдвинутых во времени импульсных последовательностей, поступающих на входы элементов И 68 (фиг. 3). Распределитель 67 вырабатывает четыре сдвину 65торых соединены с выходами элементов 74,Коммутатор 73 блока нормализации(Фиг. 6) содержит дешифратор 76двух мпадших разрядов управляющегокода, дешифратор 77 двух старших 5разрядов управляющего кода, элементы И 78, элементы ИЛИ 79-1, 79-30,элементы И 80.Специализированный процессор работает следующим образом.Через регистр 1 из оперативного запоьынающего устройства (ОЗУ)ЭВМ на вход регистра 26 поступаеткод операции обработки. Этот код,поступая на вход 40 блока 33 управления, дешифрируется в узле 57 ичерез элементы ИЛИ 58 устанавливает триггер 59 операции таким образом, что с его выхода на первыйвход элемента И 60 поступает разрешакщий потенциал, На второй входэлемента И 60 поступают импульсы,из генератора 56, которые проходятна входы распределителей 62 и 63при наличии разрешающего сигналана третьем входе элемента И 6 О,поступающего через триггер 61 повходу 38 блока 33 управления отсчетчика 25 циклов. на инверсномвыходе триггера 61 конца работы всевремя установлен разрешающий потенциал, за исключением момента установки счетчика 25 в нуль при окончании работы С выхода элемента. И 60 импульсная последовательностьчастотой 4 МГц поступает на входраспределителей 62, 63 Распределитель 62 вырабатывает восемь сдвинутых во времени импульсных последовательностей, поступающих на входыэлементов И 64, а также импульсную 40госледовательность, поступающую повыходу 50 на вход коммутатора 29адресных сигналов. Распределитель 63вырабатывает шесть сдвинутых во времени импульсных последовательностей, длительность которых в 8 разбольше длительности импульсов расп ределителя 62 и которые поступаютна входы элементов И 64. На .входпоследнего элемента И 64 поступает 5 Осигнал по входу 39 с выхода блока30 сравнения. Элементы ИЛИ 65 формируют сигналы на выходах 41-49, кото-рые, управляют работой узлов спец 4 тые во времени импульсные последовательности, которые, проходя через элементы И 68 и элементы ИЛИ 69,Формируются в управляющие сигналына выходах 51-55,Код операции через регистр 1 изОЗУ ЭВМ поступает также на входысчетчиков 21-23 адреса, регистра 24числа операций и счетчика 25 циклов, на управлякщие входы которыхприходит информация с выходов коммутатора 29, 53; 54 и 55. Начальныезначения адресов сохраняются в счетчиках 21 и 22 и перезаписываются всчетчики 27 и 28 текущих адресовпри наличии управляющих сигналов свыхода 52 коммутатора 29, Обращениев ОЗУ ЭВМ.производится по адресам,записанным в счетчиках 27 и 28, ив счетчике 23 через регистр 31 адреса и выдачи его в ЭВМ. После каждого обращения в ОЗУ ЭВМ по этимадресам производится наращивание текущих адресов на единицу в счетчиках 27 и 28. В регистре 24 хранится заданное из ЭВМ число точек оператора для выполнения, например, операции свертки. В счетчик 32 добавляется единица одновременно с наращиванием на единицу значений счетчиков 27 и 28, Блок 30 сравненияопределяет момент равенства заданного числа операций в цикле(заданное число точек оператора в регистре 24) и числа выбранных значенийоператора, определяеьых счетчиком,32, и выдает сигнал конца циклавычислений в блок 33 управления наего вход 39. Количество циклов начислений хранится в счетчике 25 циклов. По выполнении каждого циклавычислений прибавляется единица всчетчики 21 и 22 и вычитается единица из содержимого счетчика 25. Равенство нулю кода в счетчике 25 означает конец операции, о чем сооб"щается в блок управления по входу 38.Процесс заполнения регистров стекового типа и вычислений проводится следукщим.образом, Информация иэ ОЗУ ЭВМ поступает через входной регистр 1 в регистры 2-7, причем,в регистры 3, 5 и 7 поступают мантиссы входных данных, а в регистры 2, 4 и б - соответствующие им порядки. Заполнейие блоков производится путем последовательной их переза-. писи иэ регистра в регистр сверху вниз. При выполнении операции БПФ процесс приема входных данных заканчивается при заполнении регистров 2, 3 и б, Ч комплексными числами входной информации, а регистров 4, 5 - парами значений,тригонометрических функций синуса и косинуса. При таком заполнении первые числаисходных массивов оказываются и нижних регистрах.При выполнении алгоритма свертки в регистры 2, 3 и б, 7 заносятсяпоследовательные значения (.порядки,и мантиссы) исходного массива, а врегистры 4 и 5 - порядки и мантиссы оператора. Выполнение алгоритмапроизводится путем одновременноговычисления четырех значений массива данных, при этол количество регистров в каждом иэ регистров равно .четырем,Первое значение мантиссы оператора из регистров 5 умножается вумножителе 9 поочередно на четыре 15последовательных значения.мантиссымассива регистров 7. Порядки оператора из регистров 4 складываются. всумматоре 8 поочередно с четырьмяпоследовательными значениями порядков массива иэ регистров б, при этоминформация в регистрах 2, 3 и б,7.не сдвигается, Затем четыре значения массива накапливаются в регистрах 17 и 18, причем в регистрах17 накапливаются порядки, а в регистрах 18 - мантиссы.Процесс накопления осуществляется следующим образом. Для сложениядвух чисел с плавакзцей запятой необходимо произвести уравнивание ихпорядков. Для этого на вычитателецорядков 12 осуществляется вычитание порядка полученного произведения, поступающего с выхода регистра 10, из порядка, поступающего с35выхода блока 19 нормализации, прнэтом управлякюций сигнал 45 блока 33разрешает вычитание. Вычитатель 12представляет собой сумматор с принудительным инвертированием знака 40числа, которое вычитается, и преобразованием в дополнительный кодчисла с отрицательным знаком.Если полученная разность порядков положительна, то сигнал, поступакщий из знакового разряда вычита-теля 12, пропускает через коммутатор 13 порядок из блока 19.при единичном значении управляющего сигнала на выходе 47 блока 33. Этотпорядок является порядком суюы изаписывается в регистры 17, Сигнализ знакового разряда вычитателя 12пропускает также на коммутатор 15.через, коммутатор 14 мантиссу произведения из умножителя 9 при единичном значении сигнала на выходе46 блока 33, В коммутаторе 15 мантисса сдвигается вправо на числоразрядов, равное разности порядков.Принцип работы ковиутатора 15 ана- ологичен принципу работы коммутатора 73 блока 19 нормализации, ра-,бота которого описана ниже. Далеесдвийутая мантисса из блока 15 имантисса, поступившая по выходу 65 37 блока 19 через коммутатор 14, суммируются на сумматоре 16, а сумма записываетоя в регистры 18, сдви" гая информацию сверху внизЕсли же разность порядков, полученная на вычитателе 12, отрицательна, то через коммутатор 13 в регистры 17 поступает порядок произведения иэ регистра 10, а через коммутатор 14 на коммутатор 15 поступает мантисса из блока 19 нормализации и производится ее сдвиг на нужное количество разрядов. Далее сдвинутая мантисса из коммутатора 15 и мантисса, поступившая из регистра 11 через коммутатор 14, суммируются на.сумматоре 16, а сумма записывается в регистры 18.По окончании накопления первых четырех произведений осуществляется сдвиг информации в регистрах 2-.7, в реэулвтате чего в нижних регистрах групп 4, 5 и б, 7 записываются вторые значения оператора и обрабатываевых данных. Снова осуществляются четыре операции умножения и- накопления - умножается второе значение оператора на четыре последовательных значения входных данных иэ регистров б и 7, Полученные произведения прибавляются к соответствующим значениям частичны 1 л сумм из регистров 17 и 18, сумка снова заносит- ся в регистры 17 и 18. После выполнения 16 операций умножения-сложения регистры 2, 3 и 4, 5 полностью освобождаются. Затем в эти же регистры записываются четыре последующих значения входных данных и оператора, выполняются еще 16 операций умножения-сложения и т.д. Таким образом, каждая пара входных данных используется для выполнения четырех операций умножения-сложения.Блок нормализации (фиг. 4) предназначен для нормализацик поступающих на него чисел, т.е. приведения их в диапазоне (1/2, 1) и коррекции порядков, поступающих из регистров 17; Поскольку в устройстве обрабатываются двоичные числа,то для их нормализации необходимо, чтобы старший разряд мантиссы был равен единице, Например, если поступившее на блок нормализации число равно 0,0001101 2 Ю", где 0,0001101 - мантисса числа, а 101 " его порядок, то.для его нормализации необходимо сдвинуть мантиссу на три разряда влево, а из порядка вычесть число 3, т.е. после нормализации получим число 0,11012 ф".ф . Как видно из примера, для нормализации поступающего числа необходимо в мантиссепосчитать количество нулей до первого значащего разряда и осуществить сдвиг мантиссы влево на количество разрядов, равное эцомучислу, а также вычесть из значения порядка укаэанное число.Для подсчета количества нулей вмантиссе до первого значащего разряда служит коммутатор 70 (фиг, 5),на который по входу 35 поступаетмантисса иэ регистров 18. Входящиев состав коммутатора многовходовыеэлементы И 74 из прямых и инверсныхзначений разрядов мантиссы формируют сигналы У - У , где о - разрядность мантиссы, причем на выходекоммутатора 70 формируется единицатолько в одном сигнале У, в зависимости от того, какой разряд мантиссы, начиная со старшего, значащий. Так, если значащим являетсяпервый разряд мантиссы, то появится единица в сигнале У, если первый разряд мантиссы равен нулю,а второй - единице, то появитсяединица на выходе в сигнале У 2 ит.д. При нормализации в шифратор1 с выхода коммутатора 70 поступает код У-У, указывающий, насколько разрядов необходимо произвести сдвиг мантиссы. Ц 1 ифраторвыполняет функцию, обратную де,шифратору, содержит элементы ИЛИ 75и предназначендля преобразованиякода в двоичный позиционный кода-ам, указывающий количество разрядов, на которые необходимо сдвинуть мантиссу. На фиг. 5 приведенпример реализации шифратора 16-разрядного кода (У 1-У ) в 4-разрядныйкод а-а+. Этот код поступает накоммутатор 73, который и производитуказанный сдвиг, а также на сумматор 72 порядка, а котором код вычитается из порядка, поступившего изблока 17 по входу 34,На Фиг. б приведен пример рвализации коммутатора 73 для сдвига 15-разрядной мантиссы на 1-15 разрядов. Коммутация осуществляется в две ступени. Первая ступень содержит элементы И 78, выходы которых соединены с элементом ИЛИ 79. Коммутацией разрядов в первой ступени управляет дешифратор 7, а во второй ступени - дешифратор 77. Первая ступень осуществляет сдвиг на О, 4, 8, 12 разрядов в зависимости от состояния старших разрядов а, и а 4, поступающих на дешифратор 76, Вторая ступень осуществляет сдвиг на 0,1,2,3 разряда в зависимости от состояния младших разрядов аи а , поступающих на дешифратор 77.Процесс накоПления точек результата продолжается до тех пор, пока60 65 Далее производится сдвиг содержимого регистров групп 4 и 5 на одно число (сверху вниз). Числа регистров б и 7 умножаются поочередно на число (мантисса, порядок), сдвинутое в нижние регистры групп 4 и 5. Полученные произведения складываются в сумматоре 16 с нормализованными в блоке 19 результатами предыдущих вычислений, последовательно не будет выбрано из ОЗУ ЭВМ заданное число точек оператора, т,е. пока не будет сигнала с блока 30 сравнения. После выдачи результата накопления цикл начинается сначалаи так до окончания фильтрации входных данных. После этого поступаетсигнал из счетчика 15, который,устанавливает в единицу триггер 61 вблоке 33 управления, запрещаетсяпрохождение импульсов с генератора56.и устройство прекращает работув ожидании новой команды.В процессе вычислений БПФ мантиссы чисел, находящиеся в регист ре группы 7, умножаются поочереднона число, хранящееся в нижнем регистре группы 5. Параллельно насумматоре 8 порядков суммируютсяпорядки указанных чисел, находящие ся в нижних регистрах групп .б и 4.Полученные произведения (мантисса,порядок) складываются с соответствующими числами иэ регистров 2 и 3.Для осуществления сложения снова, 25 как и при свертке, производитсяуравнивание порядков.Уравнивание порядков осуществля-ется на вычитателе 12 путем вычитания порядка полученного произведе ния, поступающего с выхода регистра 10, из порядка, поступающего свыхода регистров 2,под управлениемсигнала 48 блока 33. Если полученнаяразность порядков положительна, то 35 сигнал, поступающий из знаковогоразряда вычитателя 12, пропускаетчерез коммутатор 13 порядок из регистров 2, Этот порядок являетсяпорядком сумьы и записывается в ре гистры 17. Кроме того, сигнал иззнакового разряда вычитателя порядков 12 пропускает на коммутатор 15через коммутатор 14 мантиссу произведения из умножителя 9 при равенстве нулю сигналов на выходах 46 и 47.В коммутаторе 15 мантисса сдвигается вправо на число разрядов, равноеразности порядков, и поступает навход сумматора 16. На второй входсумматора 16 через коммутатор 14поступает мантисса второго слагаемого с выхода регистров 3. В регистры 17 записываются большие порядки,а в регистры 18 - сформированныена сумматоре 16 суюы мантисс.551062715 фюнес И 6 выдвигаемыми из регистров 17 и 18.Вновь полученные суммы записываются в освобождающиеся регистры групп 17 и 18. Эти суммы являются двумя комплексными реэультатаьи этапа БПФ ф 5 которые через блок 19 нормализации и выходной регистр 20 выдаются в ОЗУ ЭВМ. После выдачи первой пары комплексных значений результата вновь повторяется рассмотренный выше цикл вычислений, Отличие заключается толь 0 ко в изменении знаков получакицихся произведений. При этом в регистрах групп 17 и 18 получены два других комплексных значения результата которые выдаются в ОЗУ ЭВМ.Таким обраф 5 зом, в устройстве вычисляются сразу несколько комплексных значения результата БПФ при одних и тех же входных числах.Аналогично при выполнении других 20 операций, например перемножения входных массивов комплексных чисел,разновременного суммирования, устройство позволяет вычислить несколько значений результатов при однократном считывании иэ ОЗУ ЭВМ необходимых входных данных. В отличие от известного предлагаемое устройство позволяет повысить достоверность конечных результатов и эфФективность дальнейшей обработки полученных результатов за счет обработки массивов данных в Формате с плавающей запятой. Использование Формата с плавающей запятой по входу и в процессе вычислений позволяет значительно увеличить диапазон представления исходных чисел, что приводит к увеличению диапазона представления результатов обработки, а значит, к увеличению точности.

СмотретьЗаявка

3490494, 06.09.1982

ЛЬВОВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. ЛЕНИНСКОГО КОМСОМОЛА

ЧЕРКАССКИЙ НИКОЛАЙ ВЯЧЕСЛАВОВИЧ, АНТОНОВ РОМАН ОСИПОВИЧ, КОНДРАТЮК ЮРИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 17/00

Метки: данных, процессор, специализированный

Опубликовано: 23.12.1983

Код ссылки

<a href="https://patents.su/13-1062715-specializirovannyjj-processor-obrabotki-dannykh.html" target="_blank" rel="follow" title="База патентов СССР">Специализированный процессор обработки данных</a>

Предыдущий патент: Устройство для выполнения быстрого преобразования фурье

Следующий патент: Анализатор спектра

Случайный патент: Устройство для двухзонного регулированияскорости вращения двигателя постоянноготока c зависимой системой управленияполем двигателя