Устройство для преобразования выражений в польскую инверсную запись

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1290358

Авторы: Водопьянов, Завьялов, Цымбал

Текст

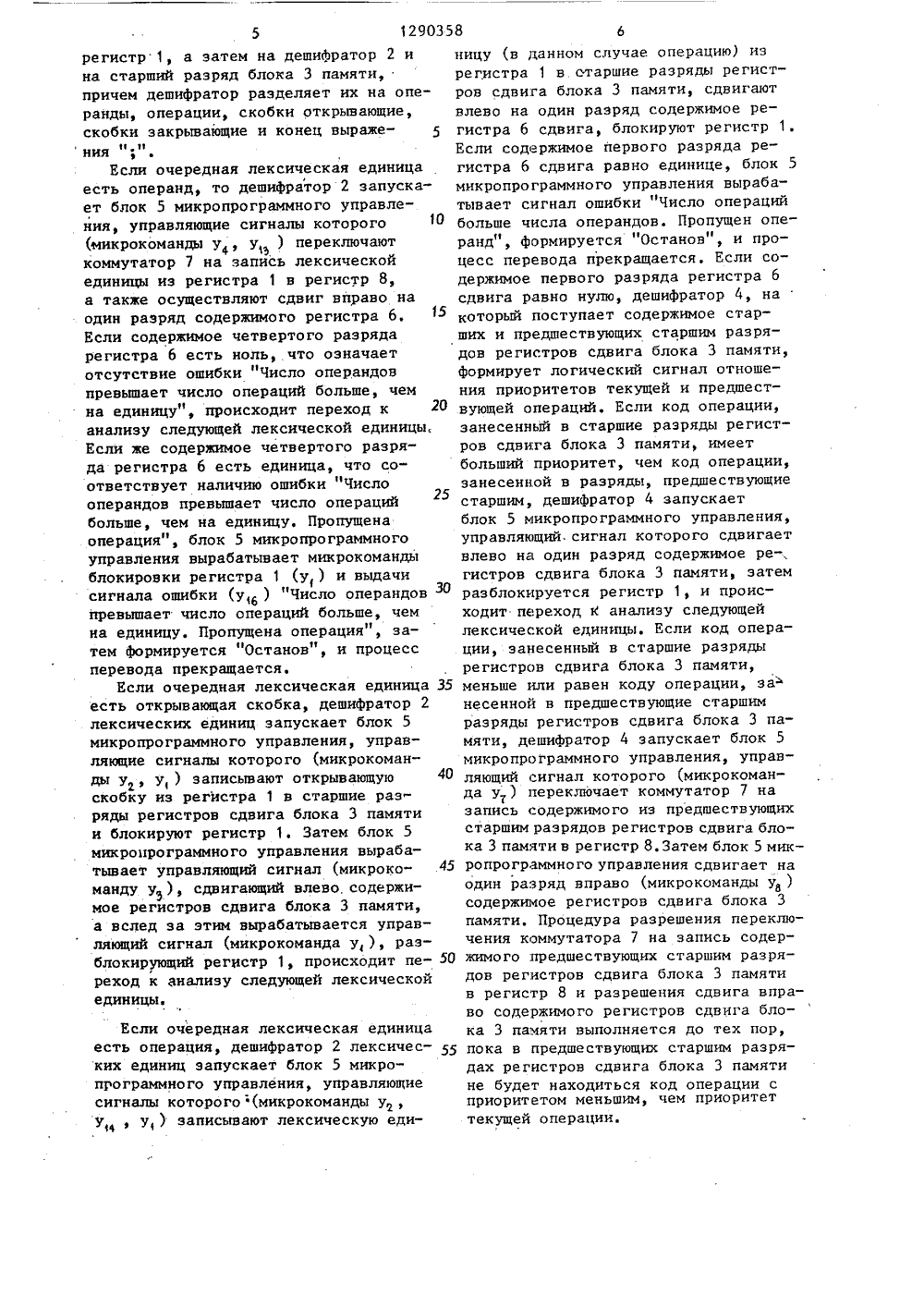

(54) УСТРОЙСТВВЫРАЖЕНИЙ В ПОЛИСЬ ДНЯ ПРЕОБРАЗОВАНИЯ КУЮ ИНВЕРСНУЮ ЗАОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ИСАНИЕ ИЭ А ВТОРСКОМУ СВИДЕТЕЛЬСТ свидетельство СССРС 06 Р 15/38, 1980,видетельство СССРС 06 Р 15/38, 1982. 1) 4 С 06 Р 15/38 9/44(57) Изобретение относится к вычислительной технике. Целью иэобретенияявляется повьппение достоверности работы за счет обеспечения контроляпарности открывающей и эакрывающейскобок, принадлежности символов .входного выражения множеству лексических единиц баланса операторов иопераций, обеспечения классификацииошибок и повьппения быстродействия,17 1290358 18информационный вход которого является выход дешифратора соединен с входоминформационным входом устройства, а признаков отнашений приоритетов блокавыход соединен с первым информацион- микропрограммного управления, выходыным входом коммутатора, с информацион- микрокоманд которого, начиная с четным входом блока памя ти и с входом 5 вертого, соединены соответственно с(дешифратора лексических единиц, выход вторым и третьим управляющими входамикоторого соединен с входом признаков коммутатора, с входами сдвига влеволексических единиц блока микропрограм- и сдвига вправо блока памяти, с вхомного управления, первый выход микро- дами сдвига влево и сдвига вправокоманд которого сое иединен с входом за реверсивного регистра сдвига и с устаписи первого регистра, второй выход новочными входамии блока памяти и ремикрокоманд соединен с первым управ- версивчого регистра сдвига, выходыляю им входом коммутатора, третий вы- разрядов которого соединены с входомход микрокоманд со единен с входом эа- признаков ошибки блока микропрограмписи блока памяти, второй регистр, много управления, выходы сигналоввыход которого является информацион- ошибок которого являются соответственным выходом устроиства, вчход пуска но выходами сигналов ошибок устройстблока микропрограммного управления . ва.является входом пуска устройства,о т л и ч а ю щ е е с я тем, что,202Устройство по п,1, о т л и -с целью повышения быстродействия ич а ю щ е е с я тем, что блок памятиостоверности работы путем обеспечедосто р рсодержит реверсивные регистры сдвига,ния контроля парности открывающей ивходы сдвига влево, сдвига вправо, зазакрывающей скобок, принадлежности в оия множест писи и установочные входы которых явсимволов входного, выражения множестб ланса опера- ляются соответственно входами сдвигаву лексических единиц, аланса опер -торов и операций, о еспеченияий б спечения клас- влево, сдвига вправо, записи и установочным входом блока, входы старшихсификации ошибок, в него введен реа причем ин- Разрядов регистров сдвига соединеныверсивный регистр сдвига, причем и -формационный выход и выход старыход старшего ЗО с информационным входом блока, выходыразряда блока памяти соедине ьединены соот- старших разрядов регистров сдвига иинфор-выходы разрядов, предшествующих старветственно с вторым и третьим ин оршим являются соответственно выходоммационными входами коммутатора и сФстаршего разряда и информационнымвходами дешифратора выход коммутатора подключен к входу второго регистра,35 д5 выходом блока.1 1290358 2Изобретение относится к вычисли- нирование описано блок-схемой микро- тельной технике и может быть исполь- программного .Управления (Фиг,б), где зовано в автоматизированных системах входные сигналы х, хг, х формирует обработки данных н производства про- дешифратор 4, с х по х 8 - дешифрагРамм длЯ электРонных вычислитель тоР 2 лексических единиц, хз, х ных машин (ЭВМ). ,хн - блок 6 контроля, сигналы микроЦелью изобретения является повы- команд с у по у, формирует блок 5 шение достоверности работы путем микропрограммного управления. Содеробеспечения контроля парности откры- жательный смысл входных сигналов и вающей и закрывающей скобок, принад- ф микрокоманд следующий:лежности символов входного выраже 1, если ход операции, занесенный в старшие разряды регистров сдвига блока 3 памяти, имеет больший приоритет, чем код операции, занесенный в предшествующие старшим разряды регистров, О - в противном случае. ния множеству лексических единиц,баланса операторов и операций, обеспечения классификации ошибок и повы 15шения быстродействия.На фиг.1 представлена структурнаясхема устройства на фиг.2 - структурная схема блока памяти, на фиг,3 структурная схема блока микропрограммного управления, на фиг.4 - схема,20реверсивного регистра сдвига, наФиг.5 - схема реверсивного регистрасдвига блока памятина фиг.б - блоксхема микропрограммного управленияустройством,Устройство содержит регистр 1,дешифратор 2 лексических единиц,блок 3 памяти, дешифратор 4, блок 5микропрограммного управления, реверсивный регистр 6 сдвига, коммутатор 7, регистр 8 реверсивные регистры 9 сдвига, программируемая логическая матрица И 10, программируемая логическая матрица ИЛИ 11,узел 12 памяти, элемент ИЛИ 13, генератор 14 тактовых импульсов, триггер 15, элемент 16 задержки, элемент И 17, группу 18 триггеров, группу 19 элементов ИЛИ, группу 20 элементов И, группу 21 триггеров, группу 22 элементов ИЛИ, группу 23 элементов И, элемент НЕ 24, узел 25 за.писи разряда,х = 1, если содержимое старшихразрядов регистров сдвига блока 3 памяти равно значению кода "Пустой символ"ф О - в противном случае. х = гесли содержимое старшихразрядов регистров сдвигаблока 3 памяти равно значению кода открывающей скобки- в противном случае 1, если очередная лексическаяединица исходного выраженияесть открывающая скобка0 - в противном случае.1, если очередная лексическаяединица исходного выраженияесть операнд0 - в противном случае. х = 1, если очередная лексическаяединица исходного выражениях = есть операнд60 - в противном случае. Регистр 1 используется для хране ния очередной лексической единицы исходного выражения, дешифратор 2 лек" сических единиц разделяет лексические единицы на операнды, операции, скобки.Блок 3 памяти - это память с последовательным безадресным принципом записи и чтения. Дешифратор 4 совместно с блоком памяти реализуют логическую функцию выработки и сравнения приоритетов, 55 если очередная лексическаяединица исходного выраженияесть закрывающаяся скобка,- в противном случае. если очередная лексическаяединица исходного выраженияесть конец выражения- в противном случае. х =1, если содер разряда ре гистра 6 с ца,0 - в противн имое третьего рсивного реига есть единиБлок 5 микропрограммного управления организует взйимодействие всех элементов устройства и его функциом случае,У15 1 б если содержимое первого разряда реверсивного регистра 6 сдвига есть единица, - в противном случае. если содержимое четвертого разряда реверсивного регистра 6 сдвига есть единица, - в противном случае. разблокировать/заблокировать 10регистр 1,записать содержимое регист-.ра 1 в М-е (старшие) разрядырегистров сдвига блока памяти; 15сдвинуть влево содержимое регистров сдвига блока памяти,переключить коммутатор 7 назапись из регистра 1,установить начальные значени 20регистра 6 (значение кода0100) и регистров сдвига блока 3 памяти (значение кода "0"в (И) разрядах),выдать сигнал ошибки "Отсутствует закрывающая скобка",переключить коммутатор 7 назапись из (И) разрядов регистров сдвига блока 3 памятия 30сдвинуть вправо на один разряд содержимое сдвига блока 3 памяти,переключить коммутатор 7 назапись из И разрядов регистров сдвига блока 3 памяти;выдать сигнал ошибки "Отсутствует открывающая скобка"выдать сигнал ошибки "Лексическая единица не принадлежит алфавиту лексическихединиц";выдать сигнал ошибки "Числооперандов равно числу операций, Пропущен операнд" 45,сдвинуть вправо на один разряд содержимое регистра 6сдвинуть влево на один разряд/содержимое регистра 6,выдать сигнал ошибки "Число 50операций больше числа операндов. Пропущен операнд",выдать сигнал ошибки "Числооперандов превышает число операций больше чем на единицу. 55Пропущена операция". Регистр 6 проверяет наличие и порядок следования лексических единиц в исходном выражении и совместно сблоком микропрограммного управленияосуществляет классификацию ошибок,Коммутатор 7 управляет передачамилексических единиц, а регистр 8 предназначен для хранения очередной лексической единицы в форме польскойинверсной записи. Реверсивные регистры сдвига блока 3 памяти поразрядносдвигают код операций и совместно сдешифратором 4 осуществляют сравнение приоритетов. Программируемая логическая матрица И 10 совместно спрограммируемой логической матрицей ИЛИ 11 и узлом 12 памяти организуют работу блока микропрограммногоуправления. Элемент ИЛИ 13 вырабатывает сигнал Останов" устройства.Генератор 14 тактовых импульсов совместно с триггером 15 и элемен.том И 17 организуют сигналы запускаустройства. Элемент 16 задержки предназначен для начальной установки узла памяти блока перед пуском устройства,Группа 18 триггеров блока контроляобразует четыре разряда реверсивногосдвигающего регистра, каждый из которых соответствует определенному классу ошибок блока контроля. Группы 19элементов ИЛИ совместно с группамиэлементов И организуют входные цепиреверсивного сдвигающего регистратаким образом, что начальная установка соответствует установке второго триггера (фиг.4) в единичное состояние, а остальных в нулевое.Группа 21 триггеров реверсивногорегистра сдвига блока памяти образуетразряды реверсивного сдвигающего регистра. Группа 22 элементов ИЛИ совместно с группой 23 элементов И и элементом НЕ 24 организуют входные цепи.реверсивного сдвигающего регистраблока памяти таким образом, что начальная установка соответствует установке разряда, предшествующего старшему (фиг.5), в "0". При этом элемент НЕ и связанные с ним элементы Иобразуют узел 25 записи разряда регистра 1, предназначенный для организации информационного входа реверсивного регистра сдвига блока памяти. Устройство работает следующим образоМ. Лексические единицы исходного выражения последовательно поступают на1290358 5регистр 1, а затем на дешифратор 2 и на старший разряд блока 3 памяти, причем дешифратор разделяет их на операнды, операции, скобки открывающие, скобки закрывающие и конец выражения ц11Если очередная лексическая единица есть операнд, то дешифратор 2 запускает блок 5 микропрограммного управления, управляющие сигналы которого (микрокоманды у , у 1 ) переключают5коммутатор 7 на запись лексической единицы из регистра 1 в регистр 8, а также осуществляют сдвиг вправо на один разряд содержимого регистра 6, Если содержимое четвертого разряда регистра 6 есть ноль, что означает отсутствие ошибки "Число операндов превышает число операций больше, чем на единицу", происходит переход к 20 анализу следующей лексической единицы, Если же содержимое четвертого разряда регистра 6 есть единица, что соответствует наличию ошибки "Число операндов превышает число операций25 больше, чем на единицу, Пропущена операция", блок 5 микропрограммного управления вырабатывает микрокоманды блокировки регистра 1 (у) и выдачи сигнала ошибки (у, ) "Число операндов превышает число операций больше, чем на единицу. Пропущена операция", затем формируется "Останов", и процесс перевода прекращается.Если очередная лексическая единица 35 есть открывающая скобка, дешифратор 2 лексических единиц запускает блок 5 микропрограммного управления, управляющие сигналы которого (микрокоманды у, у, ) записывают открывающую 40 скобку из регистра 1 в старшие разряды регистров сдвига блока 3 памяти и блокируют регистр 1. Затем блок 5 микропрограммного управления вырабатывает управляющий сигнал (микроко манду у), сдвигающий влево, содержимое регистров сдвига блока 3 памяти, а вслед за этим вырабатывается управляющий сигнал (микрокоманда у,), разблокирующий регистр 1, происходит пе реход к анализу следующей лексическойединицы. Если очередная лексическая единица есть операция, дешифратор 2 лексичес ких единиц запускает блок 5 микропрограммного управления, управляющие сигналы которого (микрокоманды у, у, , у ) записывают лексическую единицу (в данном случае операцию) из регистра 1 в.отаршие разряды регистров сдвига блока 3 памяти, сдвигают влево на один разряд содержимое регистра 6 сдвига, блокируют регистр 1. Если содержимое первого разряда регистра 6 сдвига равно единице, блок 5 микропрограммного управления вырабатывает сигнал ошибки "Число операций больше числа операндов. Пропущен операнд", формируется "Останов", и процесс перевода прекращается. Если содержимое первого разряда регистра 6 сдвига равно нулю, дешифратор 4, накоторый поступает содержимое старших и предшествующих старшим разрядов регистров сдвига блока 3 памяти, формирует логический сигнал отношения приоритетов текущей и предшествующей операций, Если код операции, занесенный в старшие разряды регистров сдвига блока 3 памяти, имеет больший приоритет, чем код операции, занесенной в разряды, предшествующие старшим, дешифратор 4 запускает блок 5 микропрограммного управления, управляющий сигнал которого сдвигает влево на один разряд содержимое ре-., гистров сдвига блока 3 памяти, затем разблокируется регистр 1, и происходит переход к анализу следующей лексической единицы. Если код операции, занесенный в старшие разряды регистров сдвига блока 3 памяти, меньше или равен коду операции, за несенной в предшествующие старшим разряды регистров сдвига блока 3 памяти, дешифратор 4 запускает блок 5 микропрограммного управления, управляющий сигнал которого (микрокоманда у ) переключает коммутатор 7 на запись содержимого из предшествующихстаршим разрядов регистров сдвига блока 3 памяти в регистр 8. Затем блок 5 микропрограммного управления сдвигает на один разряд вправо (микрокоманды у 8 ) содержимое регистров сдвига блока 3 памяти. Процедура разрешения переключения коммутатора 7 на запись содержимого предшествующих старшим разрядов регистров сдвига блока 3 памяти в регистр 8 и разрешения сдвига вправо содержимого регистров сдвига блока 3 памяти выполняется до тех пор, пока в предшествующих старшим разрядах регистров сдвига блока 3 памяти не будет находиться код операции с приоритетом меньшим, чем приоритет текущей операции.1290358 50 55 Если очередная лексическая единица есть закрывающая скобка, дешифратор 2 запускает блок 5 микропрограммного управления, управляющие сигналы которого (микрокоманды у, у,) сдвигают вправо на один разряд содержимое регистров сдвига блока 3 памяти и блокируют регистр 1. Значение содер-, жимого старших разрядов регистров сдвигов блока 3 памяти, поступает на дешифратор 4. Если содержимое старших разрядов регистров сдвига блока 3 памяти есть код открывающей скобки, то дешифратор 4 запускает блок 5 микропрограммного управления, управляющий сигнал которого (микро- команды у ) сдвигает вправо содерВжимое регистровсдвига блока 3 памяти, происходит разблокирование регистра 1 и переход к анализу следующей лексической единицы, т.е. закрывающая и первая из встретившихся открывающих скобок в регистр 8 не попадают. Если содержимое старших разрядов регистров сдвига блока 3 памяти не является кодом открывающей скобки, дешифратор 4 запускает блок 5 микропрограммного управления, управляющий сигнал которого (микрокоманда у ) переключает коммутатор 7 на запись содержимого старших разрядов регистров сдвига блока 3 памяти в регистр 8, сдвигает на один разряд вправо содержимое регистров сдвига блока 3 памяти, Дешифратор 4 определяет значение кода старших разрядов регистров сдвига блока 3 памяти. Если зто значение есть код пустого символа, что означает отсутствие в исходном выражении символа открываю-. щей скобки, дешифратор 4 запускает блок 5 микропрограммного управления, управляющий сигнал которого (микро- команда ущ ) формирует сигнал ошибки "Отсутствует открывающая скобка", формирует "Останов, и процесс перевода прекращается. Если значение кода старших разрядов регистров сдвига .блока 3 памяти не является кодом пустого символа, дешифратор 4 определяет значение кода старших разрядов регистров сдвига блока 3 памяти, и процесс анализа на наличие в блоке памяти открывающей скобки продолжается до тех пор, пока не будет найдена открывающая скобка (что соответствует правильности исходного выражения), или обнаружен код пустого символа (что соответствует ошибке).Ф Если очередная лексическая единицаесть символ "Конец выражения", тодешифратор 2 запускает блок 5, управляющий сигнал которого (микрокоманда у,) блокирует регистр 1. Дешифратор 4 определяет значение кода стар-ших разрядов сдвига блока 3 памяти.Если значение кода старших разрядоврегистров сдвига блока 3 памяти есть 10 код пустого символа, блок 5 анализирует значение содержимого третьегоразряда регистра 6 сдвига. Если этозначение равно единице, то блок 5 переключает коммутатор 7 на запись со держимого регистра 1 в регистр 8(микрокоманда у). Процесс переводанормально завершен, Устройство готовок переводу следующего выражения. Если значение третьего разряда регистра 20 6 сдвига равно нулю, то регистр 6 запускает блок 5 микропрограммного уп-,равления, формирует сигнал у, ошибки "Число операндов равно числу операций, Отсутствует операнд", выраба тывается "Останов", и процесс перевода прекращается. Если значение кодастарших разрядов регистров сдвигаблока 3 памяти отлично от кода пустого символа, дешифратор 4 запускает блок 5 30 микропрограммного управления, которыйанализирует значение выходного сигнала дешифратора 4. Если в старших разрядах регистров сдвига блока 3 памяти находится лексическая единица(скобка открывающая), то блок 5 микропрограммного управления вырабатываетсигнал у ошибки "Отсутствует закрывающая скобка" и осуществляет остановработы устройства. Если ошибка отсут ствует, то дешифратор 4 запускаетблок 5, управляющий сигнал которого(микрокоманда у ) переключает коммутатор 7 на запись из старших разрядов регистров сдвига блока 3 памяти в ре"45 гистр 8, и происходит сдвиг вправо на один разряд содержимого регистровсдвига блока 3 памяти. Затем дешифратор 4 определяет значение кода старших разрядов.регистров сдвигаблока 3памяти и запускает блок 5; Процессповторяется до тех пор, пока не будетобнаружен код пустого символа илине будет обнаружен код открывающейскобки (что свидетельствует о наличииошибки в исходном выражении) в старших разрядах регистров сдвига блока 3 памяти, определяемых дешифратором 4.Если очередная лексическая единица не является ни операндом, ни опе9 1290358 рацией, ни открывающей скобкой, ни к закрывающей скобкой, ни символом кон" с ца выражения, то дешифратор 2 запус- к кает блок 5 микропрограммного управ- и ления, который формирует сигнал ошиб р ки "Лексическая единица не принадлежит б алфавиту лексических единиц", блокируется регистр 1, вырабатывается "Останов", и процесс перевода прекраэ щается. 10 сП р и м е р 1, Пусть входное вы- к ражение имеет вид АхВ+С/ (П-Е), где и ";" используется как лексическая еди- ц ница "Конец выражения".вПроцесс перевода исходного выраже н ния в польскую инверсную запись заклю,чается в следующем. Производится начальная установка значений регистра 6 и блока 3 памяти, т.е, в регистр 6 заносится код 0100, в разря.э ды, предшествующие старшим разрядам регистров сдвига блока 3 памяти, заносится значение кода пустого симво- с ла. На регистр 1 поступает лексическая единица "А", которая определяет Р ся дешифратором 2 как операнд, и с помощью блока 5 микропрограммногоуправления производится подключение входа коммутатора 7 на запись лексической единицы "А" из регистра 1 в 30 регистр 8, а также сдвиг вправо на один разряд содержимого регистра 6 (на регистре образуется код 0010).Блок 5 микропрограммного управления анализирует значение четвертого разряда регистра 6. Так как оно равно нулю, производится переход к следующей лексической единице. 10 На регистр 1 поступает следующая лексическая единица "х", которая фиксируется дешифратором 2 как знак операции, Производится блокировка регистра 1. Из регистра 1 код "х" записывается в старшие разряды регистров сдвига блока 3 памяти. Осуществляется сдвиг влево на один разряд содержимого регистра 6, т,е, на указанном регистре образуется код 0100. При этом дешифратор 4 формирует значение отсутствия ошибки, так как значение первого разряда регистра 6 равно нулю. Значение кода "х", занесенное в старшие разряды регистров сдвига блока 3 памяти, и значение кода пустого символа которое находится в предшествующих старшим разрядах регистров сдвига блока 3 памяти, поступают на дешифратор 4,оторый формирует значение выходногоигнала, по которому с помощью блоа 5 микропрограммного управленияроизводится сдвиг влево на один разяд содержимого регистров сдвигалока 3 памяти. После этого регистр 1азблокируется.Следующая лексическая единица "В"аписывается в регистр 1 и дешифруетя как операнд, С помощью блока 5оммутатор 7 подключается на записьз регистра 1, и лексическая единиа ."В" переписывается из регистра 1регистр 8, происходит сдвиг вправоа один разряд содержимого региста 6 (на регистре образуется код010), Производится переход к следующей лексической единице,Очередная лексическая единица "+"аписывается в регистр 1 и определятся дешифратором 2 как операция,локируется регистр 1, осуществляетсядвиг на один разряд влево содержимого регистра 6, т.е, на укаэанномегистре образуетея код 0100. Таккак значение первого разряда регист-.ра б сдвига равно нулю, дешифратор 4Формирует значение х= О,Из регистра 1 код "+" записываетсяв старшие разряды регистров сдвигаблока 3 памяти, Значение кода "+",занесенное в старшие разряды регистров сдвига блока 3 памяти, и значениекода "х", занесенного в предшествующие старшим разряды регистров сдвигаблока 3 памяти, поступают на дешифратор 4, который Формирует значениевыходного сигнала х= О, так какприоритет предыдущей операции больше,40 чем последующей. С помощью блока 5коммутатор 7 переключается на записьиэ предшествующих старшим разрядоврегистров сдвига блока 3 памяти ипроизводится запись содержимого этих5 разрядов в регистр 8 (в данном случае лексической единицы "х"). Затемосуществляется сдвиг на один разрядвправо содержимого регистров сдвигаблока 3 памяти и осуществляется за 50 пись в старшие разряды регистров сдвига блока 3 памяти лексической единицы "+" с регистра 1, Значения старшихи предшествующих старшим разрядовсдвига блока 3 памяти поступают на55 дешифратор 4, который формирует вы ходной сигнал х,= 1, так как приоритет операции "+", код которой хранится в старших разрядах, больше приоритета пустого символа, хранимого впредшествующих старшим разрядах регистров блока 3 памяти. С помощью блока 5 производится сдвиг влево наодин разряд содержимого регистровсдвига блока 3 памяти. После этого ре гистр 1 разблокируется.Следующая лексическая единица "С"записывается в регистр 1, определяется дешифратором 2 как операнд, и спомощью блока 5 производится переключение входа коммутатора 7 на записьоперанда "С" в регистр 8, а такжесдвиг вправо на один разряд содержимого регистра 6 (на регистре образуется код 0010), Так как значение четвертого разряда регистра 6 равно нулю,блок 5 переходит к управлению работойустройства к анализу следующей лексической единицы,Очередная лексическая единица "/" 20определяется дешифратором 2 как операция. Производится блокировка регистра 1. Из регистра 1 с помощью блока 5код "/" записывается в старшие разряды регистров сдвига блока 3 памяти.Осуществляется сдвиг влево на одинразряд содержимого регистра 6 .(на регистре образуется код 0100). При этомдешифратор 4 формирует сигнал отсутствия ошибки. Значение кода "/", занесенного в старшие разряды регистровсдвига блока 3 памяти, и значение ко-да "+", занесенное ранее и находящееся в предшествующих старшим разрядахрегистров сдвига блока 3 памяти, поступают на дешифратор 4, который формирует значение выходного сигналах, = 1, по которому с помощью блока 5производится сдвиг влево на один разряд содержимого регистров сдвига блока 3 памяти, после чего регистр 1разблокируется,Очередная логическая единица "С"записывается в регистр 1 и определяется дешифратором 2 как скобка открывающая. С помощью блока 5 блокируется регистр 1, и значение кода "С"переписывается из регистра 1 в старшие разряды регистров сдвига блока 3памяти. После этого осуществляется 50сдвиг влево на один разряд содержимого регистров сдвига блока 3 памяти, регистр 1 разблокируется.1 1Очередная лексическая единица Э принимается на регистр 1, Онаявляется операндом. На регистре 6 образуется код 0010, и код Ъ" записывается в регистр 8,На регистр 1 принимается очереднаялексическая единица "-", которая определяется дешифратором 2 как операция, Производится блокировка регистра 1, Код "-" из регистра 1 записывается в старшие разряды регистровсдвига блока 3 памяти, Осуществляется сдвиг влево на один разряд содержимого регистра 6 (на регистре образуется код 0100). При этом дешифратор 4 формирует сигнал отсутствияошибки, а дешифратор .2, на которыйпоступают значения старших разрядов(код "-") и предшествующих старшимразрядов (код "С") регистров сдвигаблока 3 памяти, формирует выходнойсигнал х,= 1, по которому с помощьюблока 5 производится сдвиг влево наодин разряд содержимого регистровсдвига блока 3 памяти, После этогорегистр 1 разблокируется,Очередная лексическая единица "Е"принимается на регистр 1. Она является операндом. На регистре 6 образуется код 0010, и код "Е" записывается в регистр 8,На регистр 1 принимается следующая лексическая единица ")". Дешифратором 2 она определяется как скобка закрывающая. С помощью блока 5осуществляется сдвиг на один разрядвправо содержимого регистров сдвигаблока 3 памяти и блокируется ре-,гистр 1, Дешифратор формирует значение выходного сигнала х = О, .так какв старших разрядах регистров сдвигаблока 3 памяти находится код лексической единицы -" (т.е, код, отличный от открывающей скобки). С помощьюблока 5 осуществляется переключениекоммутатора 7 на запись из старшихразрядов сдвига блока 3 памяти, и кодлексической единицы "-." переписывается в регистр 8. Затем осуществляетсясдвиг вправо на один разряд содержимого регистров сдвига блока 3 памяти.Дешифратор 4 формирует значение выходного сигнала х = О, так как значения старших разрядов регистровсдвига блока 3 памяти не равны значению кода "Пустой символ", что означает наличие в блоке 3 памяти кодовопераций и скобок, т.е. необходимостьдальнейшего перевода с целью обнаружения окружающей скобки в блоке 3 памяти. Сигнал с выходом дешифратора 4запускает блок 5 микропрограммногоуправления, который анализирует значение выходного сигнала и, так какния символов соответствует польской инверсной записи входного выражения,П р и м е р 2. Пусть входное выражение имеет вид А + В/ ; , т.е. содержит ошибку - отсутствие открывающей скобки.Процесс перевода входного выражения и обнаружения ошибки заключается в следующем, На регистр 1 поступает лексическая единица "А", которая является операндом и переписывается в регистр 8, Очередная лексическая единица "+" поступает на регистр 1, дешифрируется как операция и записывается в старшие разряды регистров сдвига блока 3 памяти, после чего осуществляется сдвиг содержимого регистров блока 3 памяти на один разряд влево, так как значение выходного сигнала х дешифратора 4 равно Разблокируется регистр 1.На регистр 1 поступает лексическая единица "В", которая является операндом и переписывается в регистр 8,Очередная лексическая единица ")" поступает на регистр 1, дешифрируется как скобка закрывающая. Блокируется регистр 1, и осуществляется сдвиг вправо на один разряд содержимого регистров сдвига блока 3 памяти. Дешифратор 4 формирует выходной сигнал х = О, так как в старших разрядах регистров сдвига блока 3 памяти не находится код открывающей скобки (там находится код лексической единицы "+") и запускает блок 5, который разрешает запись кода "+" из старших разрядов сдвига блока 3 памяти через коммутатор 7 в регистр 8, а затем разрешает сдвиг вправо на один разряд содержимого регистров сдвига блока 3 памяти. В старших разрядах регистров сдвига блока 3 памяти образуется код пустого символа. Дешифратор 4 формирует выходной сигнал х = 1, так как значение старших разрядов регистров сдвига блока 3 памяти равно коду пустого символа и запускает блок 5, который формирует сигнал ошибки "Отсутствует открывающая скобка" и формирует останов работы устройства.П р и м е р 3, Пусть входное выражение имеет вид АВ + ; , т.е. содержит ошибку - подряд идущие операнды с пропущенным знаком операции между ними. Таким образом, на регистр 1 поступило выражение А х В + С / (П - Е);а через регистр 8 на выход устройствавыражение поступило в виде АВ х СВЕ - / + ; . Полученный порядок следовах = 1 (в старших разрядах регистровэсдвига блока 3 памяти находится код ,открывающей скобки), блок 5 разрешает сдвиг вправо на один разряд содержимого регистров сдвига блока памяти. 5 При этом значение кода открывающей скобки, находившееся до сдвига в старших разрядах регистров сдвига блока 3 памяти, после сдвига теряется и в регистр 8 не попадает. Разблокирует - 10 ся регистр 1. Очередная лексическая единица ";" записывается на регистр 1 и дешифри,руется как код конца выражения. Де шифратор 2 запускает блок 5, который блокирует регистр 1. Дешифратор 4 Формирует значение выходного сигнала х = О , так как значение старших разрядов регистров сдвига блока 3 памяти 20 не равно коду пустого символа, а равно коду операции "/", и значение выходного сигнала х = О, так как значе 3ние старших разрядов регистров сдвига блока 3 памяти не равно значению кода 25 открывающей скобки, и запускает блок 5, который переключает коммутатор 7 на запись со старших разрядов регистровсдвига блока 3 памяти (лексическая единица "/"переписывается 30 в регистр 8), а затем разрешает сдвиг вправо на один разряд содержимого регистров сдвига блока 3 памяти, и в . старшие разряды регистра сдвига блока 3 памяти попадает лексическая еди ница "+". Так как дешифратор 4 формирует значения выходных сигналов х =2 = О, х= О, аналогичным образом лекси;ческая единица "+" переписывается в регистр 8, и после сдвига в старших , 40 разрядах регистров сдвига блока памяти образуется код пустого символа. В этом случае дешифратор 4 Формируетзначение выходного сигнала х = 1 иязапускает блок 5, который анализирует 45 значение третьего разряда регистра 6,а, так как значение последнего равноединице (отсутствие ошибки), блок 5разрешает переключение коммутатора 7 на запись лексической единицы ";" иэ 50регистра 1 в регистр 8. Устройствозакончило перевод выражения и готовок приему следующего выражения. Процесс обнаружения ошибки заключается в следующем. Первая лексичес1290358 15кая единица "А" поступает на регистр 1. Дешифрируется как операнд.Дешифратор 2 запускает блок 5, который записывает лексическую единицу"А" регистра 1 в регистр 8 через коммутатор 7 и разрешает сдвиг вправона один разряд содержимого регистра 6,где после сдвига образуется код 0010(при начальной установке был код0100), Блок 5 анализирует значение Остаршего разряда регистра 6 и, таккак зто значение равно нулю, производит переход к следующей лексическойединице,Очередная лексическая единица "В" 15поступает на регистр 1. Она являетсяоперандом, с помощью блока 5 "В" пере.писывается в регистр 8, осуществляется сдвиг вправо на один разряд содержимого регистра 6, где образуется 20код 0001. Блок 5 микропрограммногоуправления анализирует значение старшего разряда регистра 6 и, так каконо равно единице, выдает сигнал у,ошибки "Число операндов превышает 25число операций больше чем на единицу.Пропущена операция, блокирует регистр 1 и формирует останов работыустройства.П р и м е р 4. Пусть входное выра-ЗОжение имеет вид А + ХВ, т.е. содержитошибку - пропущен операнд.Процесс перевода и обнаруженияошибки заключается в следующем, Первая лексическая единица "А" есть.операнд, Она переписывается,в регистр 8,на регистре 6 формируется код 0010.Следующая лексическая единица "+"есть операция. Она записывается вблок 3 памяти, на регистре 6 формируется код 0100. Очередная лексическая единица "х" есть операция. Оназаписывается в блок 3 памяти, блокируется регистр 1, и после сдвига влево на один разряд содержимого регистра 6 на нем образуется код 1000.Блок 5 анализирует значение первогоразряда регистра 6 и, так как оно равно единице, выдает сигнал у ошибкиЧисло операций больше числа операндов. Пропущен операнд" и формируетостанов работы устройства. 16Лексическая единица "А" переписывается в регистр 8. Лексическая единица "+" записывается в регистры сдвига блока 3 памяти, осуществляется сдвиг на один разряд вправо содержимого регистров сдвига блока 3 памяти. Очередная лексическая единица дешифрируется как скобка закрывающая. С помощью блока 5 блокируется регистр 1.и осуществляется сдвиг вправо на один разряд содержимого регистров сдвига блока 3 памяти, в результате чего в старших разрядах регистров сдвига блока 3 памяти образуется лексическая единица "+", которая записывается в регистр 8, и осуществляется сдвиг на один разряд вправо содержимого регистров сдвига блока 3 памяти, так как в старших разрядах регистров сдвига блока 3 памяти образуется код лексической единицы "(", и так как х = 1, осуществляется сдвиг вправо на один разряд содержимого регистров сдвига блока 3 памяти (значение кода "(" теряется) и производится переход к следующей лексической единице исходного выражения.Очередная лексическая единица ";" дешифрируется как конец выражения. Дешифратор 2 запускает блок 5, который блокирует регистр 1. Так как в старших разрядах регистров сдвига блока 3 памяти находится код лексической единицы "(" (вторая из скобок потеряна, так как была встречена закрывающая скобка, а первая из открывающих скобок присутствует вблоке 3 памяти), дешифратор 4 формирует значение выходного сигнала х = 0й и запускает блок 5, который анализирует значение выходного сигнала, формируемого дешифратором 4, а так как х = 1, блок 5 формирует сигнал у ошибки "Отсутствует закрывающая скобка" и формирует останов работы устройства. Пропущенный операнд будет обнаружен после исправления ошибки, связанной с отсутствием закрывающей скобки, при повторном переводе выражения в польскую инверсную запись, П р и м е р 5. Пусть исходное выражение имеет вид А +) ; , т.е, пропущена закрывающая скобка и опе" ранд, Лексические единицы "(", "(" заносятся в регистры сдвига блока 3 па-Мяти. Формула изобретения 1, Устройство для преобразованиявыражений в польскую инверсную запись,содержащее дешифратор, первый регистр,

СмотретьЗаявка

3950536, 30.08.1985

ПРЕДПРИЯТИЕ ПЯ Р-6668

ВОДОПЬЯНОВ ВИТАЛИЙ КОНСТАНТИНОВИЧ, ЗАВЬЯЛОВ ВАЛЕРИЙ НИКОЛАЕВИЧ, ЦЫМБАЛ ВАЛЕРИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 17/17, G06F 17/27, G06F 9/44

Метки: выражений, запись, инверсную, польскую, преобразования

Опубликовано: 15.02.1987

Код ссылки

<a href="https://patents.su/12-1290358-ustrojjstvo-dlya-preobrazovaniya-vyrazhenijj-v-polskuyu-inversnuyu-zapis.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для преобразования выражений в польскую инверсную запись</a>

Предыдущий патент: Устройство для определения второго момента

Следующий патент: Устройство для диагностики электрических цепей

Случайный патент: 413251