Устройство для приема и градиентного декодирования избыточных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

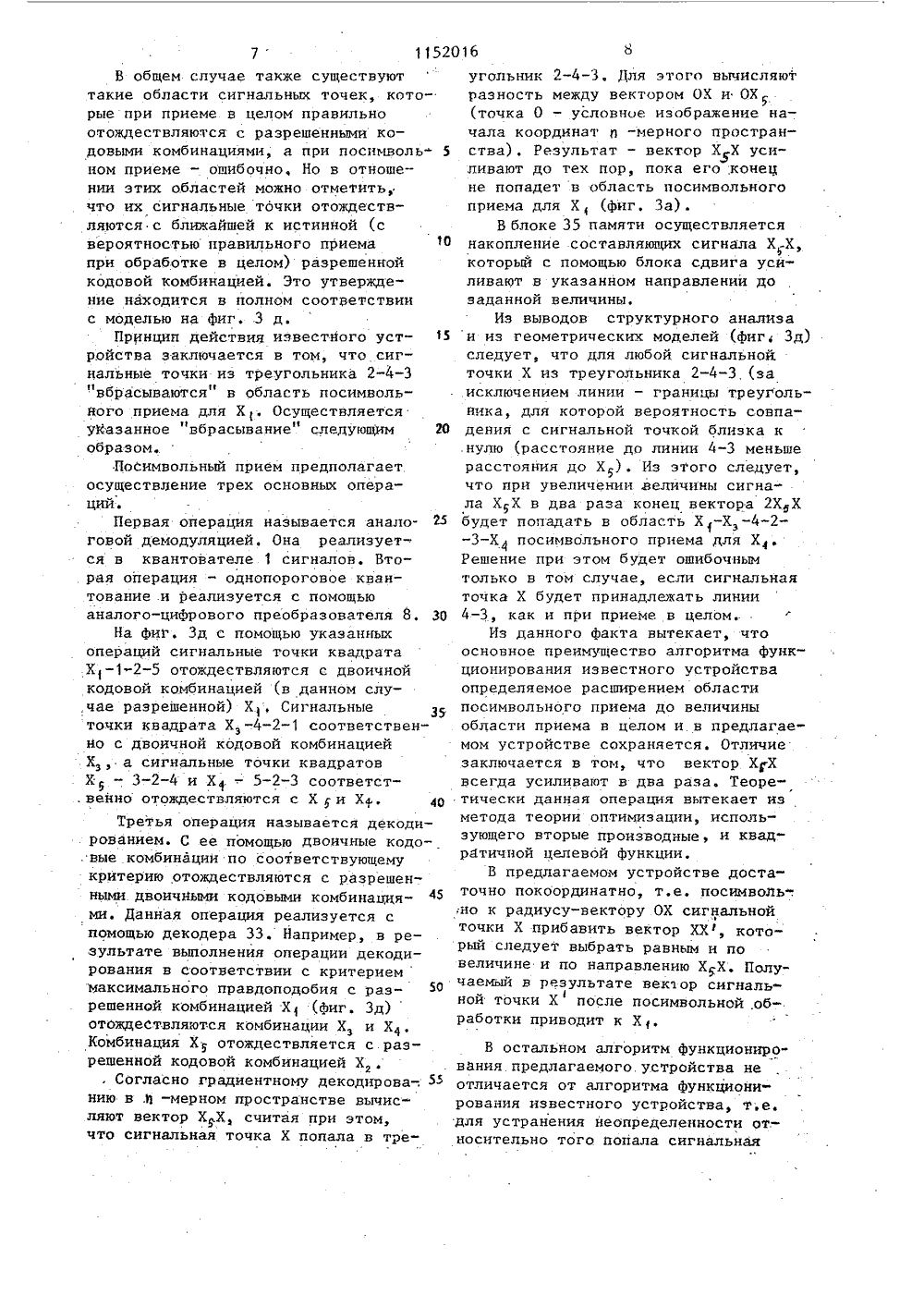

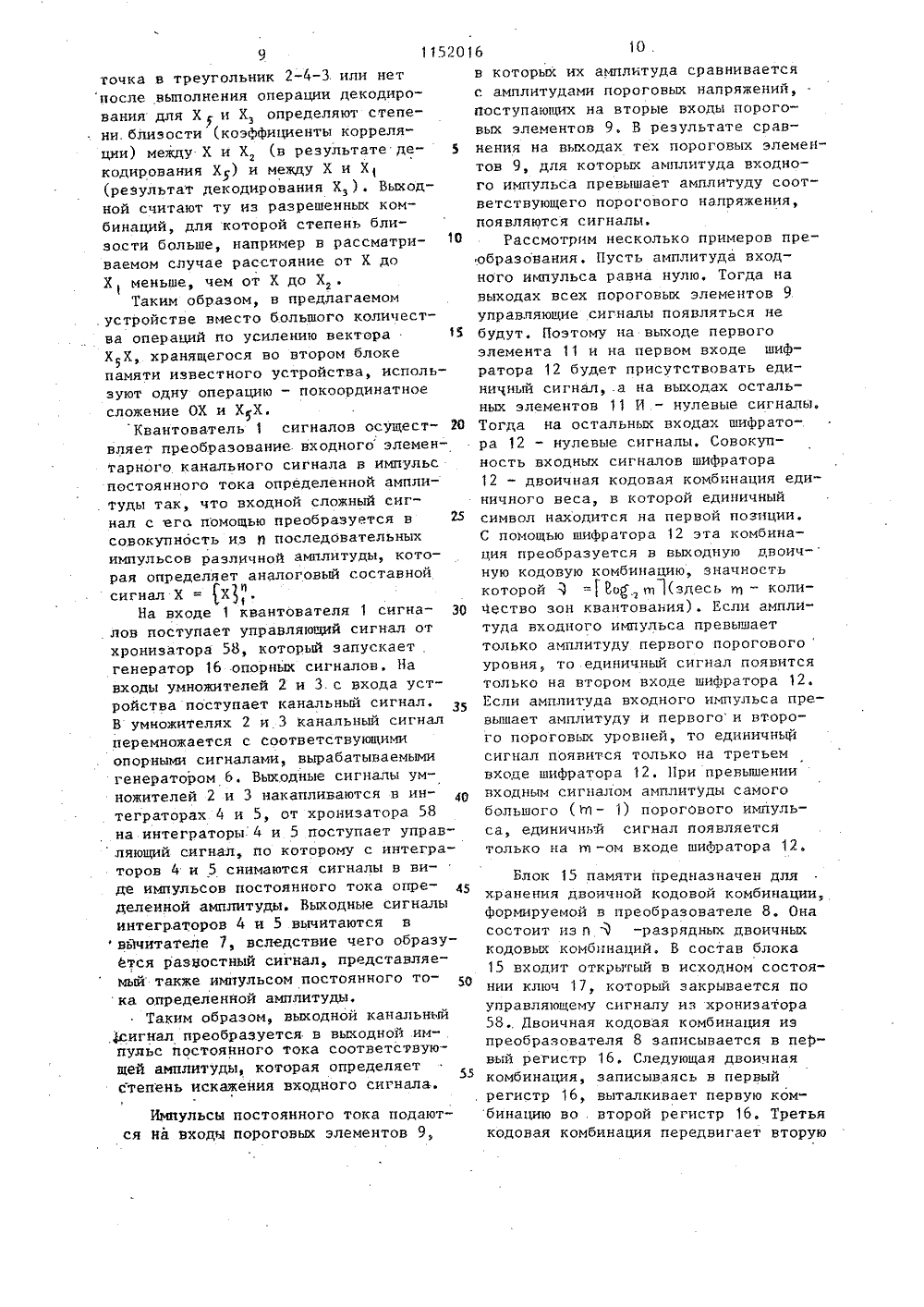

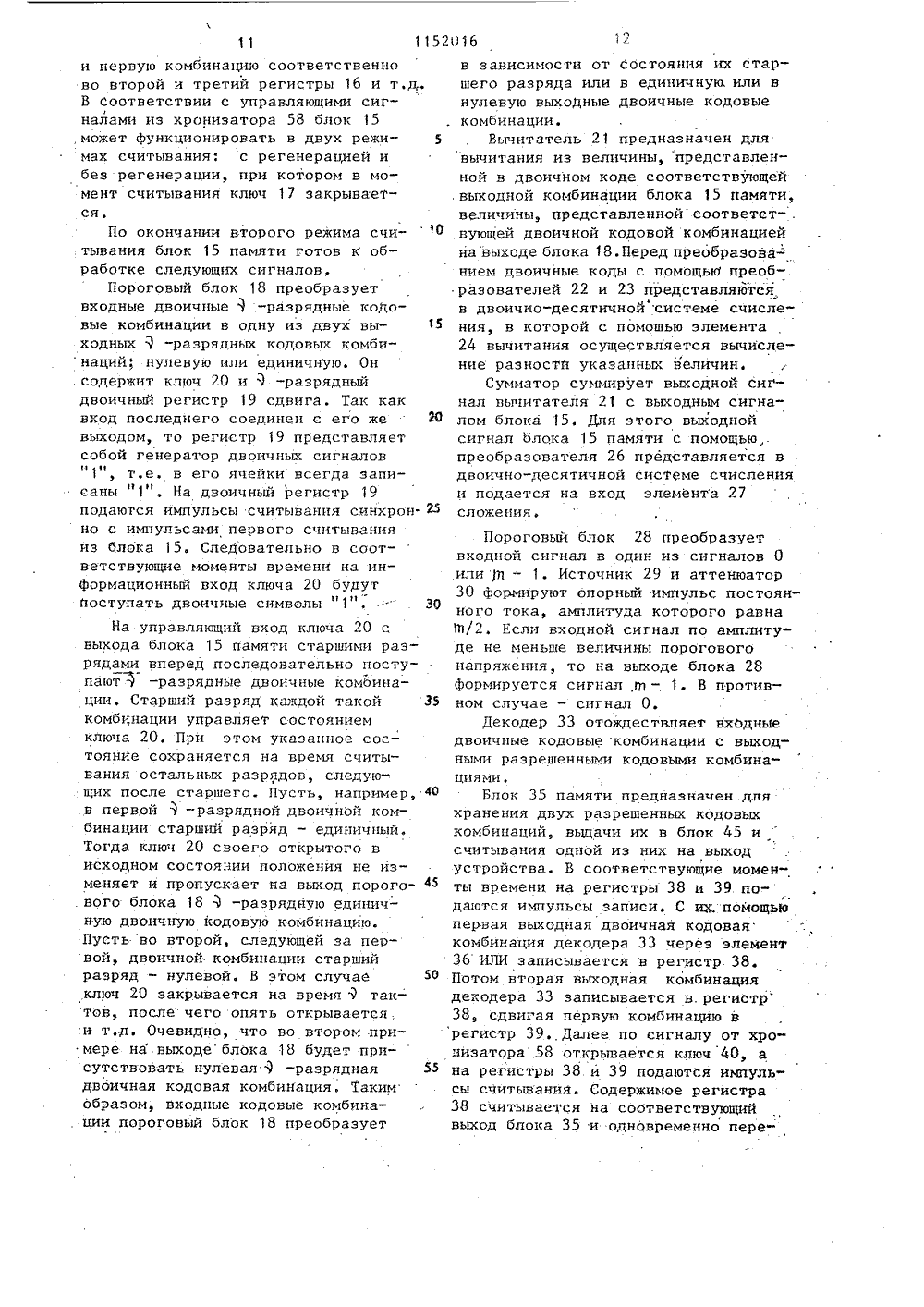

ТОРСНОМУ С интег налов соедин ственн еи,в вого нены вход вого ны и вате ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТИРЫТИЙ(56) 1. Бородин Л,Ф. Введение в теорию помехоустойчивого кодирования.М "Советское радио", 1968, с, 270,рис. 3.03,2. Авторское свидетельство СССРФ 801760, кл, Н 04 Ь 17/30,Н 04 Ь 1/10, 1976 (прототип).(54)(57) 1. УСТРОЙСТВО ДЛЯ ПРИЕМА ИГРАДИЕНТНОГО ДЕКОДИРОВАНИЯ ИЗБЫТОЧНБИ СИГНАЛОВ, содержащее квантователь сигналов, первый вход которогоявляется входом устройства, второйвход подключен к первому выходу хронизатора, выход квантователя сигналов соединен с входом аналого-цифрового преобразователя, выходы которога соединены с соответствующими первыми входами первого блока памяти,выход первого блока памяти соединенс первыми входами первого порогового блока, блока управления выдачейинформации и вычитателя, выход первого порогового блока соединен спервым входом декодера и вторымвходом вычитателя, сумматор, выход,которого. соединен с входом второгопорогового блока, выход декодерасоединен с первым входом второгоблока памяти, первый, второй выходыи второй вход которого подключенысоответственно к второму, третьемувходам и к выходу блока управлениявыдачей информации, третий выходвторого блока памяти является выходом устройства, о т л и ч а ю щ е -е с я тем, что, с целью упрощения устройства, выход первого блока памяти и выход вычитателя соединены соответственно с первым и вторым входами сумматора, выход второго порогового блока соединен с первым входом регистра, выход регистра соединен с вторым входом декодера, вто-, рой, третик, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятью, одиннадцатыи и двенадцатый выходы хронизатора соединены соответственно с третьим входом квантователя сигналов, с вторым, третьим входами первого блока памяти, с объединенными вторым входом первого порогового блока и третьими входами вычитателя и сумматора, с третьим входом декодера, с третьим, четвертым, пятым, шестым входами второго блока памяти, с четвертым входомюФ блока управления выдачей информации и с вторым входом регистра. 2. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что квантователь сигналов содержит умножители,раторы, генератор опорных сиги вычитатель, первый и второй ы генератора опорных сигналов ены с первыми входами соответо первого и второго умножите-. ыходы которых соединены с первходами соответственно первого рого интеграторов, выходы пери второго интеграторов соедисоответственно с первым и вторым ми вычитателя, вторые входы пери второго умножителей объЕдинеявляются первым входом квантоя сигналов, вход генератора, 1152016Никуленковай КорректорО. ТигорМ ставитель хред М.Па едактор И,.Дерба аказ 2995 е Филиал ППП "Патент", г. Ужгород, ул, Проектная, 4 ВНИИПИ Гос по дела 113035, Москварственного комит изобретений и от -35, Раушская на Подпита СССРрытийд. 4/1152016 опорных сигналов является вторымвходом квантователя сигналов, вторыевходы первого и второго интеграторов объединены и являются третьимвходом квантователя сигналов, выходвычитаФеля является выходом квантователя сигналов.3. Устройство по и. 1, о т л и - ч а ю щ е е с я тем, что блок управления выдачей йнформации содержит ключи, сумматоры, вычитатель и преобразователь кода, выход преобразователя кода соединен с первыми вхо.дами первого, второго, третьего и четвертого ключей, выходы первого и второго ключей соединены через соответствующие первый и второй сумматоры с первым й вторым входами третье 1Изобретение относится к электро" связи и может быть использовано в приемных устройствах систем передачи телеметрической информации, исполь-. Зующих длинные и сверхдлинные помехоустойчивые коды.Известно устройство для приема ,избыточной информации, содержащее приемник, пороговый блок и декодер 1Недостатком данного устройства 10 является низкая помехоустойчивость, поскольку в нем не учитывается апостериорная информация об амплитуде символов аналогового сигнала на выходе приемника, 15 Наиболее близким к изобретению по технической сущности является устройство для приема и градиентного декодирования избыточных сигналов, содержащее квантователь сигналов первый вход которого является входом устройства, второй вход подключен к выходу хронизатора, выход квантователя сигналов соединен с входом аналого-цифрового преобразователя, выходы которого соединены с соответствующими входами первого блока памяти, выход первого блока памяти соединен с входами первого порогового блока, блока управления выдачей информации и вычислителя,го сумматора, выходы третьего и четвертого ключей соединены через соответствующие четвертый и пятый сум-,маторы с первым и вторым входамишестого сумматора, выходы третьегои шестого сумматоров соединены соответственно с первым и вторым входами вычитателя, первый вход преобразователя кода, объединенные вторыевходы первого и второго ключей,объединенные вторые входы третьегои четвертого ключей и второй входпреобразователя кода являются соответственно первым, вторым, третьими четвертым входами блока управлениявыдачей информации, выход вычитателя является выходом блока управле ния выдачей информации. 2выход первого порогового блока соединен с первым входом декодера и вторым входом вычитателя и через регистр - с первым входом сумматора, выход вычитателя подключен через последовательно соединенные второй блок памяти и блок сдвига к второ- му входу сумматора, выход сумматора соединен через второй пороговый блок с вторым входом декодера, выход декодера соединен с первым входом третьего блока памяти, первый, второй выходы и второй вход которого подключены соответственно к второму, третьему входам и к выходу блока управления выдачей информации, третий выход. третьего блока памяти является выходом устройства. Известное устройство обеспечивает высокую помехоустойчивость приема избыточных сигналов, дает возможность осуществлять прием в целом сложных сигналов на основе избыточных кодов 23. Недостатками известного устройства являются его сложность, обусловленная наличием блока сдвига и второго блока памяти, а также в случае использования. устройства в высокоскоростных системах передачи информации для работы блока сдвига тре1152 буется высокая тактовая частота, что снижает .надежность функционирования устройства.Цель изобретения - упрощение устройства за счет исключения второго блока памяти и блока сдвига.Указанная цель достигается тем, что в. устройстве для приема и градиентного декодирования избыточных сигналов, содержащем квантователь ,сигналов, первый вход которого является входом устройства, второй вход4подключен к первому выходу хронизатора, выход квантователя сигналов соединен с входом аналого-цифрового преобразователя, выходы которого соединены с соответствующими первыми входами первого блока памяти, выход первого блока памяти соединен с первыми входами первого порогового бло- щ ка; блока управления выдачей информации и вычитателя, выход первого порогового блока соединен с первым входом декодера и вторым входом вычитатепя, сумматор, выход которого сое динен с входом второго порогового блока,. выход декодера соединен с первым входом второго блока памяти, первый, второй выходы и второй вход которого подключены соответственно к второму, третьему входам и к выходу блока управления выдачей информациитретий выход второго блока памя,ти является. выходом устройства, выход первого блока памяти и выход вы-. читателя соединены соответственно с35 первым и вторым входами сумматора, выход второго порогового блока соединен с первым входом регистра, выход регистра соединен с вторым входом декодера, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый и двенадцатый выходы хронизатора соединены соответственно с третьим входом квантователя сигналов, с вторым, ,третьим входами первого блока памя;ти, с объединенными вторым входом первого порогового блока и третьими входами вычитателя и сумматора, с третьим входом декодера, с третьим, четвертью, пятым, шестью входами второго блока памяти, счетвертым входом блока управления выдачей информации и с вторым входом регистра.55Кроме того, квантователь сигналов содержит умножители, интеграторы, генератор опорных сигналов и выО 16 4читатель, первый и второй ироды .генератора опорных сигналов соедцнены с первыми вхоцами соответственнопервого и второго умножителей, выходы которых соединены с первымн входами соответственно первого и второго интеграторов, выходы первого ивторого интеграторов соединены соответственно с первым и вторым входами вычитателя, вторые входы первого и второго умножителей объединены и являются первым входом квантователя сигналов, вход генератора опорных сигналов является вторым входом квантователя сигналов, вторые входы первого и второго интеграторовобъединены и являются третьим входомквантователя сигналов, выход вычита-,1 теля является выходом квантователясигналов,При этом блок управления выдачей информации содержит ключи, сумматоры, вычитатель и преобразователь кода, выход преобразователя кода соединен с первыми входами первого, второго, третьего и четвертого ключей, выходы первого и второго ключей соединены через соответствующие первый и второй сумматоры с первым и вторым входами третьего сумматора, выходы третьего и четвертого ключей соединены через соответствующие четвертый и пятый сумматоры с первым"и вторым .входами шестого сумматора, выходы третьего и шестого сумматоров соединены соответственно с первым и вторым входами вычитателя, первый вход преобразователя кода, объединенные вторые входы первого и второго ключей, объединенные вторые входы третьего и четвертого ключей и второй вход преобразователя кода являются соответствен" но первым вторым, третьим и четвертым входами блока управления выдачей информации, выход вычитателя является выходом блока управления выдачей информации.На фиг. 1 представлена структурная схема устройства для приема и обработки избыточных сигналов,. на фиг. 2 - структурная схема хронизатора, на фиг. 3 - геометрическое изображение алгоритма работы предлагаемого устройства.Устройство для приема и градиентного декодирования избыточных сигналов (фиг1) содержит квантователь1 сигналов, вьпюлненньпЪ на умножителях 2 и 3, интеграторах 4 и 5,генераторе 6 опорных сигналов,и вычитателе 7, аналого-цифровой преобра-зователь 8, выполненный на пороговых элементах 9, элементах 10 НЕ,элементах 11, шифраторе 12, аттенюаторах 13 и источнике 14 пороговыхнапряжений, блок 15 памяти, выполненный на регистрах 16 и ключе 17,пороговый блок 18, выполненный нарегистре 19 сдвига и ключе 20, вычитатель 21, выполненный на двоичнодесятичных преобразователях 22 и 23кода и элементе 24 вычитания, сумматор 25, выполненный на двоично-десятичном преобразователе 26 кода иэлементе 27 сложения, пороговыйблок 28, выполненный.на источнике29 порогового напряжения, аттенюаторе 30 и пороговом элементе 31, регистр 32 сдвига, декодер 33 и 34блок 35 памяти, выполненный на элементе 36 ИЛИ, триггере 37, регистрах38 и 39 сдвига, ключах 40-43 н элементе 44 ИЛИ, блок 45 управлениявьдачей информации, выполненный наключах 46-49, сумматорах 50-55,двоично-десятичном преобразователе56 кода и вычитателе 57, и хрониза- щтор 58,Хронизатор 58 (Фиг, 2) содержитФормирователь 59 импульсов, элементы60-67 задержки, элемент.68 ИПИ, формирователи 69-74 тактовых импульсов,каждый из которых выполнен на триггере 75, счетчике 76 и генераторе 77тактовых импульсов, элементы 78 - .80 ИЛИ иделители 81 и 82 частотына три. 40Устройство работает следующим образом,Рассмотрим алгоритм Функционирования предлагаемого устройства.Пусть осуществляется формирование 45 составного сигнала с избыточностью на основе комбинаций двоичного трехзначного кода с иинимальнъщ кодовым расстоянием 4 = 3, для которого разрешенными кодовыми комбинациями являются Х 1 = 101 и Х,= 010. Составной избыточный сигнал после прохождения канала связи, в котором на него воздействуют помехи, с помощью квантователя 1 сигналов преобразуют в .аналоговый сигнал.На фиг. 3 в виде куба изображено Множество сигнальных точек, соотввтствующих аналоговым сигналам Х навыходе. квантователя 1 сигнапов.Вершины куба соответствуют кодовымкомбинациям. Каждое ребро куба определяет единичное хэммингово расстояние между теми вершинами (кодовымикомбинациями), которые данное ребросоединяет,На фиг. 3 а штриховкой вьделенаобласть сигнальных точек, которыеотождествляются с разрешенной кодовой комбинацией Х, при посимвольномприеме; на.фиг. Зд- то же, при приеме в целом.Соответственно для разрешенной кодовой комбинации Х, ,на Фиг.,Зб штриховкой выделена область сигнальныхточек, отождествляемых с даннойкомбинацией при посюлвольном приеме,"па фиг. Зг - то же, при приеме вцелом.Из сравнения фиг. 3 а с 3 в ифиг. 3 б с 3 г следует, что отличиепосимвольного приема от приема вцелом заключается в отличии границобластей отождествления.Совместим области отождествленияпри посимвольном приеме и при приемев целом для комбинации Х и рассмотрим переднюю грань (квадрат) Х 1-3, --3 -Х 4 куба, Множество сигнальныхзточек Х -Х -4-2-3-34 на этой грани-.отождествляются с Х л при посимвольном.приеме. Множество сигнальныхточек Х-Хз -4-3-Х на передней грани куба отождествляются с Х 1 приприеме в целом,.Отличие приема в целом от посимвольного приема, в частности,состоит в наличии сигнальных точек,принадлежащих треугольнику 1-4-3,Характерной особенностью сигнальныхточек данной области является то,что при посимвольном приеме ониотождествляются с разрешенной комбинацией Х так как она принадлежит заштрихованной области нафиг. Зб. В случае приема в целомсигнальные точки из треугольника2-4-3 отождествляются с разрешеннойкодовой комбинацией Х 1. Геометрические модели достаточно точно иллюстрируют существо отпичия алгоритмапосимвольной обработки составныхсигналов с избыточностью, формируе.мых на основе кодов произвольнойзначимости, от алгоритма приема вцелом,115201 б 7В общем случае также существуют такие области сигнальных точек, которые при приеме в целом правильно отождествляются с разрешенными кодовыми комбинациями, а при посимволь ном приеме - ошибочно, Но в отношении этих областей можно отметить, что их сигнальные точки отождествляются с ближайшей к истинной (с вероятностью правильного приема при обработке в целом) разрешенной кодовой комбинацией. Это утверждение находится в полном соответствии с моделью на фиг, 3 д.Принцип действия известного уст ройства заключается в том, что сигнальные точки из треугольника 2-4-3 "вбрасываются" в область посимвольйого приема для Х 1. Осуществляется указанное "вбрасывание" следующим 20 образом,.Посимвольный прием предполагает. осуществление трех основных операций.Первая операция называется анало говой демодуляцией. Она реализуется в квантователе 1 сигналов. Вторая операция - однопороговое квантование .и реализуется с помощью аналого-циФрового преобразователя 8. ЗОНа фиг. Зд с помощью указанных операций сигнальные точки квадрата Х 1-1-2-5 отождествляются с двоичной кодовой комбинацией (в данном слу,чае разрешенной) Х 1, Сигнальные3 точки квадрата Хэ -4-2-1 соответственно с двоичной кодовой комбинацией Х, а сигнальные точки квадратов Х - 3-2-4 и Х. - 5-2-3 соответст.венно отождествляются с Х и Х, 40Третья операция называется декодированием. С ее помощью двоичные кодо. вые комбинации по соответствующему критерию отождествляются с разрешенными двоичными кодовыми комбинация ми, Данная операция реализуется с помощью декодера 33. Например, в результате выполнения операции декодирования в соответствии с критерием Максимального правдоподобия с разрешенной комбинацией Х 1 (фигЗд)отОждеСтвляются комбинации Х и Х 4,Комбинация Х отождествляется с разрешенной кодовой комбинацией Х 2,, Согласно градиентному декодирова-, 5 нию в,я -мерном пространстве вычисляют вектор ХХ, считая при этом,что сигнальная точка Х попала в треугольник 2-4-3, Для этого вычисляютразность между вектором ОХ и ОХ(точка О - условное изображение начала координат и -мерного прсэстранства). Результат - вектор Х Х усиливают до тех пор, пока его,конецне попадет в область посимвольногоприема для Х (фиг, За).В блоке 35 памяти осуществляетсянакопление составляющих сигнала Х .Х,который с помощью блока сдвига усйливают в указанном направлении дозаданной величины.Из выводов структурного анализаи из геометрических моделей (фиг Зд)следует, что для любой сигнальнойточки Х из треугольника 2-4-3.(заисключением линии - границы треугольника, для которой вероятность совпадения с сигнальной точкой близка к.нулю (расстояние до линии 4-3 меньшерасстояния до Х ). Из этого следует,что при увеличении величины сигнала ХХ в два раза конец вектора 2 ХХбудет попадать в область Х -Х -4-2 з-3-Х 4 посимвольного приема для Х 4.Решение при этом будет ошибочнымтолько в том случае, если сигнальнаяточка Х будет принадлежать линии4-3, как и при приеме в целомИз данного факта вытекает, чтоосновное преимущество алгоритма функционирования известного устройстваопределяемое расширением областипосимвольного приема до величиныобласти приема в целом и в предлагаемом устройстве сохраняется. Отличиезаключается в том, что вектор Хс Хвсегда усиливают в два раза. Теоретически данная операция вытекает изметода теории оптимизации, использующего вторые производные, и квадратичной целевой функции.В предлагаемом устройстве достаточно покоординатно, т.е. посимволь-.;но к радиусу-вектору ОХ сигнальнойточки Х прибавить вектор ХХ, который следует выбрать равным и повеличине и по направлению ХХ, Получаемый в результате вектор сигнальчнои точки Х после посимвольной,обработки приводит к Хс,В остальном алгоритм функциониро" вания.предлагаемого. устройства не отличается от алгоритма функционирования известного устройства, т,е. для устранения йеопределенности от. - носительно того попала сигнальнаяи первую комбинацию соответственново второй и третий регистры 16 и т.д.В соответствии с управляющими сигналами из хронизатора 58 блок 15,может функционировать в двух режимах считывания: с регенерацией ибез регенерации, при котором в момент считывания ключ 17 закрывается,По окончании второго режима считывания блок 15 памяти готов к обработке следующих сигналов,Пороговый блок 18 преобразуетвходные двоичные -разрядные коДОвые комбинации в одну из двух выходных 1 -разрядных кодовых комбинаций; нулевую или единичную. Онсоцержит ключ 20 и 1 -разрядныйдвоичный регистр 19 сдвига. Так каквход последнего соединен с его же2 Овыходом, то регистр 19 представляетсобой генератор двоичных сигналов"1", т.е, в его ячейки всегда записаны " 1". На двоичный регистр 19подаются импульсы считывания синхронно с импульсами первого считыванияиз блока 15. Следовательно в соответствующие моменты времени на информационный вход ключа 20 будутпоступать двоичные символы "1", . ЗОНа управляющий вход ключа 20 свыхода блока 15 памяти старшими разрядами вперед последовательно поступаютТ -разрядные двоичные комбинации. Старший разряд каждой такой 35комбинации управляет состояниемключа 20. При этом указанное состояние сохраняется на время считывания остальных разрядов, следующих после старшего. Пусть, например, о.в первой 3 -разрядной двоичной комбинации старший разряд - единичный.Тогда ключ 20 своего открытого висходном состоянии положения не изменяет и пропускает на выход порого. вого блока 18 1 -разрядную единичную двоичную кодовую комбинацию.Пусть во второй, следующей за первой, двоичной комбинации старшийразряд - нулевой. В этом случае 50ключ 20 закрывается на время у тактов, после чего опять Открывается,и т.д. Очевидно, что во втором примере на выходе блока 18 будет присутствовать нулевая 1 -разрядная 55двоичная кодовая комбинация. Такимобразом, входные кодовые комбинации пороговый блок 18 преобразует в зависимости от состояния их старшего разряда или в единичную,или внулевую выходные двоичные кодовыекомбинации.Вычитатель 21 предназначен длявычитания из величины, представленной в двоичном коде соответствующейвыходной комбинации блока 15 памяти,величины, представленнойсоответст- .вующей двоичной кодовой комбинациейна выходе блока 18. Перед преобразованием двоичные коды с помощьЮ преобразователей 22 и 23 представляютсяв двоично-десятичной системе счисления, в которой с помощью элемента24 вычитания осуществляется вычисление разности указанных величин.Сумматор суммирует выходной сигнал вычитателя 21 с выходным сигналом блока 15. Для этого выходнойсигнал блока 15 памяти с помощью,.преобразователя 26 представляется вдвоично-десятичной систЕме счисленияи подается на вход элемента 27сложения,Пороговый блок 28 преобразует входной сигнал в один из сигналов 0 илип - 1, Источник 29 и аттенюатор 30 формируют ОпорньЗЙ импульС постоян ного тока, амплитуда которого равна В/2. Если входной сигнал по амплитуде не меньше величины порогового напряжения, то на выходе блока 28 формируется сигнал у - 1. В противном случае - сигнал О.Декодер 33 отождествляет входные двоичные кодовые комбинации с выходными разрешенными кодовыми комбинациями.Блок 35 памяти предназначен для хранения двух разрешенных кодовых комбинаций, выдачи их в блок 45 и считывания одной из них на выход устройства. В соответствующие моменты времени на регистры 38 и 39 па" даются импульсы записи. С их помощью первая выходная двоичная кодовая комбинация декодера 33 через элемент 36 ИЛИ записывается в регистр 38. Потом вторая выходная комбинация декодера 33 записывается в. регистр 38, сдвигая первую комбинацию в регистр 39, Далее по сигналу от хронизатора 58 открывается ключ 40, а на регистры 38.и 39 подаются импульсы считываний. Содержимое регистра 38 считывается на соответствующий выход блока 35 и одновременно пере 1152016 1440 45 50 55 писывается в регистр 39. Содержимое этого регистра 39 выдается на выход блока 35 и через открытый в это вре-. мя ключ 40 переписывается в регистр ,38, После этого ключ 40 закрывается.В определенный момент времени на счетный вход триггера 37 подается сигнал. Если он единичный, то триггер 37 меняет свое состояние, если нулевой, то триггер 37 своего состояния не меняет. В это же время откры" вается ключ 41, Если состояние триггера 37 является нулевым, то открывается ключ 42, в противном случае - ключ 43. После этого на регистры 38 и 39 подаются импульсы считывания и на выход устройства через ключ 42, или через ключ 43 и элемент 44 ИЛИ.считывается одна из разрешенных кодовых комбинаций, Триггер 37 устанавливается в исходное состояниеРегистры 38 и 39 сбрасываются по сигналу "Общий сброс", Формируемому в хронизаторе 58.Блок 45 управления выдачей инФормации предназначен для вычисления степени близости (коэффициента корреляции) между двоичной кодовой комбинацией блока 15 памяти и разрешенными кодовыми комбинациями блока 35 памяти, а также для Формирования управляющего сигнала для блока 35, В момент времени, определяемый унравляюьцими сигналами хронизатора, на один вход блока 45 подается двоичная кодовая комбинация блока 15 памяти, на другие - разре" шенные двоичные кодовые комбинации от блока 35. С помощью преобразователя 56 входная двоичная кодовая комбинация преобразуется в двоична-десятичную, Этот сигнал подается на входы ключей 46-49, одновременно с соответствующими символами разрешенных комбинаций. Последние коммутируют ключи 46-49. При этом двоична-десятичные символы, через соответствующий ,ключ 46 или 41, а также 48 или 49 поступают на соответствующие сумматоры 50-53. Выходные сигналы сумматоров 50 и 52 - положительные, а выходные сигналы сумматоров 51 и 53 " отрицательные, На выходе сумматора 54 после считывания всех символов указанных комбинацйй формируется сигнал, соответствующий степени близости между составным сигналом блока 15 и второй разрешейной комбинацией. Соответственно выходнойсигнал сумматора 55 определяет степень близости между составным сигналом и первой разрешенной комбинацией. Сигналы сумматоров 54 и 55 вычитаются в вычитателе 57. Положительный выходной сигнал вычитателя 57служит для блока 35 в качестве единичного управлякпцего состоянием .триггера 37 сигнала, а отрицательный сигнал - соответствейно в качестве нулевого управляющего сигнала, Обнуляются сумматоры 50-55 по сигналу "Общий сброс" из хронизатора 58.Регистр 32 сдвига предназначен для хранения выходной двоичной кодовой комбинации блока 28 на время, в течение которого в декодере 33 осуществляется преобразование выход- ной двоичной комбинации блока 18. Сигналы записи и считывания подаются с соответствующего выхода хронизатара 58.В хронизаторе 58 с помощью Формирователя. 59 импульсов осуществляется тактовая и блочная синхронизация. Формирователя тактовых импульсов содержат триггеры 75, разрешающие работу генераторов 77 импульсов определенной частоты следования, Сопряжение соответствующих входов блоков устройства и управляющих сигналов, Формируемых .в различные моменты времени, осуществляется с помощью элементов 68, 78 - 80 ИЛИ..В качестве примера, поясняющего алгоритм Функционирования предлагае" мого устройства, рассмотрим его работу при следующих параметрах. Пусть на передающей стороне составной сигнал с избыточностью сформирован на основе двоичной кодовой комбинации У = (0110101). Если бы в канале связи. не было помех, то на выходе преобразователя при количесФве зон квантования, равных Я, была сформирована следующая совокупность трехзначных двоичных кодовых комбинаций: 000, 111, 111, 000, 111, 000, 111Эта совокупность. определяет сигнал - точную оценку избыточного. сигнала.Характеристики кода следующие: длина кодовой комбинации й = 7, количество информационных символов К = 3, минимальное ходовое расстоя.ние 3 = 4 (следовательно, кратность1520 двоичных ошибок, исправляемых декодером 9, равна= 1). Используемыйкод состоит из следующих разрешенных,кодовых комбинаций: 0000000, 0011011,0101110, 0110101, 1001101, 1010110, 51100011, 1111000,Сложный избыточный сигнал, искакенный в канале связи помехами, спомощью квантователя 1 преобразуетсяв совокупность импульсов с различной амплитудой. Величина амплитудыкаждого такого импульса с помощьюпреобразователя 8 преобразуется вЧ = 3-значную двоичную кодовую комбинацию. Совокупность из 1 таких 15комбинаций запоминается в блоке 15памяти и соответствует сигнальнойточке Х (Фиг, 3 д). Пусть указаннаясовокупность (сигнал Х) имеет вид:.,Х = (100, 010, 011, 000, 111, 000,111) .Посимвольная обработка составногосигнала Х в блоке 18 после его записи и считывания с регенерацией,из блока 15 приводит к сигналу1(Фиг. 3 д) Х = (111, 000, 000, 000,11 1, 000, 111). Двоичный составнойсигнал Х -подается в декодер 33,в котором отождествляется с ближайшей разрешенной кодовой комбинацией(Фиг. Зд) Х - (7007707). Символыэтой комбинации на выходе декодера33 представляются импульсами постоянного тока с амплитудами, определяемыми величинами проекций сигналаХ 2 - соответственно они равны УВ,ОВ, ОВ, 7 В, 7 В, ОВ, 7 В, Сигнал Х, запоминаетея в регистре 38 блока 35.Одновременно с комбинацией Х поступаетна вход вычитателя 21, Навйходе последнего образуется сигнал(Фиг. Зд) ХХ = Х - Х = (-3, 2, 3,О, О, О, О), который в сумматоре25 суммируют с сигналом Х. В результате послучают сигнал Х= 1, 4, 6,(ЦО, 7, О, 7. Его с помощью блока 8,преобразуют в двоичный сигнал Х,- (О, 7, 7, О, У, О, 7), которыйв данном примере оказывается равным 6.6сигналу Х, т.е. Х, есть Х 1. Элементарные сигналы, входящие в состав Х 1, накапливаясь, запоминаются в регистре 32 сдвига. В соответствующий момент времени сигнал считывается из регистра 32 в декодер 33, в котором отождествляется с ближайшей разрешенной двоичной кодовой комбинацией, но так как Х и является, разрешенной комбинацией, то второй выходной разрешенной двоичной кодо вой комбинацией на выходе декодера 33 будет являться Х= 3 . Она, как и первая, запоминается в блоке 35.После этого разрешенные комбинации Х, и Х из блока 35 и комбинация Х из блока 15 подаются в блок 45, где вычисляются степени близости между Х и Х 1 (соответствующий коэФФициент корреляции равен 17) и . между. Х и Х (коэФФициент корреляции равен 13). На основе анализа разности степеней близости из блока 35 на выход устройства считывают разрешенную двоичную кодовую комбинацию Х. Подается сигнал "Общий сброс" и устройство готово к обработке следующего составного избыточного сигнала. Полученньп результат тот же, что и получаемьпЪ с помощью известного устройства, но достигается он алгоритмически значйтельно проще.Предлагаемое устройство для гра-, диентного декодирования в целом двоичных избыточных кодов обладает более высокими технико-экономическими показателями по сравнению с известньщ.Техническое преимущество предлагаемого устройства заключается в том, что в нем отсутствуют два бло- .ка: блок памяти и блок сдвига, обуславливающие большое количество операций при Формировании второй грубой оценки (сигнала Х) составного избыточного сигнала. Последнее при- водит к уменьшению времени выполне- ния элементарных операций.

СмотретьЗаявка

3665753, 24.11.1983

СТАВРОПОЛЬСКОЕ ВЫСШЕЕ ВОЕННОЕ ИНЖЕНЕРНОЕ УЧИЛИЩЕ СВЯЗИ ИМ. 60-ЛЕТИЯ ВЕЛИКОГО ОКТЯБРЯ

ЗУБКОВ ЮРИЙ ПЕТРОВИЧ, КОЖУХОВ ОЛЕГ ИВАНОВИЧ

МПК / Метки

МПК: G08C 19/28

Метки: градиентного, декодирования, избыточных, приема, сигналов

Опубликовано: 23.04.1985

Код ссылки

<a href="https://patents.su/12-1152016-ustrojjstvo-dlya-priema-i-gradientnogo-dekodirovaniya-izbytochnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для приема и градиентного декодирования избыточных сигналов</a>

Предыдущий патент: Система телемеханики

Следующий патент: Устройство для приема и обработки избыточных сигналов

Случайный патент: 314525